用基于AXI的RTL DUT替换行为DUT在UVM测试台中

此示例显示了如何从简单的行为DUT接口移动到使用AXI Lite和AXI流总线协议的RTL DUT接口。几个UVM组件必须更改如驱动程序和监视器,但原始测试台结构和序列和记分牌组件可以在不修改的情况下重复使用。

介绍

看到这个例子从Simulink生成参数化UVM测试替补万博1manbetx用于描述设计和背景技术的设计和背景。要为此示例执行默认测试坐标执行:

%生成UVM测试台设计='prm_uvmtb / pulsedetector'序列='prm_uvmtb / genpulse'记分牌='prm_uvmtb / checkdetection'UVMBuild(设计,序列,记分牌)

Simulink中的D万博1manbetxUT表示脉冲检测器的功能行为,并且不使用典型的HDL IP核心的任何硬件协议接口。UVM测试台使用Simulink设计作为实际HDL实现的万博1manbetx待机。验证工作流程中的下一步集成了使用基于AXI的协议的实际HDL实现,进入同一生成的UVM测试台。

要使用RTL DUT,必须替换UVM测试台的碎片,如蓝色所示:

将端口映射到AXI接口

对于这个rtl dut,COEFF.端口映射到处理器接口,AXI4-Lite,data_in.端口映射到AXI4流从接口,以及data_out.端口映射到AXI4流主界面,如下所示。

您可以手动编写此RTL或使用HDL编码器的IP核心生成工作流以创建它。该模型具有一种变体算法,可以使用HDL编码器产品生成HDL IP核心。

模拟Simulink中的HDL变量万博1manbetx

使用此变体执行模拟:

%模拟RTL可变算法变体set_param('prm_uvmtb / pulsedetector'那'LabelModeaconciveChoice'那'hdl')set_param('prm_uvmtb / checkdetection / whecialsdelay'那'LabelModeaconciveChoice'那'帧延迟')sim('prm_uvmtb')

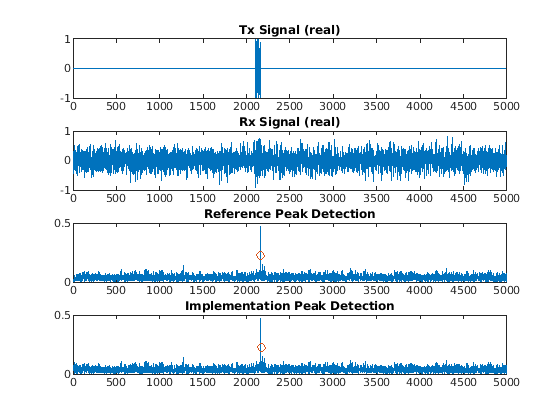

[Framenum = 0]在REF或iclim中没有发现峰值。[Framenum = 1]峰值位置= 2163.000000,使用全局最大值= 0.280使用来自iclic = 2170错误(abs)= 7 [framenum = 1]峰值从impl = 0.280,错误(ABS)= 0.000误差(PCT)= 0.017 [FRAMENUM = 2]峰值位置= 2163.000000,使用从iclic = 2170错误(ABS)= 7 [FRAMENUM = 2的峰值使用全局最大[FRAMENUM = 2]峰值峰值]从iclic = 0.199,错误(ABS)= 0.000误差(PCT)= 0.190 [framenum = 3]峰值位置= 2163.000000,使用全局最大值[framenum = 3]峰值检测到的mag-squared = 0.2242170错误(ABS)= 7 [framenum = 3]峰值从iclic = 0.223,误差(abs)= 0.000误差(pct)= 0.183 [framenum = 4]峰值位置= 2163.000000,Mag-Squared = 0.200使用全局从iclic = 2170错误(abs)= 7 [framenum = 4]峰值从iclic = 0.200,误差(abs)= 0.000误差(pct)= 0.043 [framenum = 5]峰值位置= 2163.000000,使用来自iclic = 2170错误(abs)= 7 [framenum = 5的Framenum = 5]峰值使用全局最大值[Framenum = 5]峰值峰值= 0.255]峰值从iclic = 0.255,误差(ABS)= 0.000误差(PCT)= 0.031 [Framenum = 6]峰值位置= 2163.000000,使用来自iclic =检测到的全局最大[framenum = 6]峰值的Mag-Squared = 0.2412170错误(ABS)= 7 [Framenum = 6]峰值从iclic = 0.241峰值,误差(ABS)= 0.000误差(PCT)= 0.187 [Framenum = 7]峰值位置= 2163.000000,Mag-Squared = 0.241使用全局从iclic = 2170错误(abs)= 7 [framenum = 7]峰值从iclic = 0.241,误差(abs)= 0.000误差(pct)= 0.019 [framenum = 8]峰值位置= 2163.000000,使用来自iclic = 2170错误(abs)= 7 [framenum = 8]峰值从iclic = 0.225,错误(abs)= 0.000 = 0.000 = 0.000 = 0.000误差的峰值= 0.225(PCT)= 0.032 [FRAMENUM = 9]峰值位置= 2163.000000,使用从iclic = 2170错误(ABS)= 7 [FRAMENUM = 9]峰值的峰值= 2163.000000,使用全局MAX [FRAMENUM = 9]峰值impl = 0.239,错误(ABS)= 0.001误差(PCT)= 0.241 [Framenum = 10]峰值位置= 2163.000000,使用全局M = 2163.000000,Mag-Squared = 0.225AX [Framenum = 10]从Impl = 2170错误(ABS)= 7 [Framenum = 10]峰值从Accl = 0.225,误差(ABS)= 0.000误差(PCT)= 0.146

生成HDL.

如果您有HDL编码器,则可以设置工具路径并为此变体生成RTL。例如,要创建Xilinx Vivado兼容IP,请插入工具路径并执行以下操作:

%生成基于AXI的RTL HDL IP(需要HDL编码器)hdl setuptoolpath('toolname'那'Xilinx Vivado'那'工具路径'那'/tools/vivado/2018.3/bin/vivado')prm_uvmtb_hdlworkflow.

这将使结果的HDL IP文件将结果的HDL IP文件放入HDL_PRJ / HDLSRC / PRM_UVMTB中。但是,RTL实现已被包含在覆盖overrides_AXIDUT / AXIIVESOURCE中的此演示中,因此不需要HDL编码器许可证。

覆盖必要的UVM组件

替换原始DUT的UVM文件位于覆盖_AXIDUT中。没有必要修改原始文件中的任何生成文件UVMBuild.调用。

mw_pulsedetector_axirtl_if.sv.:重新定义主DUT接口类。比较原始接口定义。

mw_pulsedetector_axirtl_driver.sv.:根据DUT接口的AXI协议驱动输入事务。比较原来的驾驶员。

mw_pulsedetector_axirtl_monitor / monitor_input.sv.:接收流式AXI数据并将其转换为与以前相同的交易类型。比较原始监视器定义。

mw_pulsedetector_axirtl_top.sv.:实例化AXI RTL DUT并包括主UVM封装。比较原始顶级定义。

模拟UVM测试台

使用新的RTL DUT执行测试台,以验证UVM执行是否匹配Simulink执行。万博1manbetx由于序列用SNR输入端口参数化,因此其默认值将在UVM中为0.0。为了正确比较模拟运行,我们需要将其默认值更改为2.0(具有0b10_000000的比特值),以匹配Simulink;万博1manbetx这可以通过PlueRG完成,我们通过环境变量传递给脚本。

我们有许多新的RTL文件来编译,我们必须覆盖顶级设计单元。我们通过环境变量将这些更新传递给脚本。

%清除环境变量,影响UVM模拟setenv.extra_uvm_sim_args.;setenv.extra_uvm_comp_args.;setenv.uvm_top_module.;%使用AXI RTL DUT模拟UVM测试台光盘prm_uvmtb_uvmbuild / uvm_testbench / topsetenv.extra_uvm_comp_args.'-f ../../../overrides_axidut/extra_comp_args.f'setenv.extra_uvm_sim_args.'+ snr_default_inp_val = 10000000 + uvm_testname = mw_pulsedetector_axirtl_test'setenv.uvm_top_module.mw_pulsedetector_axirtl_top.!!vsim -do run_tb_mq.do%modelsim / questasim(gui)!!vsim -c -do run_tb_mq.do%modelsim / questasim(控制台)!!./run_tb_incisive.sh%incisive(控制台)!!./run_tb_xcelium.sh%xcelium(控制台)!!./run_tb_vcs.sh%VCS(控制台)光盘../../ ..

仿真日志和波形片段如下所示。请注意,日志显示与之前的相同结果,5个检测脉冲。但是,还注意到波形显示不同的时机,以便锻炼设计。对于每个5000个信号样本的每个帧而不是始终始终有效数据流,而是通过处理器接口编程64系数,然后流动5000个样本。

结论和下一步

此示例显示了在Simulink中开发的设计和测试工作台如何用于生成完全可执行的UVM测试台。万博1manbetx这UVMBuild.命令可自动化关键组件的生成,编译和集成到UVM框架中。

HDL验证工程师可以从Simulink中确认总体覆盖范围,并使用自己的本机UVM序列库增强覆盖范围。万博1manbetx

它们还可以使用Simulink使用Simulink替代行为设计,RTL设计以AXI4等硬件协议包装,万博1manbetx没有更改原始序列发生器和响应检查。