进程间数据通信通过专用的努力ware Peripheral

A variety of microcontroller units (MCUs) and SoCs provide dedicated hardware peripherals to enable processes executing on separate processors to communicate. The dedicated hardware connection eliminates the need to develop conventional channels through shared memory or through peripheral buses. Dedicated interprocess data communication in hardware is used in embedded MCUs that either support or do not support an operating system (OS). Without an OS, the process occupies the entirety of the processor resources. In this case, multiprocess systems require distribution across multiple processors within the single MCU. For example, the F2838xD family of processors from Texas Instruments™ contains a pair of interprocessor communication (IPC) peripherals that directly connect the C28 CPUs. For more information on the F2838xD processors and their IPC peripherals, see the Texas Instruments websiteTMS320F2838x Microcontrollers with Connectivity Manager.

The SoC Blockset™Interprocess Data Read,Interprocess Data Channel, andInterprocess Data Writeblocks simulate communication between bare metal processes executing on separate processors. To create a monodirection data channel between two processors, add anInterprocess Data Writeblock into the processor reference model that sends data. Next, add anInterprocess Data Readblock into the processor reference model that receives data. In each model, expose the event ports to the top-level model using theOutportandInportblocks, respectively. Finally, connect the event ports in the top-level model using theInterprocess Data Channelblock.

If the SoC models are built for a supported processor, such as those in the F2838xD family of processors, code is automatically generated for the hardware IPC peripherals.

One Way Interprocess Communication

This example shows one-way interprocess data communication between two bare metal processors.

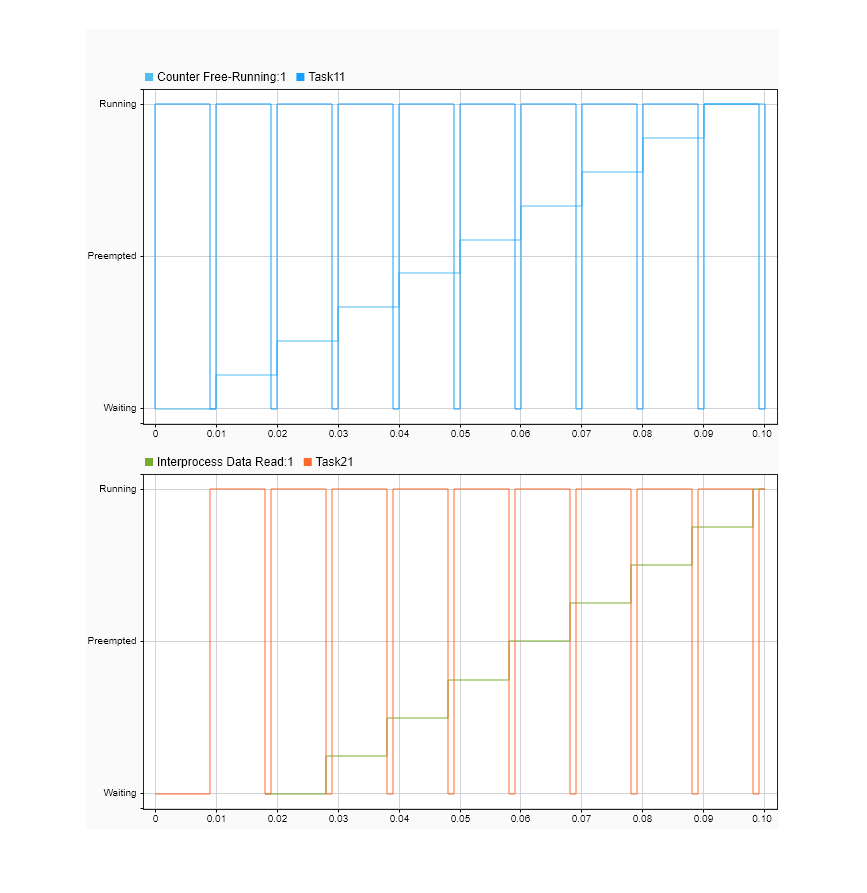

An algorithm in Processor1 sends a data message, using the Interprocess Data Write block, to the Interprocess Data Channel block at a 0.01 second interval. Processor2 two receives and processes the data messages asynchronously, using the Interprocess Data Read block.

Results

In the Simulation tab, click Run. When the simulation completes, open the Simulation Data Inspector to view the resulting signals and tasks. From the graphs, Processor1 sends the data value at the completion of the first task, Task11, instance. The data then gets received by Processor2, triggering the event driven task, Task21. At the completion of Task21 instance, the final value gets emmitted in Processor2, potentially for additional processing by other tasks.

See Also

Interprocess Data Read|Interprocess Data Channel|Interprocess Data Write|Task Manager