设计和计算简单的锁相环模型

这个例子展示了如何设计一个简单的锁相环(PLL)使用参考体系结构和验证使用锁相环Testbench。

锁相环频率合成器系统产生一个输出信号的相位取决于输入信号的相位。在最简单的形式,一个锁相环由一个阶段/频率检测器(PFD),电荷泵、环路滤波器、压控振荡器(VCO),和一个时钟分频器反馈循环。PFD和电荷泵在一起产生一个误差信号正比于它的两个输入信号的相位差。循环过滤去除误差信号的高频成分,使VCO。VCO的输出是美联储通过PFD的时钟分频器的输入,产生一个负面的反馈循环。

混合信号Blockset™提供了参考体系结构来设计一个简单的锁相环模型和testbenches验证符合设计规范的设计模型。

设置锁相环Testbench模型

打开模型simplePLL这个例子作为支持文件。万博1manbetx模型由一个整数N与单一模量预定标器块和锁相环锁相环Testbench块。

open_system (“simplePLL.slx”)

锁相环规格和障碍

使用的数据表Skyworks SKY73134-11设计锁相环系统锁定在2.8 GHz。

双击整数N与单一模量预定标器锁相环块打开参数对话框并验证这些设置:

检查的障碍被禁用PFD和电荷泵选项卡。

在电荷泵选项卡,输出电流被设置为

2.7马。的死区补偿和输入阈值参数保持默认值。

在VCO选项卡,VCO的敏感性被设置为

20.MHz / V。的免费的运行频率略低于目标锁定频率和设置2.78GHz。的相位噪声频率偏移被设置为[100年e3 1 e6 3 e6 10 e6)赫兹和相位噪声水平(dBc / Hz)被设置为145 (108−134−−−154]dBc / Hz。

考虑到参考输入频率锁相环

1.6兆赫,时钟分频器的价值和时钟分频器最小值在预定标器选项卡设置 。

。

在循环过滤选项卡,环路带宽被设置为

160年kHz,为参考输入的频率。相缘是保存在默认45度。过滤器组件值自动计算。

在分析选项卡,开环的分析和闭环分析阴谋被选中。

情节Presimulation锁相环循环动力学

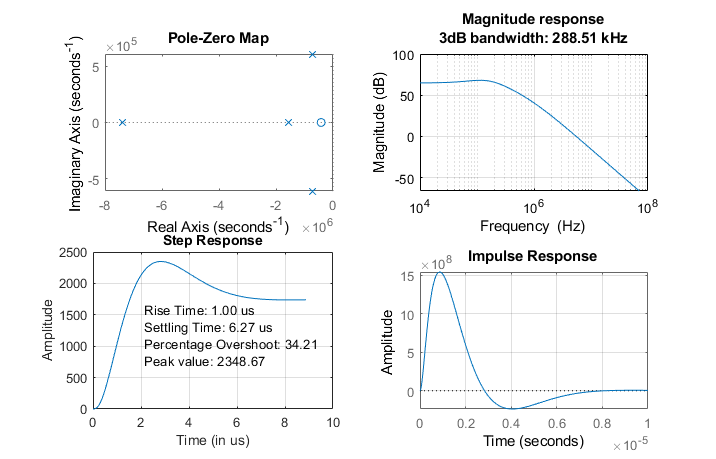

单击情节循环动力学按钮查看presimulation结果和aseess的稳定系统。

闭环分析包括Pole-Zero地图、级响应、阶跃响应、脉冲响应。系统的3-dB带宽288.51kHz。系统是稳定的。

开环分析由锁相环系统的伯德图。这个阶段是44.1度和单位增益频率159.9kHz。

修改锁相环Testbench相位噪声的测量

双击该锁相环Testbench打开参数对话框和验证这些设置:

在刺激选项卡中,输入信号的锁相环被定义为一个方波

1.6MHz。

在设置选项卡,检查相位噪声测量选项被选中。操作的频率和锁定时间测量选项去掉的时候。设置分辨率带宽来

50kHz,不。谱平均来4,推迟时间来1.5 e-5年代,相位噪声频率偏移来[100年e3 1 e6 3 e6 10 e6)赫兹。

在目标指标选项卡,设置相位噪声(dBc / Hz)来

145 (108−134−−−154],一样的锁相环相位噪声。

情节锁相环相位噪声

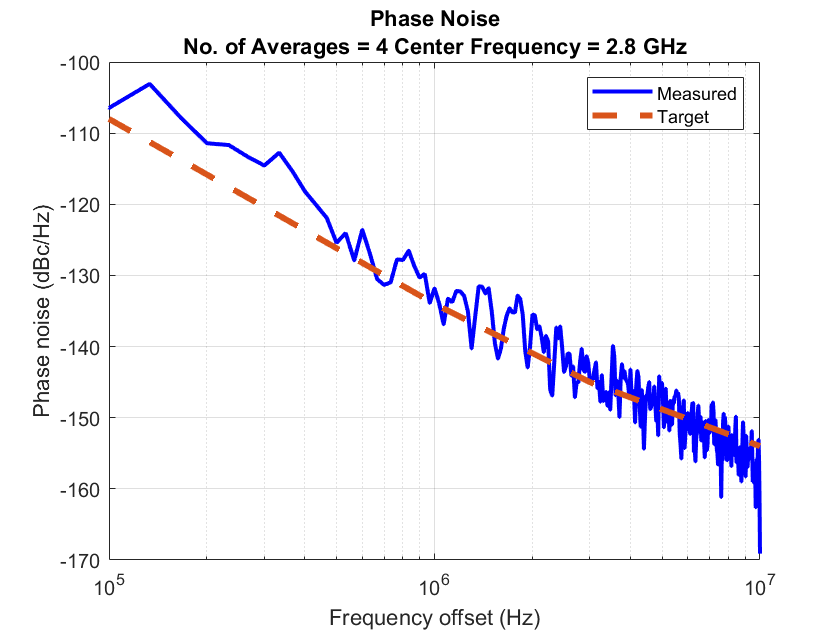

运行仿真1.35的军医年代。仿真结果显示图标的锁相环Testbench。在特定频率偏移测量相位噪声水平与目标相一致的价值观。

双击锁相环Testbench块打开参数对话框。单击情节相位噪声剖面按钮。锁相环操作频率2.8GHz,测量相位噪声轮廓匹配目标概要文件。