主要内容

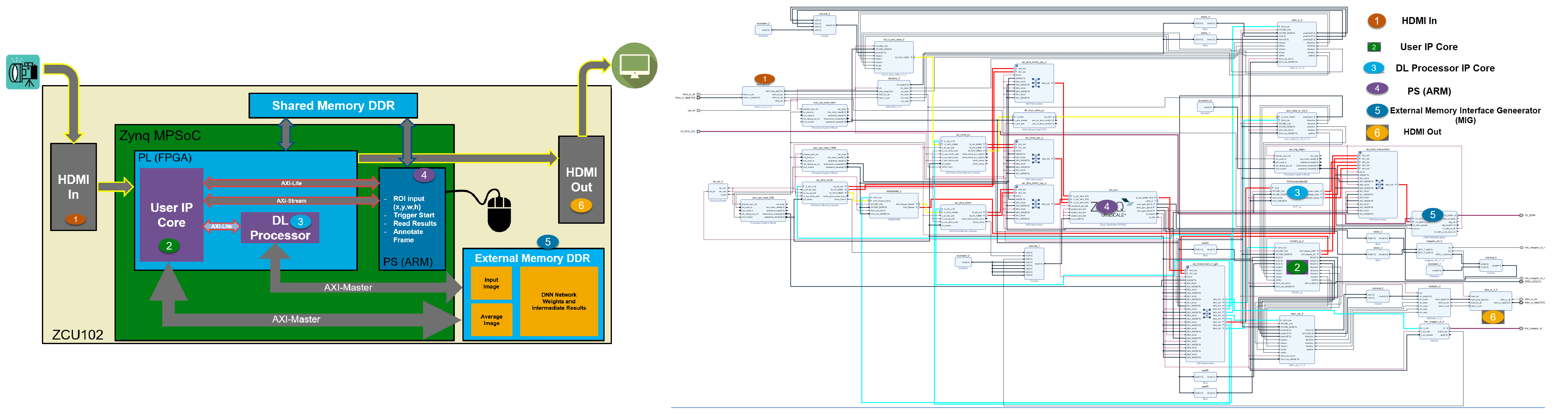

DL处理器IP核的系统集成

手动将生成的深度学习(DL)处理器IP核集成到系统设计中

深度学习HDL工具箱™生成深度学习(DL)处理器IP核,并为支持的FPGA板构建FPGA比特流。万博1manbetx有关更多信息,请参见生成自定义处理器IP和生成定制的比特流.

你可以通过以下方法加速将生成的DL处理器IP核心集成到你的系统设计中:

生成DL处理器IP核心。

使用编译器生成的外部内存缓冲区分配。

格式化外部存储器的输入和输出数据。

创建AXI4寄存器映射。AXI4寄存器允许使用MATLAB®对DL处理器IP核进行控制和编程。

主题

开始

了解生成的深度学习处理器IP核。

使用编译器输出将生成的深度学习处理器IP核集成到您的设计中。

定义输入和输出外部存储器的数据格式。

利用MATLAB或其他AXI4主设备对深度学习处理器IP核进行控制和编程。