UVM组件发电概述

UVM组件发电概述

如果你有一个万博1manbetx®编码器™许可证,您可以生成一个普遍的验证方法(UVM)试验台和附加组件从一个仿真软件模型。万博1manbetx生成UVM组件可以直接从您的仿真软件环境过渡到UVM框架。万博1manbetx

高密度脂蛋白校验™出口仿真软件子系统内部生成万博1manbetx的C代码UVM组件直接编程接口(DPI)。你可以将这些生成的组件集成到您的现有UVM环境。您还可以使用生成的UVM试验台测试的高密度脂蛋白DUT取代生成的行为DUT详细的HDL设计。

准备UVM组件生万博1manbetx成仿真软件模型

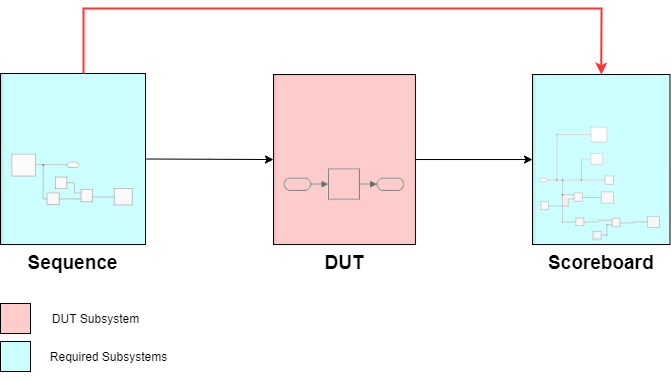

仿真软件模万博1manbetx型必须包括这些子系统。

DUT子系统。这个子系统生成一个SystemVerilog DPI (SVDPI) DUT的行为模型。关于SystemVerilog DPI代的更多信息,请参阅DPI组件生成与仿真软件万博1manbetx。

一个序列子系统。这个子系统产生刺激和推动DUT。

一个记分牌子系统。这个子系统收集和检查DUT的输出。

序列还可以直接驱动信号记分牌,见红图仿真软件模型结构。万博1manbetx

有关如何创建一个子系统,明白了创建子系统(万博1manbetx模型)。

万博1manbetx仿真软件模型结构

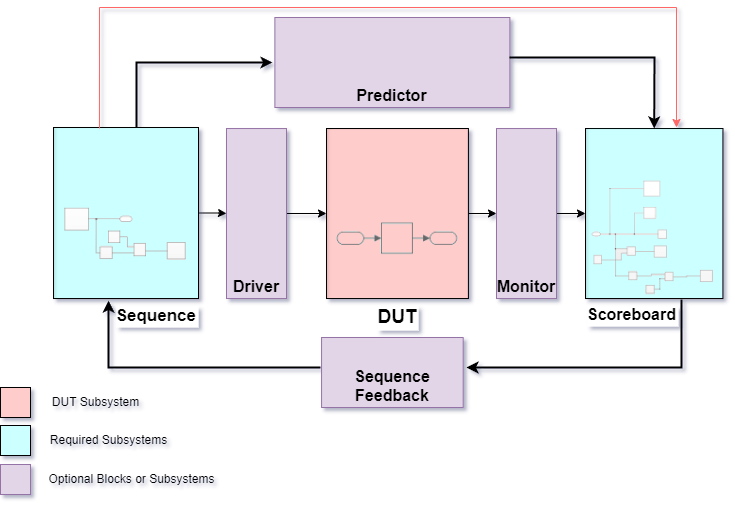

除了前面的结构,您可以选择包含这些子系统。

一个司机子系统

监控子系统

当添加监控或驱动子系统,该功能支持这些配置。万博1manbetx

如果你的模型包括一个司机子系统,那么所有的信号序列必须连接到驱动程序或记分牌。

如果您的模型包括一个司机子系统,那么所有的信号必须连接到DUT的司机。

如果您的模型包括一个监控子系统,那么所有的信号必须连接到DUT的班长。

如果您的模型包括一个监控子系统,那么所有信号的监测必须在记分板连接。

这张图片显示了一个仿真软件模型,包括一万博1manbetx个驱动子系统和监控子系统。

选择系统目标

因为UVM代利用技术生成SystemVerilog DPI,您必须先选择一个支持系统目标文件。万博1manbetx打开配置参数对话框,并选择代码生成从左边窗格。为系统目标文件,点击浏览,然后选择systemverilog_dpi_grt.tlc从列表中。

另外,如果你有嵌入式编码器®产品,您可以选择目标systemverilog_dpi_ert.tlc。这个目标使您能够访问额外的代码生成选项当您选择代码生成左窗格的配置参数对话框。

UVM代的例子,请参阅从模型生成参数化UVM试验台万博1manbetx。

生成UVM结构

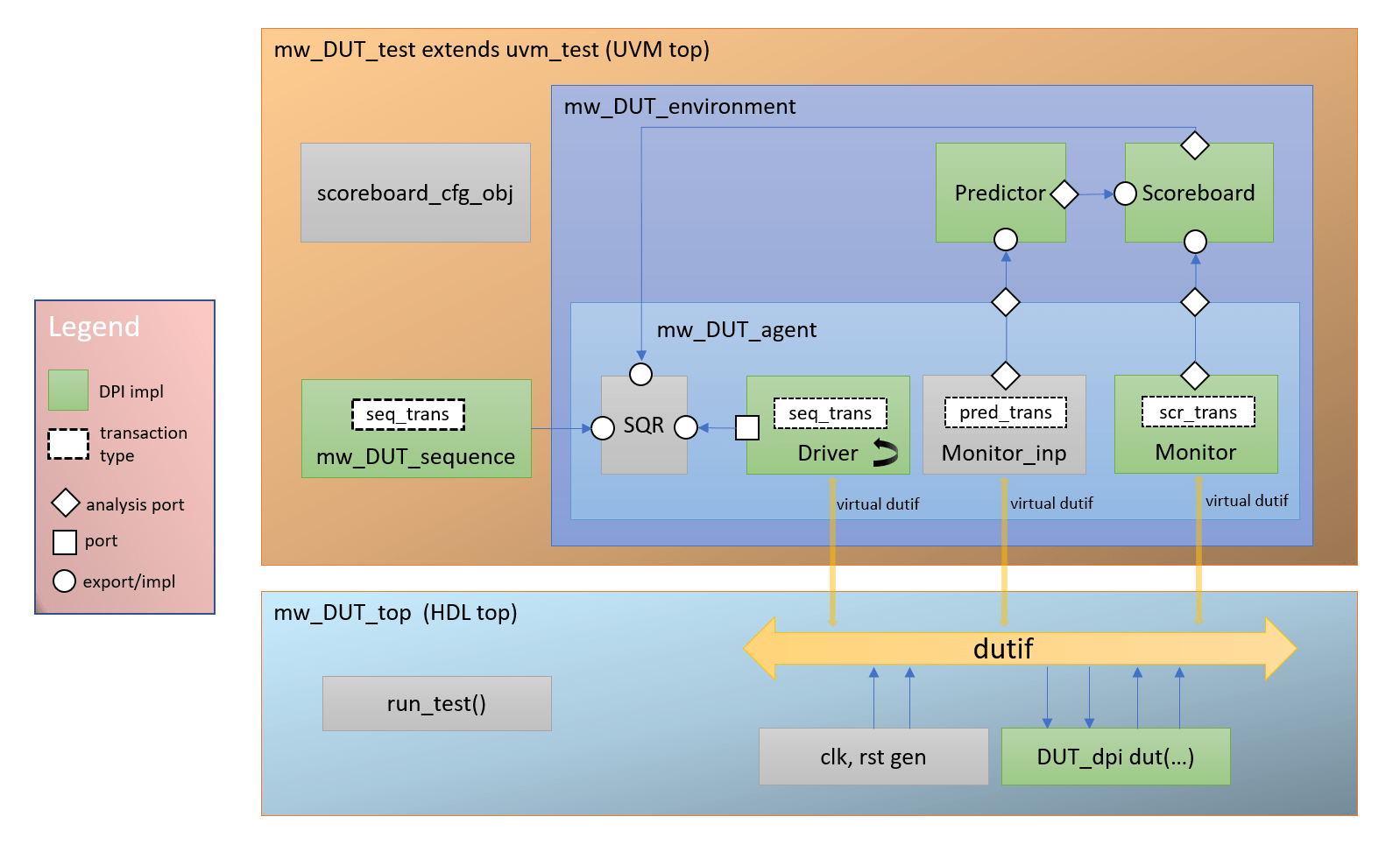

使用uvmbuild函数来生成这个UVM组件的结构。

这个模块实例化一个行为DUT生成和测试环境。高层模块时钟和复位信号传播到设计。

DUT -行为design-under-test从模型生成模块DUT子系统。万博1manbetx

测试这个模块包括UVM环境和序列类。

序列——这UVM对象定义了一组事务。模型序列的序列对象生成子系统。万博1manbetx

环境——这个模块包括代理和生成的记分牌。

记分板——UVM记分板从模型生成记分牌子系统。万博1manbetx

代理——UVM代理包括音序器,司机,和监控。如果直接从模型序列路径子系统仿真软件记分牌子系统,额外的监控,图中万博1manbetx红色所示,包括监控信号。

音序器这个模块控制序列流DUT事务。

司机这个模块从模型生成驱动子系统和转换每个事务的行为DUT理解序列信号。万博1manbetx

监控这个模块从模型生成监控子系统和从行为样本信号发送到DUT并生成事务UVM记分牌。万博1manbetx

关于UVM组件和结构的更多信息,参见UVM参考指南。

生成的文件和文件夹结构

当生成UVM组件,高密度脂蛋白验证器生成SystemVerilog DPI组件从DUT,序列,记分牌子系统。DPI生成的工件放置在三个目录,一个为每个子系统:DUT,序列和记分板。每个人的三个子系统,与这些内容创建一个文件夹。

子系统_build子系统_build

子系统_dpi_pkg.sv子系统_dpi.svDPI组件和扩展. c和. h头文件

元数据和信息文件扩展.mat .dmr, .tmw, . def . txt

编译组件的makefile . o和所以的文件

生成指定子系统三个文件夹之后,第四个文件夹为额外的UVM组件创建文件和执行脚本。文件夹命名top-model-name_uvmbuild / uvm_testbenchtop-model-name是你的名字前仿真软件模型。万博1manbetx这个文件夹包含几个子文件夹。

DPI_dut这个文件夹包含一份SystemVerilog包,模块文件,和一个. dll文件dut_build记分板这个文件夹包含一份SystemVerilog包和一个. dll文件记分板_build序列这个文件夹包含一份SystemVerilog包和一个. dll文件序列_build前这个文件夹包含SystemVerilog包和模块文件顶部仿真软件模型。万博1manbetx这个文件夹还包含HDL-simulator执行的脚本。uvm_artifacts这个文件夹包含这些SystemVerilog文件。mw_dpi_types_pkg.sv——这个文件包含的定义生成SystemVerilog类型,如枚举和结构体,由UVM组件接口暴露。只有UVM组件使用这些类型导入这个包。mw_这个文件包含一个UVM对象定义了记分板的输入事务类型。DUT_trans.svmw_这个文件定义了DUT SystemVerilog接口类型。它包含DUT的输入和输出,以及港口时钟,重置,clock-enable信号。DUT_if.svmw_,这个文件包含一个直通UVM默认驱动程序。当指定的司机子系统DUT_driver.svuvmbuild功能,该模块包括一个调度器和DPI的API调用组件司机_dpi_pkg.svmw_,这个文件包含一个直通UVM监视器。监测样本信号从驾驶员记分板。DUT_monitor_input.svmw_,这个文件包含一个直通UVM监视器。监测样本信号DUT的记分牌。当指定的监控子系统DUT_monitor.svuvmbuild功能,该模块包括一个调度器和DPI-component API调用监控_dpi_pkg.svmw_,这个文件包含一个UVM代理实例化序列,司机,和监控。DUT_agent.svmw_——这个文件包括UVM环境中,实例化一个代理和一个记分牌。DUT_environment.svmw_,这个文件包含一个UVM测试,实例化一个环境和序列。测试模块通过调用启动事务DUT_test.svseq.start。

当指定监视器或司机uvmbuild函数,两个额外的目录中生成uvm_testbench目录中。

司机——这个文件夹生成如果你指定的监控子系统uvmbuild函数。这个文件夹包含一份SystemVerilog包和一个共享库文件(dll文件或文件)司机_build监控——这个文件夹生成如果你指定的监控子系统uvmbuild函数。这个文件夹包含一份SystemVerilog包和一个共享库文件(dll文件或文件)监控_build

万博1manbetx支持万博1manbetx数据类型

万博1manbetx支持模型的数据类型转万博1manbetx换为SystemVerilog数据类型,如表所示。

生成SystemVerilog类型

| MATLAB® | SystemVerilog | ||

|---|---|---|---|

| 兼容的C类型 | 逻辑向量 | 位向量 | |

uint8 |

字节无符号 |

逻辑(7:0) |

位(7:0) |

uint16 |

shortint无符号 |

逻辑15:0 |

位(15:0) |

uint32 |

int无符号 |

逻辑(31:0) |

位(31:0) |

uint64 |

longint无符号 |

逻辑(63:0) |

位(63:0) |

int8 |

字节 |

逻辑(7:0)签署 |

位签署(7:0) |

int16 |

shortint |

逻辑(15:0)签署 |

位签署(15:0) |

int32 |

int |

逻辑(31:0)签署 |

位签署(31:0) |

int64 |

longint |

逻辑(63:0)签署 |

位签署(63:0) |

布尔 |

字节无符号 |

逻辑0时 |

位(0时) |

| 定点 | 端口是符号扩展到一个内置的C类型,如 |

逻辑向量长度( |

位向量的长度( |

单 |

shortreal |

||

双 |

真正的 |

||

复杂的 |

你可以选择一个SystemVerilog之间 |

||

| 向量,矩阵 | 数组 例如,一个4×2的矩阵矩阵模型转化为一维SystemVerilo万博1manbetxg八个元素的数组。编码器平缓矩阵列为主的顺序。 |

||

| nonvirtual总线 | 你可以选择一个SystemVerilog之间 |

||

| 枚举数据类型 | 枚举 |

||

限制

高密度脂蛋白校验矩阵和向量转换为一维数组SystemVerilog。例如,一个4×2的矩阵矩阵模型转化为一维SystemVerilo万博1manbetxg八个元素的数组。

的

uvmbuild未指定函数忽略了仿真软件组件DUT万博1manbetx,序列,记分板,司机,或监控子系统。您可以使用反馈回路内的任何子系统,但不是他们之间。

序列和记分板子系统必须运行在一个单一税率,和子系统的基本示例倍必须相等。样品倍更多信息,请参阅样品在系统(万博1manbetx模型)。

司机的基本样例次,DUT,监控子系统必须相等。可以多重速率的端口,但最大公约数(GCD)或基本样本时间必须相同。

的样本时间序列和记分板子系统必须大于或等于基本样本的司机,DUT,班长。