FPGA可编程滤波器

这个例子展示了如何实现一个可编程数字滤波器对硬件。你可以通过加载程序过滤所需的响应系数为内部寄存器使用memory-style接口。

这个例子实现了一个银行的两个过滤器,每一个都有不同的反应。过滤器有相同的长度和对称系数。这种模式系数允许块共享乘数的对称系数对过滤器以同样的方式。相同的滤波器硬件可编程与新系数来获得不同的滤波器响应。

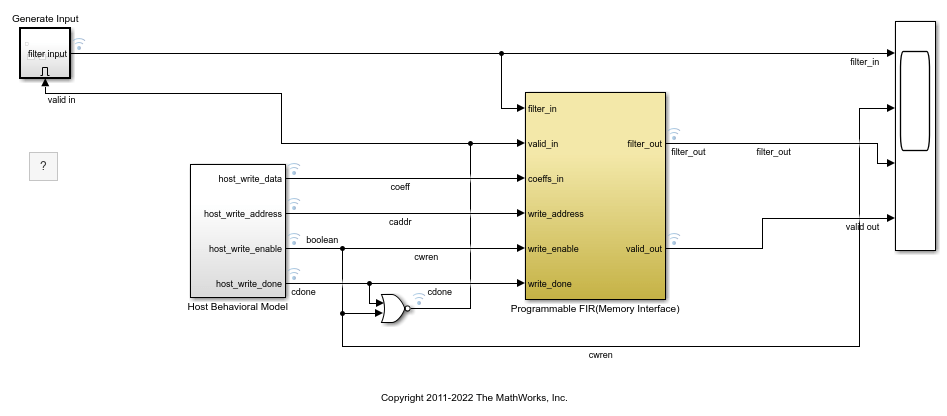

可编程滤波器模型

这个例子实现了两个FIR滤波器,一个低通响应和高通滤波响应。模型属性中指定系数> > InitFcn回调函数。

可编程的冷杉(内存接口)子系统包含离散冷杉过滤块,与系数来源参数设置为输入端口(内存接口)。这种配置使memory-style的港口,你可以写滤波器系数。首先,主持人行为模型子系统加载冷杉滤波器低通滤波器系数。模型的延迟输入唧唧声样本,直到第一个系数编写完成。然后主持人行为模型子系统加载高通滤波系数。

当你写系数过滤器,过滤器忽略任何输入数据样本。这个模型停止发送输入数据而系数发生变化。您还可以使用输出有效信号确定何时输出数据是有效的。

离散冷杉过滤器阻塞在这个模型配置为使用一个完全平行的直接形式收缩架构。块还支持使用memory-st万博1manbetxyle当块使用并行可编程系数转置或串行架构。的系数的原型参数设置为一个系数向量。此设置允许块优化硬件资源基于对称和新鲜感的位置系数。当你指定一个原型,所有输入系数集的原型在对称和位置必须匹配新鲜感系数。关于如何使用的更多细节原型滤波器优化资源,明白了可编程滤波器优化资源(DSP HDL工具箱)。

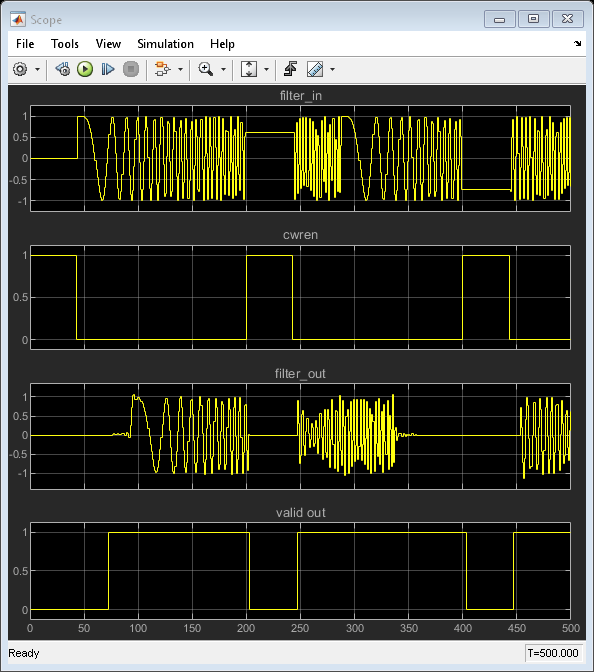

万博1manbetx仿真软件仿真结果

查看输入和输出数据和信号的系数界面,打开和运行示例模型范围。

使用逻辑分析仪

您还可以查看逻辑分析仪的信号模型。逻辑分析仪可以查看多个信号在一个窗口,让你找到信号的转换和测量信号之间的延时。

从模型的将来发布启动逻辑分析仪。

模型已经有一些感兴趣的信号(输入系数,写地址,写启用,编写完成,过滤器,过滤,有效信号)添加到观察的逻辑分析仪。

逻辑分析仪显示也可以控制在一波或per-divider基础。修改单个波或分频器,选择一个波或分频器,然后单击波选项卡。一个有用的模式,在逻辑分析仪是可视化模拟格式。

有关更多信息,请参见逻辑分析仪。

生成HDL代码和试验台

你必须有一个高密度脂蛋白编码器™许可生成这个例子的HDL代码模型。使用此命令可生成HDL代码。

systemname = [modelname' /可编程冷杉(内存接口)'];makehdl (systemname);

使用此命令来生成一个试验台相比,高密度脂蛋白模拟对模型模拟结果的行为。万博1manbetx

makehdltb (systemname);

另请参阅

相关的话题

- 可编程滤波器优化资源(DSP HDL工具箱)