可编程FIR滤波器的FPGA

这个例子展示了如何实现一个可编程的FIR滤波器的硬件。您可以通过使用主机接口将系数加载到内部寄存器,从而为过滤器编写所需的响应。

在这个例子中,我们将在一个芯片上实现一组滤波器,每个滤波器都有不同的响应。如果所有的过滤器有一个直接形式的FIR结构,和相同的长度,然后我们可以使用一个主机接口来加载系数为每个响应到一个寄存器文件时,需要的。

这种设计在输入样本可以用加载系数处理之前增加了几个周期的延迟。然而,它的优点是相同的滤波器硬件可以编程与新的系数,以获得不同的滤波器响应。这节省芯片区域,否则每个过滤器将在芯片上单独执行。

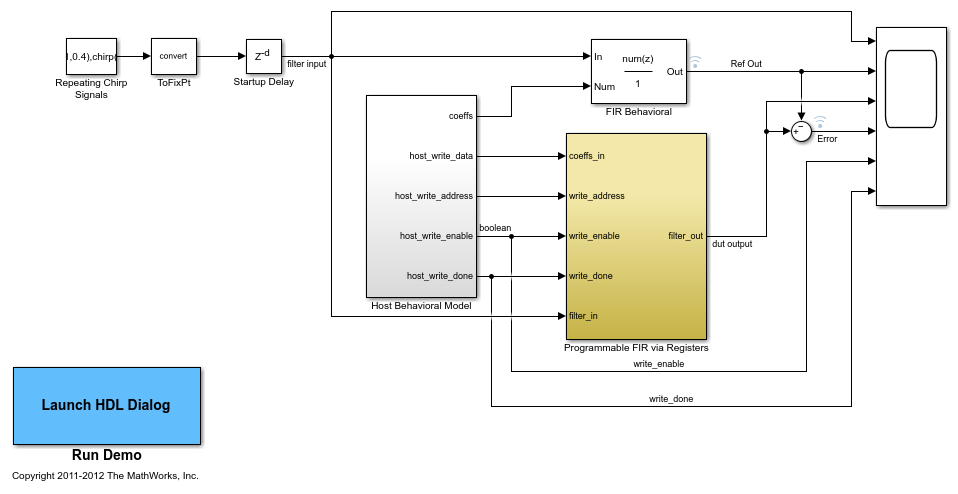

模型可编程序FIR滤波器

考虑两个FIR滤波器,一个具有低通响应,另一个具有高通响应。这些系数是通过使用模型属性>回调>InitFcn函数指定的。

modelname =“dspprogfirhdl”;open_system (modelname);

的可编程FIR通过寄存器块加载低通系数从主机行为模型,并先处理输入的啁啾样本。然后,该模块加载高通系数并再次处理相同的啁啾样本。

open_system ([modelname'/可编程FIR通过寄存器']);

的coeffs_registers块将系数加载到内部寄存器中write_enable信号是高。阴影寄存器由系数寄存器更新write_done信号是高。阴影寄存器允许由过滤器实体同时加载和处理数据。分块在处理最后几个输入样本的同时加载第二组系数。

该模型被配置为使用一个完全并行的结构离散FIR滤波器块。您还可以从高密度脂蛋白块属性菜单。

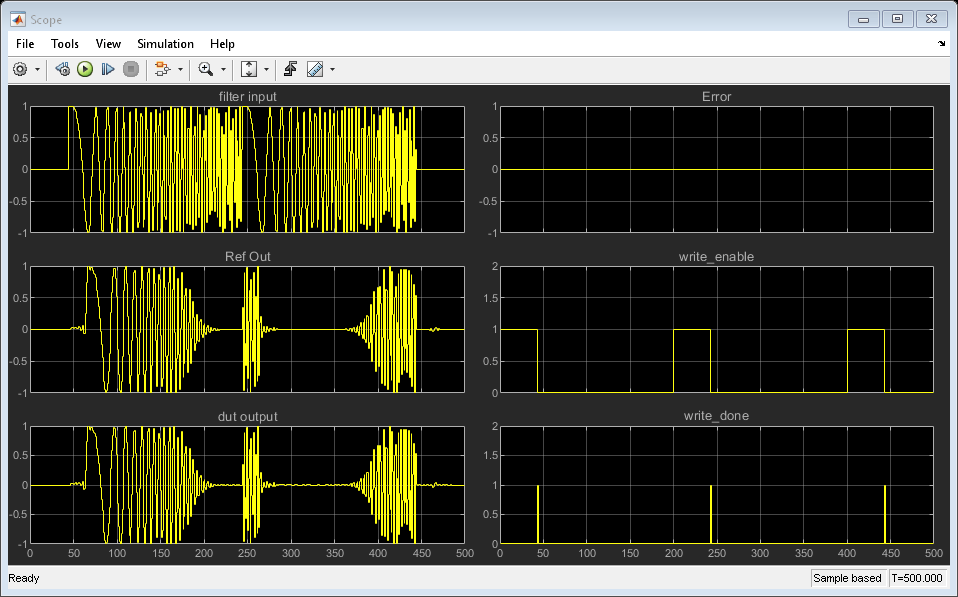

万博1manbetx仿真软件®仿真结果

要比较Design Under Test (DUT)和引用过滤器,请打开范围并运行示例模型。

open_system ([modelname/范围的]);sim (modelname);

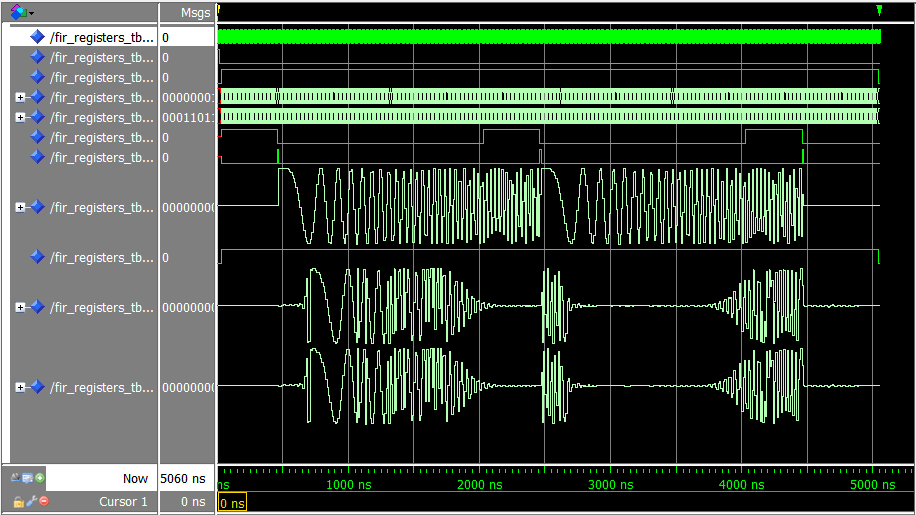

使用逻辑分析器

您还可以在逻辑分析器中查看信号。逻辑分析器允许您在一个窗口中查看多个信号。它还可以很容易地发现信号中的转换。

从模型的工具栏启动逻辑分析器。

感兴趣的信号——输入系数、写地址、写启用、写完成、过滤、过滤、参考和错误都被添加到逻辑分析器中以供观察。

逻辑分析器的显示也可以控制在一个波或分频基础上。要修改一个单独的波浪或分割器,选择一个波浪或分割器,然后点击“波浪”标签。在逻辑分析器中,一种有用的可视化方式是模拟格式。

有关逻辑分析器的进一步信息,请参阅逻辑分析仪文档。

生成HDL代码和测试平台

您必须拥有HDL Coder™许可证才能为这个示例模型生成HDL代码。使用此命令生成HDL代码。systemname = [modelname '/可编程FIR通过寄存器'];makehdl (systemname);

使用此命令生成一个测试台,用来比较HDL模拟和Simulink模拟行为的结果。万博1manbetxmakehdltb (systemname);

ModelSim™仿真结果

下图显示了在运行为测试工作台生成的.do文件脚本后的ModelSim HDL模拟器。将ModelSim结果与之前绘制的Simulink结果进行比较。万博1manbetx