为FPGA实现数字升频器

这个例子展示了如何设计一个数字升频器(DUC) LTE等无线电通信的应用程序,并生成HDL代码。

介绍

duc广泛应用于数字通信发射机基带信号转换为射频(RF)或中频(IF)信号。DUC操作增加了信号的采样率和转移到更高的频率,便于后续处理阶段。本例中的DUC执行采样率转换使用四级过滤器链复杂频率翻译紧随其后。这个例子首先设计DUC浮点DSP系统工具箱™功能。然后,每个阶段转换为定点,在仿真软件中使用®模型,生成synthesizable HDL代码。万博1manbetx本例使用这两个测试信号来演示和验证DUC操作:

一个正弦信号调制到一个32 MHz如果载体。

一个LTE下行信号带宽为1.4 MHz,如果载波调制到32 MHz。

的例子降频转换器输出浮点和定点duc,并比较这两个输出的信号质量。

最后,提供了一个示例实现fpga的过滤器链,并合成结果。

这个示例使用DUCTestUtils一个助手类,其中包含函数生成刺激和分析DUC输出。有关更多信息,请参见DUCTestUtils.m文件。

DUC结构

DUC由一个插值过滤器链,数控振荡器(NCO)和混合器。过滤器链由一个低通滤波器插入器,halfband插入器,中投公司补偿插入器(杉木),中投插入器,中投获得校正。

过滤器链的整体反应相当于一个插值滤波器的相同的规范。然而,将滤波器分解到多个插值结果以更有效的设计阶段,使用更少的硬件资源。

第一个低通滤波器插入器实现了精确成就和FstopDUC的特性。halfband过滤器是一个中间插入器。较低的采样率在链的开始意味着早期的过滤器可以优化资源使用共享乘数。中投补偿插入器提高了光谱响应补偿后的中投在插值由两个下垂。中投插入器提供了一个大的插值系数,满足过滤器链upsampling需求。

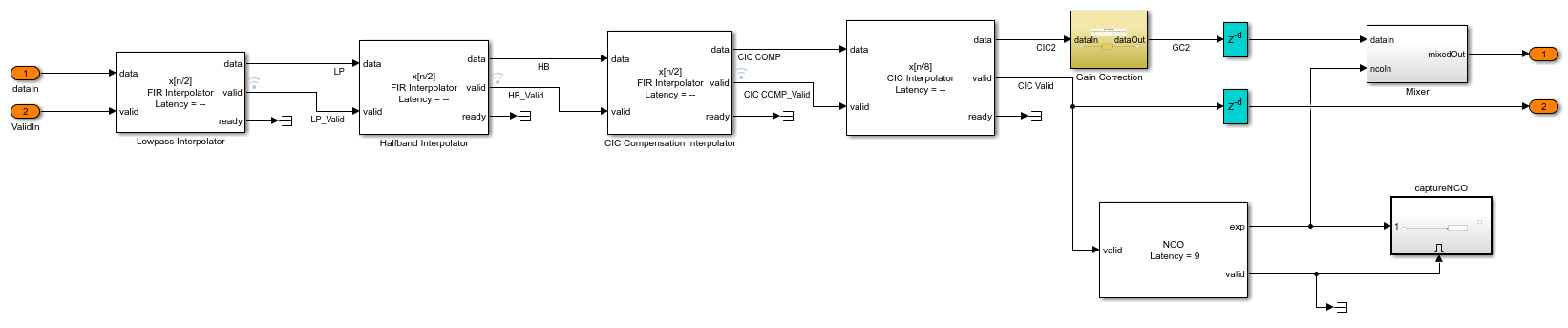

这幅图显示了DUC的框图。

DUC输入的采样率是1.92议员,和采样率是122.88 m / s的输出。这些利率给整体插值64倍。LTE接收器使用1.92议员作为典型的采样率对细胞搜索和主信息块(MIB)复苏。DUC过滤器是为了适合这个应用程序。DUC优化运行时钟频率为122.88 MHz。

DUC设计

本节解释如何使用浮点操作和设计DUC MATLAB®滤波器函数。DUC对象允许您指定几个特征定义的级联反应的四个过滤器,包括通带和阻带频率,通带波纹,阻带衰减。

DUC参数

这个例子设计DUC滤波器特性满足这些期望的响应值为给定的输入采样率和载波频率。

傅氏国际= 1.92 e6;%在DUC输入采样率FsOut = 122.88;%输出采样率Fc = 32 e6;%载波频率成就= 540年e3;%通带频率,相当于36 * 15 khz LTE副载波Fstop = 700年e3;%阻带频率美联社= 0.1;%通带纹波Ast = 60;%阻带衰减

第一个低通滤波器插入器

这个过滤器插入两个,在过滤器链的采样率最低。低采样率意味着这个过滤器可以使用一个高效的硬件实现资源共享。

lowpassParams。傅氏国际=国际;lowpassParams。InterpolationFactor = 2;lowpassParams。FsOut =国际* lowpassParams.InterpolationFactor;lowpassSpec = fdesign.interpolator (lowpassParams.InterpolationFactor,…低通滤波器的,“Fp,置,美联社,Ast”成就,Fstop,美联社,Ast, lowpassParams.FsOut);lowpassFilt =设计(lowpassSpec,“SystemObject”,真正的)

lowpassFilt = dsp。FIRInterpolator属性:InterpolationFactor: 2 NumeratorSource:“财产”分子:[0.0020 -0.0027 - -0.0050 0.0021 - 4.9115 e-04……使用能显示所有属性

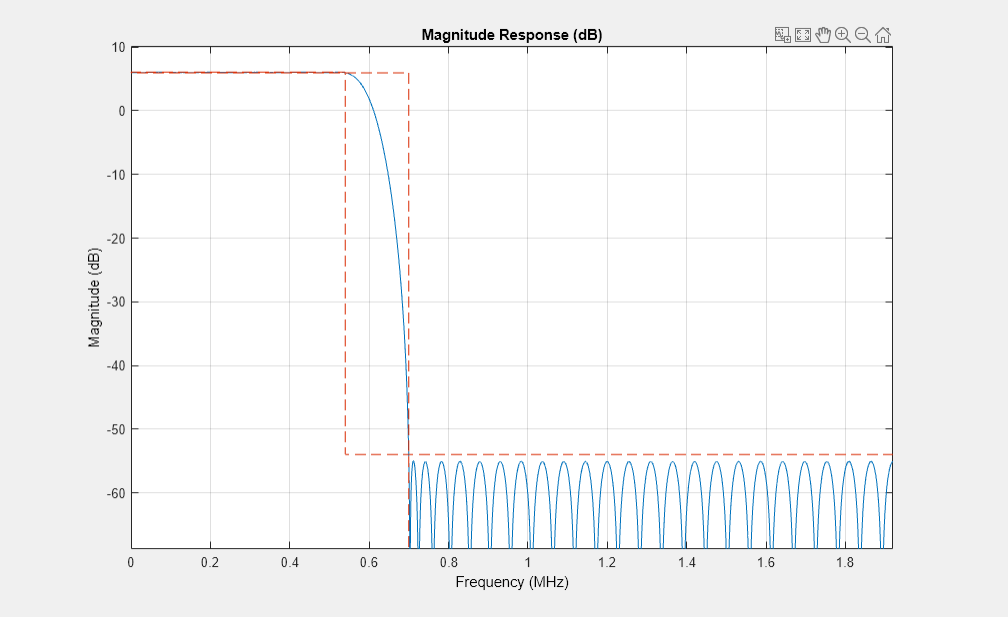

显示的大小响应低通滤波器没有得到修正。

ducPlots。低通滤波器= fvtool (lowpassFilt,“Fs”傅氏国际* 2,“传奇”,“关闭”);

第二个Halfband插入器

两个halfband过滤器提供了有效的插值。Halfband过滤器是高效的硬件,因为大约一半的系数等于零,和这些乘数是排除在硬件实现。

hbParams。傅氏国际= lowpassParams.FsOut;hbParams。InterpolationFactor = 2;hbParams。FsOut = lowpassParams.FsOut * hbParams.InterpolationFactor;hbParams。TransitionWidth = hbParams。傅氏国际- 2 * Fstop;hbParams。StopbandAttenuation = Ast; hbSpec = fdesign.interpolator(hbParams.InterpolationFactor,“halfband”,…“TW, Ast”,…hbParams.TransitionWidth,…hbParams.StopbandAttenuation,…hbParams.FsOut);hbFilt =设计(hbSpec,“SystemObject”,真正的)

hbFilt = dsp。FIRInterpolator属性:InterpolationFactor: 2 NumeratorSource:“财产”分子:[0.0178 -0.1129 -0.1129 0.5953 0.5953 - 1 0 0…使用能显示所有属性

可视化的幅度响应halfband插值。

ducFilterChain = dsp.FilterCascade (lowpassFilt hbFilt);ducPlots。hbFilt = fvtool (lowpassFilt hbFilt ducFilterChain,…“Fs”,(国际* 2,国际* 4,国际* 4]);传奇(ducPlots.hbFilt…“低通插值器”,…“Halfband插入器的,…“低通+ Halfband”);

中投公司补偿插入器

因为过去的CIC滤波器的幅度响应显著下垂通带内的地区,示例使用一个FIR-based下垂补偿滤波器通带响应变平。下垂的补偿器和中投插入器相同的属性。这个过滤器实现插值的两倍,所以你也必须指定过滤器bandlimiting特征。同时,指定中投插入器属性用于补偿滤波器以及后来中投插入器。

使用设计函数返回一个过滤系统对象与指定的特征。

compParams。傅氏国际= hbParams.FsOut;compParams。InterpolationFactor = 2;%中投补偿插值系数compParams。FsOut = compParams.FsIn * compParams.InterpolationFactor;%的新采样率compParams。成就= 1/2*compParams.FsIn + Fpass;% CIC补偿通频带的频率compParams。Fstop= 1/2*compParams.FsIn + 1/4*compParams.FsIn;% CIC补偿阻带频率compParams。美联社=美联社;%整体滤波器通带波纹一样compParams。Ast = Ast;%整体滤波器阻带衰减一样N = 31;% 32抽头滤波器利用16输入之间的周期cicParams。InterpolationFactor = 8;%中投插值因子cicParams。DifferentialDelay = 1;%中投插入器微分延迟cicParams。NumSections = 3;%中投插入器的数量积分器和梳部分compSpec = fdesign.interpolator (compParams.InterpolationFactor,“ciccomp”,…cicParams.DifferentialDelay,…cicParams.NumSections,…cicParams.InterpolationFactor,…“N, Fp,美联社,Ast”,…N compParams.Fpass compParams.Ap compParams.Ast,…compParams.FsOut);compFilt =设计(compSpec,“SystemObject”,真正的)

compFilt = dsp。FIRInterpolator属性:InterpolationFactor: 2 NumeratorSource:“财产”分子:[-6.9876 e-04 -0.0099 0.0038 0.0134 -0.0255……使用能显示所有属性

中投公司补偿插入器的响应。

ducFilterChain = dsp.FilterCascade (lowpassFilt hbFilt compFilt);ducPlots。cicComp = fvtool (lowpassFilt hbFilt、compFilt ducFilterChain,…“Fs”,(国际* 2,国际* 4,国际* 8,国际* 8]);传奇(ducPlots.cicComp…“低通插值器”,…“Halfband插入器的,…“中投Comp插入器”,…“低通+ Halfband +中投Comp”);

中投插入器

最后过滤阶段被实现为一个中投插入器,因为这种类型的滤波器有效地实现一个大死亡因素的能力。CIC滤波器的反应类似于移动平均滤波器级联,但CIC滤波器不使用乘法或除法。因此,CIC滤波器有一个很大的直流增益。

cicParams。傅氏国际= compParams.FsOut;cicParams。FsOut = cicParams.FsIn * cicParams.InterpolationFactor;cicFilt = dsp.CICInterpolator (cicParams.InterpolationFactor,…cicParams.DifferentialDelay cicParams.NumSections)% #好< * NOPTS >

cicFilt = dsp。CICInterpolator属性:InterpolationFactor: 8 DifferentialDelay: 1 NumSections: 3 FixedPointDataType:完整精确的

可视化的幅度响应中投插值。中投过滤器在内部使用定点运算,所以fvtool情节量化和unquantized反应。

ducFilterChain = dsp.FilterCascade (lowpassFilt hbFilt、compFilt cicFilt);ducPlots。cicInter = fvtool (lowpassFilt hbFilt、compFilt cicFilt, ducFilterChain,…“Fs”,(国际* 2,国际* 4,国际* 8,国际* 64,国际* 64));传奇(ducPlots.cicInter…“第一Halfband插入器的,…“第二Halfband插入器的,…“中投公司补偿插入器”,…“中投插入器”,…“总体响应”);

每个插入器的直流增益是由其插值系数。中投比其他过滤器插入器有较大的增益。调用获得这种滤波器的增益系数函数。

因为中投获得是2的幂,增益系数的硬件实现容易正确使用移位操作。进行分析的目的,这个例子代表用一抽头增益校正dsp.FIRFilter系统对象。将过滤器链和增益修正过滤到一个dsp.FilterCascade系统对象。

cicGain =增益(cicFilt)增益= lowpassParams.InterpolationFactor *…hbParams.InterpolationFactor * compParams.InterpolationFactor *…cicParams.InterpolationFactor * cicGain;GainCorr = dsp.FIRFilter (“分子”1 /增益)

cicGain = 64 GainCorr = dsp。FIRFilter属性:结构:“直接形式”NumeratorSource:“财产”分子:2.4414 e-04 InitialConditions: 0使用能显示所有属性

情节整体连锁反应有或没有获得校正。

ducPlots。overallResponse = fvtool (ducFilterChain dsp.FilterCascade (ducFilterChain GainCorr),…“Fs”,国际* 64,国际* 64);传奇(ducPlots.overallResponse…“总体响应:没有获得校正”,…“总体响应:增益校正”);

定点转换

的频率响应浮点DUC过滤器链现在符合规范。接下来,量化每个过滤阶段使用定点类型和分析他们确认过滤器链仍然符合规范。

过滤器量子化

这个示例使用16位系数,满足规范。使用少于18位系数的数量降至最低,DSP模块所需的FPGA实现。DUC过滤器链的输入16位数据与15分位。滤波器输出的是18位值,提供额外的空间在中间和精确的信号。

%的第一个低通滤波器插入器lowpassFilt。FullPrecisionOverride = false;lowpassFilt。CoefficientsDataType =“自定义”;lowpassFilt。CustomCoefficientsDataType = numerictype(15)[], 16日;lowpassFilt。ProductDataType =“充分精确”;lowpassFilt。AccumulatorDataType =“充分精确”;lowpassFilt。OutputDataType =“自定义”;lowpassFilt。CustomOutputDataType = numerictype([], 18岁,14);% HalfbandhbFilt。FullPrecisionOverride = false;hbFilt。CoefficientsDataType =“自定义”;hbFilt。CustomCoefficientsDataType = numerictype(14)[], 16日;hbFilt。ProductDataType =“充分精确”;hbFilt。AccumulatorDataType =“充分精确”;hbFilt。OutputDataType =“自定义”;hbFilt。CustomOutputDataType = numerictype([], 18岁,14);% CIC补偿插入器compFilt。FullPrecisionOverride = false;compFilt。CoefficientsDataType =“自定义”;compFilt。CustomCoefficientsDataType = numerictype(14)[], 16日;compFilt。ProductDataType =“充分精确”;compFilt。AccumulatorDataType =“充分精确”;compFilt。OutputDataType =“自定义”;compFilt。CustomOutputDataType = numerictype([], 18岁,14);

中投插入器的选择“最低部分单词长度”定点数据类型选项自动优化内部基于输出字和字其他中投参数。

cicFilt。FixedPointDataType =“最低部分单词长度”;cicFilt。OutputWordLength = 18;

配置定点获得校正和FIR-based系统对象的属性。使用默认的对象RoundingMethod和OverflowAction属性值(“地板”和“包装”分别)。

%中投获得校正GainCorr。FullPrecisionOverride = false;GainCorr。CoefficientsDataType =“自定义”;GainCorr。CustomCoefficientsDataType = numerictype (fi (GainCorr.Numerator 1 16));GainCorr。OutputDataType =“自定义”;GainCorr。CustomOutputDataType = numerictype(1, 18岁,14);

定点分析

检查量化效果fvtool。你可以单独分析过滤器或级联。fvtool显示了量化和unquantized(参考)响应功能。例如,这个图中显示的效果量化第一冷杉过滤阶段。

ducPlots。quantizedFIR = fvtool (lowpassFilt,“Fs”lowpassParams.FsIn * 2,“算术”,“固定”);传奇(ducPlots.quantizedFIR…“低通插值器”);

重新定义ducFilterChain级联对象包括个人的定点属性过滤器。然后使用fvtool分析整个过滤器链和确认量子化DUC仍然符合规范。

ducFilterChain = dsp.FilterCascade (lowpassFilt hbFilt、compFilt cicFilt, GainCorr);ducPlots。quantizedDUCResponse = fvtool (ducFilterChain,…“Fs”傅氏国际* 64,“算术”,“固定”);传奇(ducPlots.quantizedDUCResponse…“DUC过滤器链”);

HDL-Optimized仿万博1manbetx真软件模型

设计流程的下一步是在仿真软件实现DUC使用块支持HDL代码生成。万博1manbetx万博1manbetx

模型配置

MATLAB的模式依赖于变量和设置工作空间配置块。过滤器配置块通过过滤器链对象前面定义的例子。

DUC来自的输入ducIn变量。现在,分配一个虚拟价值ducIn模型可以计算它的数据类型。在测试过程中,ducIn提供输入数据到模型中。

ducIn = 0;% #好< NASGU >

的outputFrame参数设置的帧大小根据DAC输出要求。outputFrame影响输入向量的大小和有效的采样间隔,它应该是2的幂。

outputFrame = 4;

模型结构

这个图显示的顶级DUC仿真软件模型。万博1manbetx模型导入ducIn从MATLAB工作区使用变量信号从工作区块,将信号转换为16位值,并应用DUC信号。设计单一税率,和使用有效的信号传递速度变化从块到块中。模拟输入运行比时钟慢64倍,由64年upsampled零插入。你可以从生成HDL代码HDL_DUC子系统。

modelName =“DUCforLTEHDL”;open_system (modelName);set_param (modelName“开放”,“上”);

内DUC实现HDL_DUC子系统。

set_param ([modelName' / HDL_DUC '),“开放”,“上”);

过滤块参数

所有的过滤器配置继承的系数对应的系统对象。每一块也有一个“有效输入之间的最小数量的周期”参数,用于优化生成的HDL代码。halfband,低通滤波器和CIC补偿滤波器有周期之间的有效输入,可用于资源共享——64年,32岁的分别和16个周期。

例如,因为输入的采样率低通插值块Fclk/ 64,64个时钟周期可用来处理每个输入样本。

第一个过滤器插入2。每个多相分支由一个单独的冷杉过滤器实现。因为周期之间有效的输入样本的数量大于1,每个冷杉使用部分实现的串行收缩期架构。过滤器总共有69个系数,在多相分解每个分支都有35个系数。有64个周期可供分享,所以每个分支是用一个完全实现串行冷杉。与复杂的输入,每个分支使用2乘数,总共4乘数在这个过滤器。

第二个过滤器halfband插入器。这个过滤器之间的周期也可以利用有效的输入进行资源共享。这些周期可以因为每个插入器输出有效样本之间的空闲周期。第一个过滤器64周期和篡改了2。因此,它将输出数据每32个周期。第二个过滤器6每多相分支系数,所以它可以作为一个完全实现串行冷杉。在这个过滤器,第二个分支只包含一个非零系数,它是2的幂。冷杉插入器块实现这个分支作为转变而不是乘法器。第二个过滤器然后只有2乘数。

第三个过滤器是中投公司补偿滤波器篡改的2。它总共有32系数,我们在设计指定的过滤器。过滤器是使用2完全实现连续复杂的冷杉,总共4乘数这个过滤器。

增益校正

增益校正将输出到4096年,相当于将由12位。因为输入和输出信号的增益校正每个表达与18位,该模型实现了这一转变重新解读了输出信号的数据类型。转换块来诠释12位数字有20分位而不是8分位。

set_param ([modelName“HDL_DUC /增益校正”),“开放”,“上”);

以区域块参数

NCO块产生一个复杂的矢量载波频率。这个信号去繁殖的混合器与输出信号相量。混频器的输出采样在122.88议员。

指定所需的频率分辨率,然后计算出所需要的蓄电池比特数达到预期的决议,并定义量化蓄电池部分的数量。以区域使用的量化输出蓄电池解决正弦查找表。计算阶段增加区域必须使用生成指定的载波频率。NCO的相位抖动适用于蓄电池位期间被量化。

以区域。Fd = 1;以区域。AccWL = nextpow2国际* 64 / nco.Fd) + 1;以区域。QuantAccWL = 12;以区域。PhaseInc =圆((Fc * 2 ^ nco.AccWL) /(国际* 64));以区域。NumDitherBits = nco.AccWL-nco.QuantAccWL;

NCO的块模型中配置中定义的参数以区域结构。这个图显示了NCO块参数对话框。

混合机

混合器子系统执行一个复杂的用滤波器的输出和区域。

set_param ([modelName“HDL_DUC /混合器”),“开放”,“上”);

将混合映射到DSP片FPGA,混合器是管线式块有特定的设置。混合器的延迟块被配置复位关闭如图片所示。有两个管道阶段的输入,1乘法器和加法器之间,另一个post-adder。此外,乘数和蛇都被配置为使用软件不能输出。这些块使用地板上舍入方法,和饱和溢出逻辑是禁用的。

正弦信号对载波测试

测试DUC,通过40 khz通过DUC正弦信号,输出信号调制到载波频率。信号解调并重新取样。然后免费测量的动态范围(SFDR)产生的语气和NCO的SFDR输出。

%初始化随机种子之前执行任何模拟。rng (0);%生成一个40 khz测试基调。40 ducIn = DUCTestUtils.GenerateTestTone (e3);%与浮点DUC Upconvert测试信号。ducTx = DUCTestUtils.UpConvert (Fc ducIn,国际* 64年,ducFilterChain);释放(ducFilterChain);%转换DUC的输出。ducRx = DUCTestUtils.DownConvert (ducTx、国际* 64 Fc);% Upconvert测试信号通过运行定点仿真软件模型。万博1manbetxsimOut = sim (modelName);%降频转换器DUC的输出。simTx = simOut.ducOut;simRx = DUCTestUtils.DownConvert (simTx、国际* 64 Fc);NCO %测量SFDR,浮点DUC,定点DUC输出。结果。sfdrNCO = sfdr(真正的(simOut.ncoOut),国际);结果。sfdrFloatDUC = sfdr(真正的(ducRx),国际);结果。sfdrFixedDUC = sfdr(真正的(simRx),国际);disp (“SFDR测量”);disp ([“浮点DUC SFDR:“num2str (results.sfdrFloatDUC)“数据库”]);disp ([“定点NCO SFDR:”num2str (results.sfdrNCO)“数据库”]);disp ([“定点DUC SFDR:“num2str (results.sfdrFixedDUC)“数据库”]);流(换行符);%的阴谋的SFDR NCO和定点DUC输出。ducPlots。以区域OutSDFR = figure; sfdr(real(simOut.ncoOut),FsIn); ducPlots.ducOutSDFR = figure; sfdr(real(simRx),FsIn);

SFDR测量浮点DUC SFDR: 287.944 dB定点NCO SFDR: 86.2454 dB定点DUC SFDR: 89.5756 dB

LTE信号测试

您可以使用一个LTE测试信号DUC执行更严格的测试。生成一个兼容标准LTE波形通过使用LTE工具箱™函数。然后,upconvert波形与DUC模型。使用LTE工具箱函数测量误差向量幅度(维生素)产生的信号。

rng (0);%执行这个测试只有如果你有LTE工具箱的产品。如果许可证(“测试”,“LTE_Toolbox”)%生成一个LTE测试信号通过使用LTE工具箱函数。[ducIn, sigInfo] = DUCTestUtils.GenerateLTETestSignal ();%与浮点DUC Upconvert信号调制到载波上。ducTx = DUCTestUtils.UpConvert (Fc ducIn,国际* 64年,ducFilterChain);释放(ducFilterChain);%添加噪声传输信号。ducTxAddNoise = DUCTestUtils.AddNoise (ducTx);%降频转换器接收到的信号。ducRx = DUCTestUtils.DownConvert (ducTxAddNoise、国际* 64 Fc);% Upconvert信号通过使用仿真软件模型。万博1manbetxsimOut = sim (modelName);%添加噪声传输信号。simTx = simOut.ducOut;simTxAddNoise = DUCTestUtils.AddNoise (simTx);%降频转换器接收到的信号。simRx = DUCTestUtils.DownConvert (simTxAddNoise、国际* 64 Fc);结果。evmFloat = DUCTestUtils.MeasureEVM (sigInfo ducRx);结果。evmFixed = DUCTestUtils.MeasureEVM (sigInfo simRx);disp (“LTE维生素与测量”);disp ([“浮点DUC RMS维生素:”num2str (results.evmFloat.RMS * 100, 3)“%”]);disp ([挣值管理的浮点DUC峰值都:“num2str (results.evmFloat.Peak * 100, 3)“%”]);disp ([“定点DUC RMS维生素:”num2str (results.evmFixed.RMS * 100, 3)“%”]);disp ([挣值管理的定点DUC峰值都:“num2str (results.evmFixed.Peak * 100, 3)“%”]);流(换行符);结束

LTE浮点DUC RMS维生素与维生素与测量:0.813%浮点DUC峰值维生素:2.53%定点DUC RMS维生素:0.816%定点DUC维生素:峰值2.82%

HDL代码生成和FPGA实现

生成这个例子中你必须有高密度脂蛋白HDL代码编码器™产品。使用makehdl和makehdltb命令来生成和高密度脂蛋白HDL代码的试验台HDL_DUC子系统。DUC合成在Xilinx®Zynq®-7000 ZC706评估板。表显示了邮报place-and-route资源利用率结果outputFrame大小4。设计了计时的时钟频率335 MHz。

T =表(…分类({附近地区的;“LUTRAM”;“FF”;“布莱姆。”;“DSP”}),…分类({“4708”;“654”;“6849”;' 2 ';“32”}),…“VariableNames”,{“资源”,“使用”})

T = 4708 x2词根表资源使用________ _____ LUT LUTRAM 654 FF 6849 BRAM 2 DSP 32