数字硬件中的数据类型和缩放

定点数据类型

在数字硬件中,数字以二进制字存储。二进制字是一个固定长度的比特序列(1和0)。硬件组件或软件功能如何解释这个1和0的序列是由数据类型定义的。二进制数表示为定点数据类型或浮点数据类型。

定点数据类型的特征是字长(以比特为单位)、二进制点的位置以及它是有符号的还是无符号的。二进制点的位置是用来缩放和解释定点值的方法。

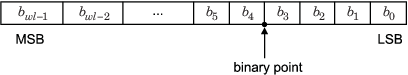

例如,一个广义定点数(有符号或无符号)的二进制表示如下所示:

在哪里

b我是我th二进制数字。

王以比特为单位的单词长度。

bwl-1是最高位(MSB)的位置。

b0是最低有效位(LSB)的位置。

二进位点显示在LSB左边四个位置。在这个例子中,这个数字被称为有四个小数位,或者一个分数长度为4。

定点数据类型可以是有符号的,也可以是无符号的。一个定点值是有符号的还是无符号的,通常不会显式地编码在二进制字中;也就是说,没有符号位。相反,符号信息是在计算机体系结构中隐式定义的。

有符号二进制定点数在计算机硬件中通常以以下三种方式之一表示:

符号/幅度-二进制字的一位始终是专用的符号位,而字的其余位编码数字的幅度。使用符号/幅度表示的否定包括将符号位从0(正)翻转到1(负),或从1到0。

补数-对补数中的二进制数求反需要按位补数。也就是说,所有的0都变成了1所有的1都变成了0。在补表示法中,有两种表示零的方法。所有0的二进制单词表示“正”零,而所有1的二进制单词表示“负”零。

Two's补体-使用带符号的Two's补体表示的否定包含位反转(转换为one的补体),然后是1的二进制加法。例如,000101的补数是111011。

Two的补码是带符号的定点数最常见的表示形式,也是定点设计器文档使用的唯一表示形式。

二进制点解释

二进位是定点数缩放的方法。通常是软件决定二进制点。当执行基本的数学功能,如加减法,硬件使用相同的逻辑电路,而不管比例因子的值。本质上,逻辑电路不知道比例因子。它们在执行有符号或无符号定点二进制代数就好像二进制点在b0.

定点设计器支持通用万博1manbetx二进位点缩放V =问✕2E,在那里V是真实世界的价值,问是存储整数值,和固定指数E等于负的分数长度。换句话说,RealWorldValue=StoredInteger✕2−FractionLength.

分数长度定义存储整数值的缩放。单词长度限制了存储的整数可以取的值,但它不限制分数长度可以取的值。该软件不限制指数的值E基于所存储整数的字长问.因为E等于−FractionLength,将二进位点限制为与分数相邻是不必要的;分数长度可以为负数,也可以大于单词长度。

例如,由三个无符号位组成的单词通常用科学记数法用以下其中一种方法:

如果指数大于0或小于-3,则表示将涉及额外的0:

这些额外的0永远不会变成1,所以它们不会显示在硬件中。与浮点指数不同,定点指数永远不会出现在硬件中,因此定点指数不受有限位数的限制。

考虑一个带符号的值,它的字长为8,分数长度为10,存储的整数值为5(二进制值)00000101).使用公式计算实字值RealWorldValue=StoredInteger✕2−FractionLength.在这种情况下,RealWorldValue= 5 2−10= 0.0048828125.因为分数长度比单词长度长2位,所以存储的整数的二进制值为x.xx00000101,在那里x是隐式零的占位符。0.0000000101(二进制)等价于0.0048828125(小数)。对于一个使用a的例子fi对象,看到分数长度大于单词长度.

浮点数据类型

浮点数据类型的特征是一个符号位、一个分数(或尾数)字段和一个指数字段。定点设计器遵循IEEE®二进制浮点算术标准754-1985(在本指南中简称为IEEE标准754),并支持半精度、单精度和双精度数据类型。万博1manbetx

在选择数据类型时,必须考虑以下因素:

结果的数值范围

结果所要求的精度

相关的量化误差(即舍入模式)

处理异常算术条件的方法

这些选择取决于您的特定应用程序、使用的计算机体系结构和开发成本等等。

使用定点设计器,您可以探索动态数字系统建模中数据类型、范围、精度和量化误差之间的关系。与万博1manbetx®编码器™,您可以根据该模型生成产品代码。使用HDL Coder™,您可以从Simulink模型和Stateflow生成可移植的、可合成的VHDL和Verilog代码万博1manbetx®图表。