用于FPGA的高吞吐量信道化器

这个示例演示了如何使用多相滤波器组实现高吞吐量(每秒gigassamples, GSPS)的硬件信道化。

高速信号处理是雷达、宽带无线和回程等应用的要求。

现代ADC能够以高达每秒数千兆个采样率对信号进行采样。但最快FPGA的时钟速度低于此采样率。FPGA通常以数百MHz的频率运行。在FPGA上执行GSPS处理的一种方法是从标量处理转移到向量处理,并以每秒的速度处理多个采样许多现代FPGA支持JESD204B标准接口,该接口以GHz时钟频率接受标量输入,并以较低的时钟频率生成样本向量。万博1manbetx

在本例中,我们展示了如何在Simulink中为GSPS吞吐量设计一个信号处理应用程序。输入数据通过JESD204B接口进行矢量化,并在FPGA中以较低的时钟速率提供。该模型是一个多相滤波万博1manbetx器组,由一个滤波器和一个FFT组成,一次处理16个样本。多相滤波器组技术ique用于最小化由于泄漏和扇形损耗导致的FFT不准确度。请参阅高分辨率光谱分析(DSP系统工具箱)有关多相滤波器组的更多信息。

示例的第一部分实现了一个带有4抽头滤波器的多相滤波器组。

示例的第二部分使用为12抽头滤波器配置的Channelizer HDL优化块。Channelizer HDL优化块使用多相滤波器组技术。

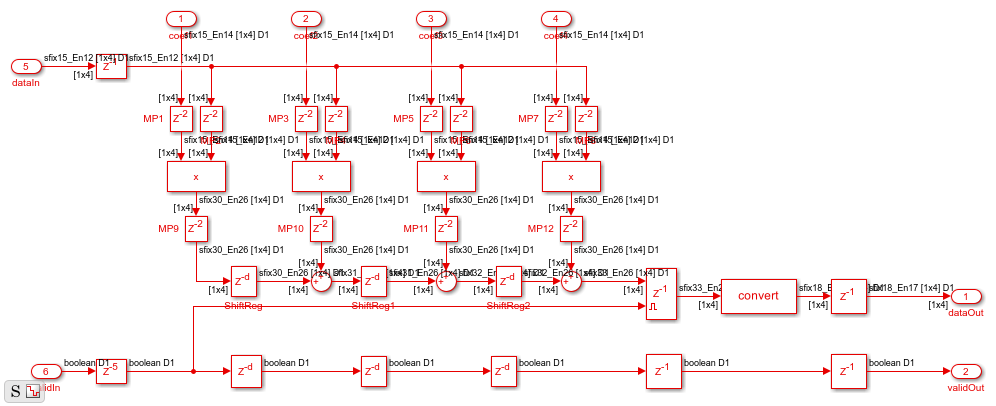

多相滤波器组

modelname =“多相滤波器组HDLEXAMPLE4tap”;open_system (modelname);

的InitFcncallback (Model Properties > callback > InitFcn)设置模型。这个模型使用512点FFT,每个频带有四个抽头滤波器。使用信道发生器(DSP系统工具箱)系统对象™来生成系数。多相法的Channelizer对象产生512 × 4矩阵。每一行代表每个波段的系数。系数被转换成与输入信号相同字长的定点。

FFT长度=512;h=dsp.信道化器;h、 NumTapsPerBand=4;h、 NumFrequencyBands=fft长度;h、 stoppandattention=60;coef=fi(多相(h),1,15,14,'roundingmethod',“收敛”);

该算法需要512个滤波器(每个波段一个滤波器)。对于一个包含16个样本的向量输入,我们可以重复使用16个过滤器,共32次。

InVect = 16;ReuseFactor = FFTLength / InVect;

为了将滤波器合成到更高的时钟速率,我们将乘数和系数库管道。这些值在“优化的硬件注意事项”部分中解释。

乘法管道=2;CoefBank管道=1;

数据源

输入数据由两个正弦波组成,200 KHz和250 KHz。

仿真结果

要可视化频谱结果,请打开频谱查看器并运行模型。

Open_System('PolyphaseFilterBankhdlexample_4TAP / FFT频谱观众/功率谱查看器(FFT)'); 开放式系统(PolyphaseFilterBankHDLExample_4tap/PFB频谱查看器/功率频谱查看器(PFB));sim (modelname);

与仅使用FFT相比,多相滤波器组的功率谱查看器显示了功率谱的改善和频率泄漏和扇形的最小化。通过比较两种频谱,并在100 KHz和300 KHz之间放大,观察多相滤波器组在-40 dB以上的峰值比经典FFT要少。

优化的硬件注意事项

数据类型:数据字长影响结果的准确性和硬件中所使用的资源。在这个例子中,我们以全精度设计了滤波器。输入数据类型为

fixdt(1, 15日,13),输出为fixdt(1,18,17).过滤系数的绝对值都小于1,所以每次乘法后数据不会增长,我们需要为每次加法添加一位。为了保持FFT的准确性,我们需要为每个阶段增加一位。这使得旋转因子相乘在每个阶段都变得更大。对于许多fpga来说,保持乘法大小小于18x18是可取的。由于512点FFT有9级,FFT的输入不能超过11位。通过对滤波系数的考察,我们观察到最大系数的前8位二进制数为零,因此我们可以将系数转换为fixdt(1,7,14)而不是Fixdt(1,15,14).我们还观察到多相滤波器组内的数据类型块输出的最大值在二进制点之后有7个前导零,因此我们将滤波器输出转换为Fixdt(1,11,17)反而。这将乘数大小保留在小于18×18的FFT内,并节省硬件资源。

设计速度:

国家控制块:国家控制块在同步模式下使用,为启用端口的延迟块生成硬件友好代码。

减少时钟使:模型被设置为在最小化时钟使能选项打开时生成HDL代码(在配置参数中选择> HDL代码生成>全局设置>端口>最小化时钟使能)。当型号为单速率时,支持此选项。万博1manbetx时钟使能是一个全局信号,不建议用于高速设计。

DSP模块在FPGA中的应用:为了将乘法器映射到FPGA中的DSP块中,乘法器应该是流水线。在此示例中,我们通过设置乘法_pipeline = 2,我们将乘法器(之前的2次延迟和2延迟);这些管道寄存器不应重置。为每个流水线设置重置类型到无(右键单击延迟块,然后选择HDL代码> HDL块属性>重置类型=无)。

ROM在FPGA中的使用:系数库中的系数块是一个组合块。为了将该块映射到ROM中,请在该块后添加一个寄存器。延迟长度由

科夫班克管道。将这些延迟的重置类型设置为无(右键单击延迟块,然后选择HDL代码>HDL块属性>重置类型=无)。

生成HDL代码和测试平台

你必须有一个HDL编码器™ 为该示例模型生成HDL代码的许可证。使用此命令生成HDL代码。systemname='PolyphaseFilterBankHdlexSample_4tap/PolyPhaseFilterBank';makehdl(系统名);

使用此命令生成测试台,该测试台与模拟模拟行为的HDL仿真结果进行比较。万博1manbetxmakehdltb(systemname);

综合结果

本设计采用ISE合成Xilinx Virtex 7 (xc7vx550t-ffg1158,速度等级3)。该设计实现了499.525 MHz的时钟频率(放置前和路由前)。在每个时钟16个样品,这转换为8 GSPS吞吐量。注意,这个子系统有大量的I/O端口,它不适合作为针对FPGA的独立设计。

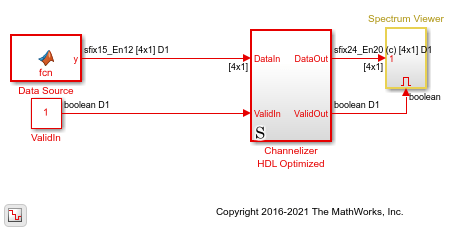

HDL优化的通道器

为了改善频率响应,使用更多的点击滤波器。以下型号使用了Channelizer HDL优化块,配置了12分频滤波器以改善频谱。使用内置的Channelizer HDL优化块可以更容易地更改设计参数。

modelname =“多相滤波器组HDLEXSAMPLE\u HDLChannelizer”;open_system (modelname);

该模型使用工作空间变量来配置FFT和滤波器。在这种情况下,该模型为每个频带使用512点FFT和12抽头滤波器。信道化器的系数数为512个频带乘以每个频带12抽头TF(h)方法生成所有系数。

InVect=16;FFTLENGHT=512;h=dsp.Channelizer;h.NumTapPerband=12;h.NumFrequencyBands=FFTLENGHT;h.StopBandAttentiation=60;coef12Tap=tf(h);

数据源

输入数据由两个正弦波组成,200 KHz和206.5 KHz。频率比第一个例子更接近,以说明信道化器和四抽头滤波器在频谱分辨率上的差异。

仿真结果

要可视化频谱结果,请打开频谱查看器并运行模型。

Open_System('PolyphaseFilterBankhdlexample_hdlchannelizer / PFB_4TAP频谱观众/功率谱查看器(PFB_4TAP)'); 开放式系统(“多相滤波器组HDLexSample\u HDL信道化器/信道化器频谱查看器/功率谱查看器(信道化器\u 12tap)”);sim (modelname);

Channelizer_12tap模型的功率谱查看器显示,与前一个模型中的4-tap滤波器相比,使用12-tap滤波器的多相滤波器组的功率谱有所改善。比较Channelizer和4-tap多相滤波器组的频谱结果。放大100 KHz和300 KHz之间的范围,观察channelizer仅检测到两个峰值,而4抽头多相滤波器组检测到两个以上的峰值。由于输入信号只有两个频率分量,因此两个峰值是预期结果。