矩阵和向量的设计考虑

这些指导方针建议如何在为HDL代码生成进行设计建模时使用矩阵和向量信号。每个指导方针都有一个严重级别,它指示遵从性需求的级别。想要了解更多,请看HDL建模指南严重性级别。

矩阵建模要求

指导ID

1.3.1

严重程度

强制性的

描述

HDL Coder™在DUT接口不支持矩万博1manbetx阵数据类型。在二维矩阵信号进入DUT子系统之前,使用整形块将信号转换为一维向量。在DUT子系统中,可以使用重塑块将向量转换回矩阵,然后执行矩阵计算。在执行计算之后,必须在DUT输出接口将矩阵转换回矢量信号。在DUT接口之外,您可以将矢量信号转换回矩阵。

建模方面的考虑

在使用重塑块将向量转换为2D矩阵时,请确保指定正确输出尺寸。

当您使用产品块时,请使用右边乘法模式。通过使用这种模式,您可以执行矩阵乘法或元素乘法。乘积的输出可以有不同的维度,这取决于乘法模式。

当您使用Product块执行矩阵乘法时,请将matrix Multiply块放入子系统块中。当您生成代码并打开生成的模型时,您会看到HDL Coder将矩阵乘法扩展为多个Product和Add块。将Matrix Multiply块放置在子系统中可以使生成的模型更容易理解。另外,请确保不要向Matrix Multiply块提供两个以上的输入。

当您提取矩阵数据时,使用选择器和赋值块。请确保您没有为块的索引输入端口使用定点数据类型。

例子

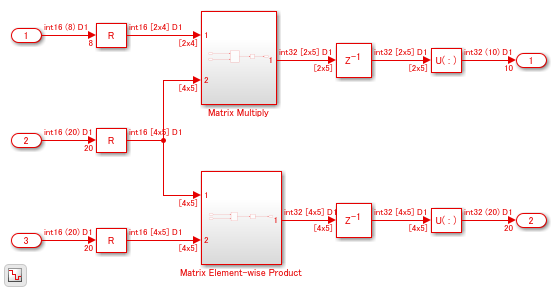

这个例子展示了如何在HDL Coder™中使用矩阵类型。打开这个模型hdlcoder_matrix_multiply。该模型包含一个重塑块,它在DUT子系统接口上将矩阵输入转换为1-D向量。

open_system (“hdlcoder_matrix_multiply”) set_param (“hdlcoder_matrix_multiply”,“SimulationCommand”,“更新”) sim卡(“hdlcoder_matrix_multiply”)

如果您打开DUT子系统,您会看到两个子系统。重塑块将一维数组转换为2乘2矩阵,以便输入到子系统。一个子系统使用Matrix Multiply块,另一个子系统执行按元素进行的乘法运算。输出结果被转换回向量。

open_system (“hdlcoder_matrix_multiply / DUT”)

如果您为DUT子系统生成HDL代码并打开生成的模型,您将看到乘法操作是如何执行的。

避免在HDL代码中从矢量信号生成升序位

指导ID

1.3.2

严重程度

强烈推荐

描述

在MATLAB®,则数组的默认位序为升序。在这种情况下生成的VHDL代码使用声明Std_logic_vector(0到n)。这个信号声明通过违反某些HDL编码标准规则而产生警告。以下是一些场景:

位序递增操作场景

| 场景 | 问题的例子 | 解决方案 |

|---|---|---|

延迟块和一个延迟的长度大于 |

这个例子演示了生成的代码延迟块和一个延迟的长度的 ENTITY Subsystem1 IS PORT(clk: IN std_logic;reset: IN std_logic;enb: IN std_logic;In1: IN std_logic;——ufix1 Out1: OUT std_logic——ufix1);Subsystem1结束;struct rtl OF Subsystem1 IS——Signals SIGNAL Delay_reg: std_logic_vector(0 TO 4);——ufix1[5]信号Delay_out1: std_logic;——ufix1 |

而不是使用延迟块和一个延迟的长度的 ENTITY Subsystem1 IS PORT(clk: IN std_logic;reset: IN std_logic;enb: IN std_logic;In1: IN std_logic;——ufix1 Out1: OUT std_logic——ufix1);Subsystem1结束;rtl OF Subsystem1 IS——Signals SIGNAL Delay_out1: std_logic;——ufix1信号Delay1_out1: std_logic;——ufix1信号Delay2_out1: std_logic;——ufix1信号Delay3_out1: std_logic; -- ufix1 SIGNAL Delay4_out1 : std_logic; -- ufix1 |

将多个输入信号组合成向量信号Mux块。 |

这个示例演示了使用Mux块结合 ENTITY子系统IS PORT(In1: IN std_logic;——ufix1 Out1: OUT std_logic_vector(0到3)——ufix1 [4];终端子系统;system IS - Signals SIGNAL Mux_out1: std_logic_vector(0 TO 3);——ufix1 [4] |

使用一个位Concat块来组合输入信号。这个例子通过连接演示了为这个块生成的代码 ENTITY子系统IS PORT(In1: IN std_logic;——ufix1 Out1: OUT std_logic_vector(3 DOWNTO 0)——ufix4;终端子系统;子系统IS的结构rtl——Signals SIGNAL Bit_Concat_out1: unsigned(3 DOWNTO 0)——ufix4 |

使用一个常数块生成矢量信号。 |

这个示例演示了使用常数块生成的向量 ENTITY Subsystem2 IS PORT(Out1: OUT std_logic_vector(0 TO 3)——boolean [4]);终端子系统;struct rtl OF Subsystem2 IS——Signals SIGNAL Constant_out1: std_logic_vector(0 TO 3);——布尔[4] |

使用一个多路分配器块,后跟位Concat块后常数块。这个示例演示了将这种建模技术应用于向量时生成的代码 ENTITY Subsystem2 IS PORT(Out1: OUT std_logic_vector(3 DOWNTO 0)——ufix4);Subsystem2结束;struct rtl OF Subsystem2 IS——Signals SIGNAL Constant_out1: std_logic_vector(0 TO 3);——boolean [4] SIGNAL Constant_out1_0: std_logic;信号常量out1_1: std_logic;信号常量out1_2: std_logic;信号常量out1_3: std_logic;SIGNAL Bit_Concat_out1: unsigned(3 DOWNTO 0);——ufix4] |