在Zynq工作流中使用axis - stream接口部署模型

本示例展示了如何使用AXI4-Stream接口在Zynq®硬件上的处理器和FPGA之间实现高速数据传输。

开始之前

要运行此示例,您必须安装并设置以下软件和硬件:

HDL Coder™支万博1manbetx持包Xilinx®Zynq平台

嵌入式Coder®支持包Xili万博1manbetxnx Zynq平台

Xilinx Vivado®设计套件,支持的版本列在万博1manbetxHDL语言支持和支持的第三万博1manbetx方工具和硬件

Zedboard

要设置Zedboard,请参阅设置Zynq硬件和工具节。着眼于Xilinx Zynq平台.

简介

这个例子展示了如何:

使用简化的流协议对流算法建模。

使用AXI4-Stream接口生成HDL IP核。

将生成的IP核集成到具有DMA控制器的Zedboard参考设计中。

使用AXI4-Stream驱动程序块生成运行在ARM处理器上的C代码。

上图是Zynq平台上处理器和FPGA结构之间流数据传输的高层架构图。通常,AXI4-Stream接口与DMA控制器一起使用,以将大量数据从处理器传输到FPGA。在软件端,数据通常表示为矢量数据。DMA控制器从内存中读取矢量数据,并通过AXI4-Stream接口将其“流”到FPGA IP。“流”过程为每个样本发送一个数据元素,这意味着流算法在FPGA IP中的数据路径使用标量数据类型。

FPGA IP还可以包括用于控制信号或参数调优的AXI4-Lite接口。与AXI4-Lite接口相比,AXI4-Stream接口传输数据的速度要快得多,因此更适合于算法的数据路径。

除了与处理器连接外,具有AXI4-Stream接口的FPGA IP还可以与具有AXI4-Stream接口的其他IP连接,在FPGA内部传输数据。

用简化流协议建模流算法

假设我们想在Zynq上部署一个简单的对称FIR滤波器。我们想在FPGA上实现滤波器。ARM处理器生成源数据,并通过AXI4-Stream接口将其传输到FPGA。

让我们从sfir_fixed模型。

open_system (“sfir_fixed”) set_param (“sfir_fixed”,“SimulationCommand”,“更新”)

注意,这个模型的数据路径(从x_in来y_out)正在处理标量输入数据,这适用于流接口。

为了支持数据从软件传输到过滤器算法,我们需要将数据路径端口映射到AXI4-Stream接口。AXI4-Stream接口包含数据(数据)和控制信号,例如数据有效(有效的)、背压(准备好了)和数据边界(TLAST).

AXI4-Stream IP核生成特性至少需要数据和有效的在DUT中建模的信号。的数据信号是通过接口发送的主要有效载荷。的有效的信号表示数据信号有效。其他控制信号可选。

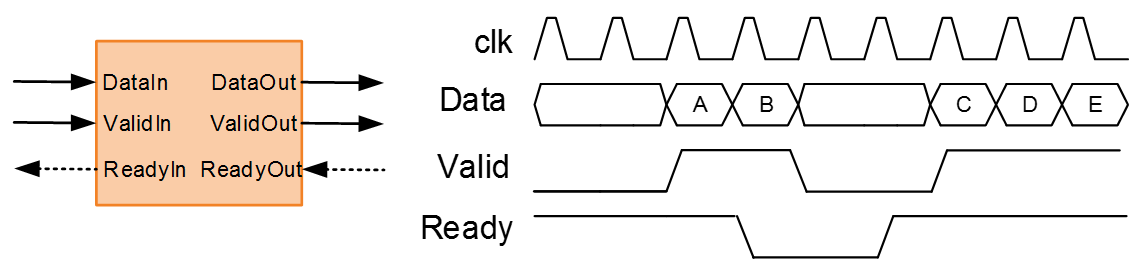

注意:对于IP核生成,Data和Valid遵循简化的流协议。您不需要对完整的AXI4-Stream协议建模,因为它更复杂。HDL Coder在HDL IP核中自动生成流媒体接口模块,将简化的流媒体协议转换为完整的AXI4-Stream协议。如下图所示,协议很简单:只要Data信号有效,valid信号也必须被断言。

为了映射sfir_fixed算法来简化流协议,一个有效的需要添加信号。要添加有效的信号传递给您的模型,我们推荐以下建模模式:

将算法子系统转换为启用的子系统。

增加一个输入控制端口,

Valid_In,输出控制端口,Valid_Out.使用

Valid_In来驱动算法子系统的启用端口和Valid_Out.

在这种模式中,输入流通道和输出流通道都遵循简化的流协议。

现在,让我们看一下示例模型。

open_system (“hdlcoder_sfir_fixed_stream”);

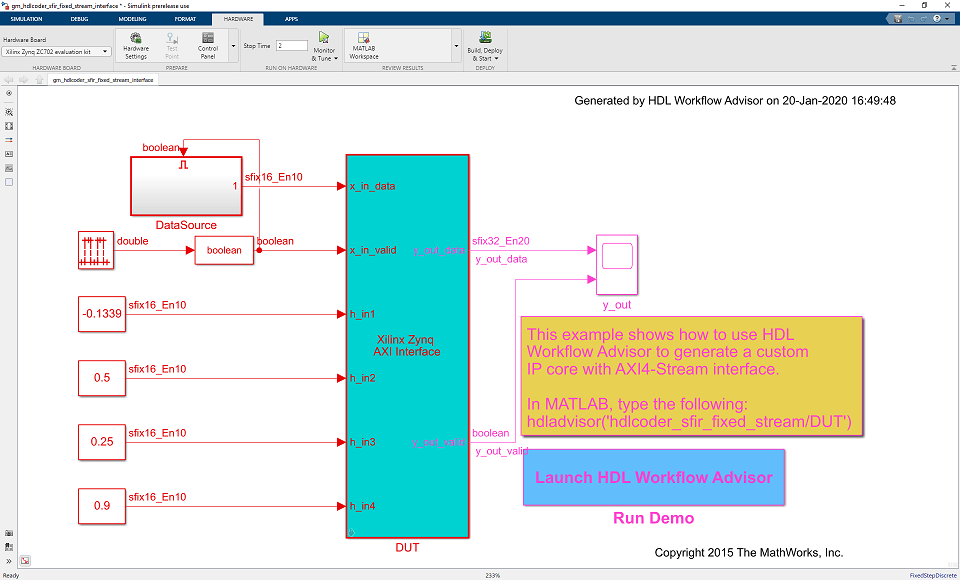

子系统DUT是针对FPGA结构的硬件子系统。在这个子系统中,symmetric_fir子系统代表滤波算法。输入端口,x_in_data和x_in_valid,输出端口,y_out_data和y_out_valid,为过滤器的数据路径端口。其他输入端口,如h_in1,是调整过滤器参数的控制端口。

该模型遵循简化流协议的建模模式。的symmetric_fir子系统是启用的子系统。输入控制信号,x_in_valid,控制symmetric_fir子系统的使能端口,同时驱动输出控制信号,y_out_valid.

使用AXI4-Stream IP核生成,您可以选择对其他流控制信号建模。例如,你可以模拟背压信号,准备好了.AXI4-Stream接口以主/从模式通信,主设备向从设备发送数据。的准备好了信号是从设备到主设备的背压信号,用来指示从设备是否可以接受新的数据。如下图所示准备好了当从设备可以接受新数据时,信号被断言。当从设备不能再接受新数据时,它需要去断言准备好了信号。当主设备看到准备好了信号被解除,它最多在一个采样后停止数据传输。这一样本量是协议中规定的。

注:该图根据简化的流协议说明了数据、有效和就绪信号之间的关系。当你运行IP核生成该代码生成器在HDL IP核中添加了一个流接口模块,将简化协议转换为完整的流协议。

例如,您可以使用准备好了信号,当你使用FIFO块来收集一帧传入的流数据,然后用你的算法处理。在数据处理期间,您将撤销准备好了信号,以防止进一步传入数据。

使用AXI4-Stream接口生成HDL IP核

接下来,我们启动HDL Workflow Advisor并使用Zynq硬件-软件协同设计工作流将该设计部署到Zynq硬件上。有关更详细的分步指南,可以参考着眼于Xilinx Zynq平台的例子。

1.在MATLAB命令窗口中使用以下命令设置Xilinx Vivado合成工具路径。运行该命令时,请使用自己的Vivado安装路径。

hdlsetuptoolpath('ToolName', 'Xilinx Vivado', 'ToolPath', 'C:\Xilinx\Vivado\2019.1\bin\ Vivado .bat')

2.从DUT子系统启动HDL Workflow Advisor,hdlcoder_sfir_fixed_stream / DUT.目标接口设置已经保存在这个示例模型中,因此将自动加载Task 1.1和1.2中的设置。有关在模型中保存目标接口设置的详细信息,请参阅在模型中保存目标硬件设置的例子。

在任务1.1中IP核生成为目标工作流程,Zedboard为目标平台.在Task 1.2中默认系统带有AXI4-Stream接口为参考设计,以及目标平台接口表加载如下图所示。数据路径端口,x_in_data,x_in_valid,y_out_data,y_out_valid,映射到AXI4-Stream接口,以及控制参数端口,例如h_in1,映射到AXI4-Lite接口。

AXI4-Stream接口以主/从模式通信,主设备向从设备发送数据。因此,如果数据端口是输入端口,请将其分配给AXI4-Stream奴隶接口,如果数据端口是输出端口,则将其分配给AXI4-Stream主接口。

3.右键单击任务3.2,生成RTL代码和IP核,并选择运行到选定任务来生成IP核。您可以在生成的IP核报告中找到IP核的寄存器地址映射和其他文档。

将IP集成到AXI4-Stream兼容参考设计中

接下来,在HDL Workflow Advisor中,我们运行嵌入式系统集成将生成的HDL IP核部署到Zynq硬件上。

1.运行任务4.1,创建项目.该任务将生成的IP核插入默认系统带有AXI4-Stream接口参考设计。本参考设计包含Xilinx的AXI DMA IP处理处理器到FPGA fabric的数据流。如第一个图或IP核报告中所示,数据从ARM处理系统通过DMA控制器和AXI4-Stream接口发送到生成的HDL FIR滤波器IP核。过滤IP核的输出然后被发送回处理系统。

2.可选地单击Result窗格中的链接来打开生成的Vivado项目。在Vivado工具中,单击开放式体块设计查看Zynq设计框图,包括生成的HDL IP核、AXI DMA控制器和处理器。

3.在HDL Workflow Advisor中,运行其余任务以生成软件接口模型,并构建和下载FPGA比特流。

使用AXI4-Stream驱动程序块生成ARM可执行文件

在任务4.2中生成软件接口模型,生成软件接口模型,如下图所示。

虽然在软件接口模型中自动生成了AXI4-Lite驱动程序,但不能自动生成AXI4-Stream驱动程序块。原因是AXI4-Stream驱动程序块希望连接到软件端的矢量端口,但是x_in_dataDUT端口为标量端口。

1.在从软件接口模型生成代码之前:

添加AXI4-Stream IIO读取和AXI4-Stream IIO写入司机从万博1manbetxSimulink Library浏览器->Xilinx Zynq平台嵌入万博1manbetx式编码器支持包图书馆。

使用矢量数据源来驱动x_in_data端口。

连接x_in_data端口到驱动程序块。

双击AXI4-Stream IIO写入block并将Timeout设置为0而不是inf。如下所示。

5.属性的优先级AXI4-Stream IIO写入Block到1,以确保在读取之前进行写操作。要设置优先级,右键单击块并打开属性,将优先级设置为1。如下所示。

6.现在双击AXI4-Stream IIO读取设置帧大小为100,采样时间为Ts,超时时间为10。如下所示。

7.优先级AXI4-Stream IIO读取块不需要设置。仅将写块的优先级设置为1就可以确保先写后读。

对于本例,提供了更新的软件接口模型:hdlcoder_sfir_fixed_stream_sw.slx.在这个模型中使用了一个包含100个数据元素的矢量数据源,它连接到AXI4-Stream DMA驱动程序块。这意味着对于每个处理器采样时间,DMA控制器将通过AXI4-Stream接口将100个32位数据样本流到HDL IP核,并接收100个32位流数据样本。

2.配置和构建外部模式的软件接口模型:

在生成的模型中,单击Hardware窗格并转到硬件设置打开配置参数对话框。

选择解算器并将“停止时间”设置为“inf”。

在Hardware窗格中,单击监视和调优按钮。

单击运行按钮。Embedded Coder构建模型,下载ARM可执行文件到Zedboard硬件,执行它,并将模型连接到运行在Zedboard硬件上的可执行文件。

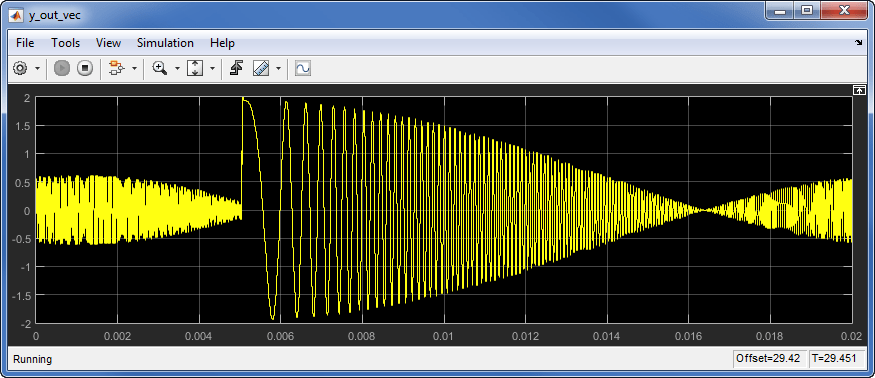

3.现在,设计的硬件和软件部分都运行在Zynq硬件上。ARM处理器通过DMA控制器和AXI4-Stream接口将源数据发送到FPGA IP。ARM处理器从FPGA IP接收过滤结果数据,并通过外部模式将结果数据发送给Simulink。万博1manbetx在时间范围上观察Zynq硬件的FIR滤波器IP核的输出y_out.

4.在软件接口模型中调优FIR滤波器参数,并观察在调优参数时FIR滤波器的输出如何变化。参数值通过外部模式和AXI4-Lite接口发送到Zynq硬件。