开始瞄准Zynq UltraScale+MPSoC平台

此示例演示如何使用硬件-软件协同设计工作流在Xilinx®Zynq®UltraScale+MPSoC上以不同频率闪烁LED。

介绍

这个例子是一个逐步指导,帮助您使用HDL编码器™ 用于生成自定义HDL IP核心的软件,该核心使Xilinx Zynq UltraScale+MPSoC ZCU102评估工具包上的LED闪烁,并演示如何使用嵌入式编码器生成在ARM®处理器上运行的C代码,以控制LED闪烁频率。

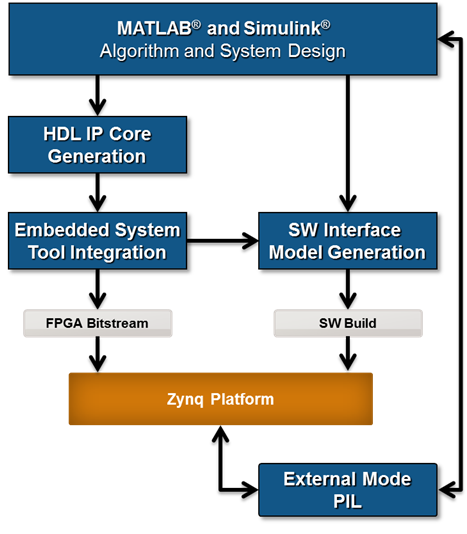

您可以使用MATLAB®和Simulink®设计万博1manbetx,模拟和验证您的应用程序,执行具有算法的What-If场景,并优化参数。然后,您可以通过决定可编程逻辑执行哪些系统元素,以及将哪些系统元素进行准备在Xilinx Zynq UltraScale + MPSoc上的硬件和软件实现的设计,以及哪些系统元素将在ARM Cortex-A53上运行。

使用此示例中显示的导向工作流程,使用HDL编码器自动生成可编程逻辑的HDL代码,使用嵌入式编码器生成用于ARM处理器的C代码,并在Xilinx Zynq UltraScale + MPSOC平台上实现设计。

在此工作流中,您将执行以下步骤:

设置Xilinx Zynq UltraScale+MPSoC ZCU102硬件和工具。

为硬件和软件实现对设计进行分区。

使用HDL Workflow Advisor生成HDL IP核心。

将IP核心集成到Xilinx Vivado项目中并编程Xilinx Zynq UltraScale + MPSoC硬件。

生成软件接口模型。

从软件界面模型生成C代码,并在ARM Cortex-A53处理器上运行它。

使用外部模式从Zynq硬件调整参数并捕获结果。

要求

Xilinx Vivado设计套件,带有支持的版本万博1manbetxHDL编码器文档

Xilinx Zynq UltraScale+MPSoC ZCU102评估套件

Xilinx Zyn万博1manbetxq平台的HDL编码器支持包

Xilinx Zynq平台的嵌万博1manbetx入式编码器支持包

设置Xilinx Zynq UltraScale+MPSoC硬件和工具

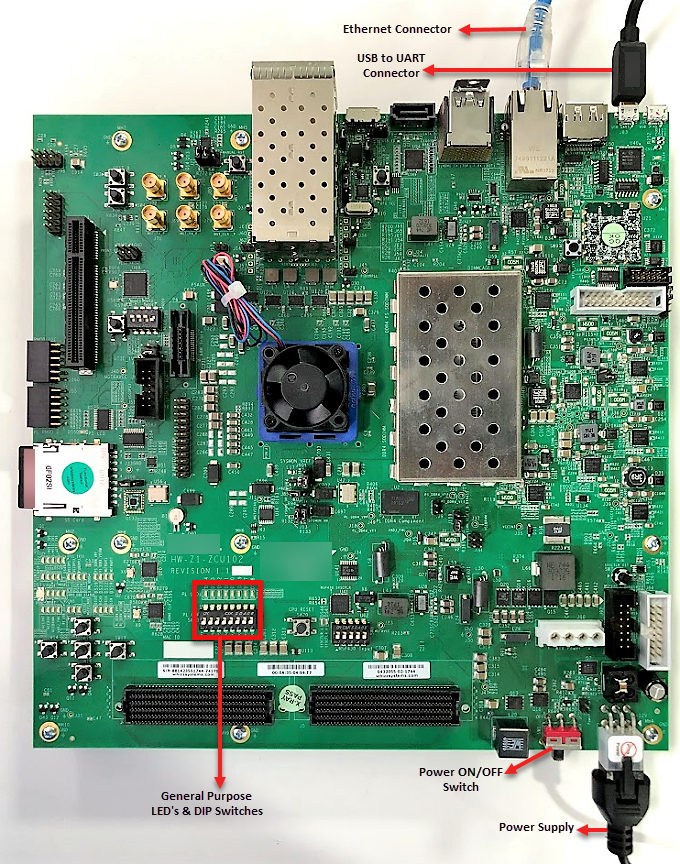

1.如下图所示,设置Xilinx Zynq UltraScale+MPSoC ZCU102评估工具包。要了解有关ZCU102硬件设置的更多信息,请参阅Xilinx文档.

1.1.确保SW6切换设置如下图所示,因此您可以从SD卡启动Linux。

1.2使用微型USB电缆将计算机连接到ZCU102的USB UART接口。确保正确安装了USB设备驱动程序,如Silicon Labs CP210x USB到UART网桥的驱动程序。如果没有,请联机搜索并安装驱动程序。

1.3使用以太网电缆将Xilinx Zynq UltraScale+MPSoC板连接到计算机。

2.如果您还没有,请为Xilinx Zynq平台安装HDL编码器和嵌入式编码器支持软件万博1manbetx包。

2.1关于MATLAB家选项卡中的环境部分,单击“加载项”>“管理加载项”。

2.2在附加模块管理器中,单击Xilinx Zynq平台嵌入式编码器支持包的设置按钮,开始硬件设置过程。万博1manbetx

3.确保您使用的是Xilinx Zynq平台嵌入式编码器支持包提供的SD卡映像。万博1manbetx

4.通过在MATLAB命令窗口中输入以下命令设置zynq硬件连接:

h = zynq.

这个Zynq.函数通过COM端口登录到硬件并运行命令命令获取板的IP地址。此功能还测试以太网连接。

5.您可以选择使用PuTTY之类的程序,使用以下配置测试串行连接™. 波特率:115200; 数据位:8.;停止位:1.;平价:没有任何;流量控制:没有任何. 重启MPSoC板时,您应该能够在串行控制台上观察Linux引导日志。在使用之前,必须先关闭此串行连接Zynq.再次发挥作用。

6.在MATLAB命令窗口中使用以下命令设置Xilinx Vivado合成刀具路径。运行命令时,请使用自己的Vivado安装路径。

hdlsetuptoolpath('toolname','xilinx vivado','toolpath','c:\ xilinx \ vivado \ 2019.1 \ bin \ vivado.bat');

为硬件和软件实现对设计进行分区

Zynq硬件软件共同设计工作流程的第一步是决定设计的哪些部分用于在可编程逻辑上实现,以及在ARM处理器上运行的部分。

将要在可编程逻辑上实现的所有块分组到一个原子子系统中。这个原子子系统是硬件-软件分区的边界。该子系统内的所有模块将在可编程逻辑上实现,该子系统外的所有模块将在ARM处理器上运行。

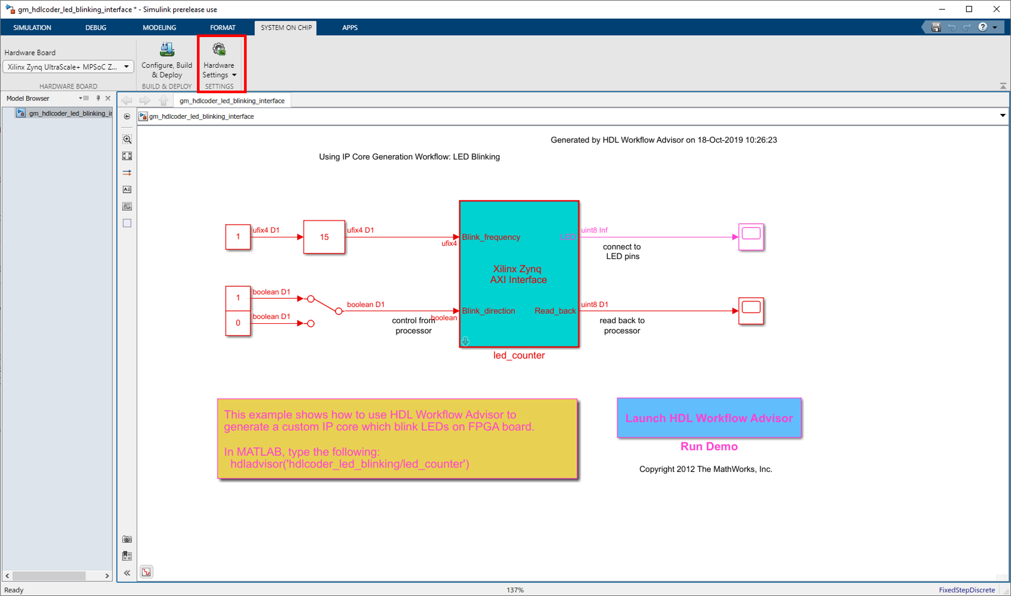

在本例中,子系统发光二极管计数器是硬件子系统。它模拟了一个计数器,使FPGA板上的LED闪烁。两个输入端口,闪烁频率和blink_direction.,是确定LED闪烁频率和方向的控制端口。子系统外部的所有块发光二极管计数器用于软件实现。

在Si万博1manbetxmulink中,您可以使用滑动增益或手动开关块调整硬件子系统的输入值。在嵌入式软件中,这意味着ARM处理器通过写入AXI接口可访问寄存器来控制生成的IP内核。硬件子系统的输出端口,发光二极管,连接LED硬件。输出端口,回读,可用于将数据读回处理器。

Open_System(“hdlcoder\u led灯闪烁”);

使用HDL Workflow Advisor生成HDL IP核心

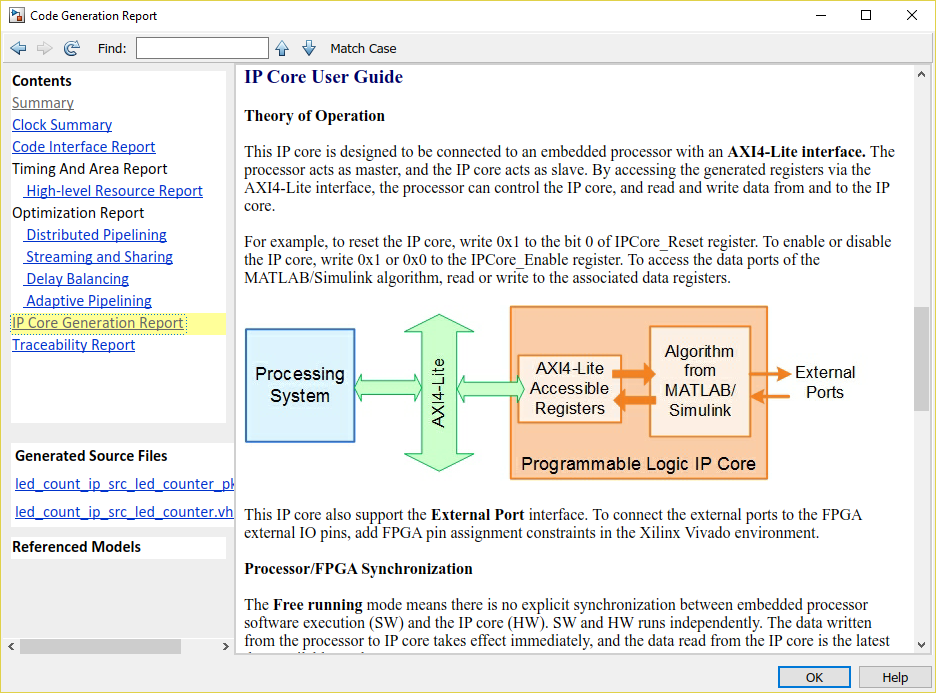

使用HDL workflow Advisor中的IP核心生成工作流,您可以从Simulink模型自动生成可共享和可重用的IP核心模块。生成的IP核设计为连接到FPGA设备上的嵌入式处理器。HDL编码器从Simulink块生成HDL代码,还为连接IP核与嵌入式处理器的AXI接口逻辑生成HDL代码。HD万博1manbetxL编码器将所有生成的文件打包到IP核心文件夹中。然后,您可以在Xilinx Vivado环境中将生成的IP核与更大的FPGA嵌入式设计集成。

1.启动IP核心生成工作流。

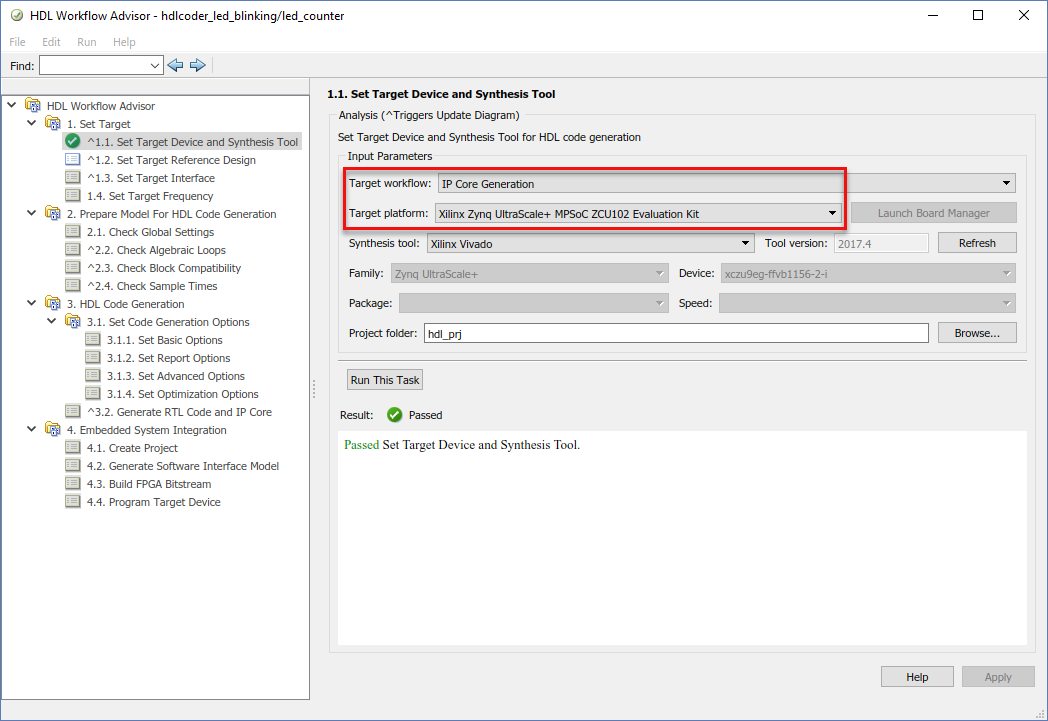

1.1.从中打开HDL工作流顾问hdlcoder_led_blinking / led_counter.通过右键单击发光二极管计数器子系统及其选择硬体描述语言程式码>HDL工作流程顾问.

1.2.在里面设定目标>设置目标设备和合成工具任务,for.目标工作流选择IP核心生成.

1.3.对于目标平台选择Xilinx Zynq UltraScale+MPSoC ZCU102评估套件. 如果没有此选项,请选择获取更多打开支持包安装程序。在支万博1manbetx持包安装程序中,选择Xilinx Zynq Platform并按照支持包安装程序提供的说明完成安装。

1.4.点击运行此任务运行设置目标设备和合成工具任务

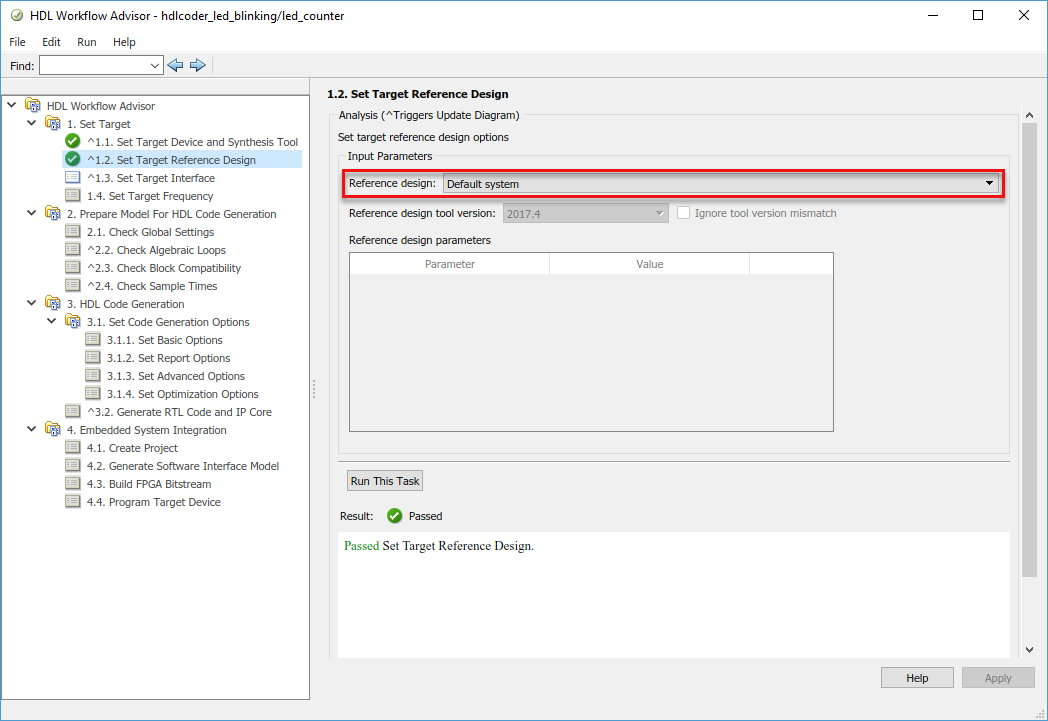

1.5在里面设定目标>设定目标参考设计任务,选择默认系统.

1.6。点击运行此任务运行设定目标参考设计任务

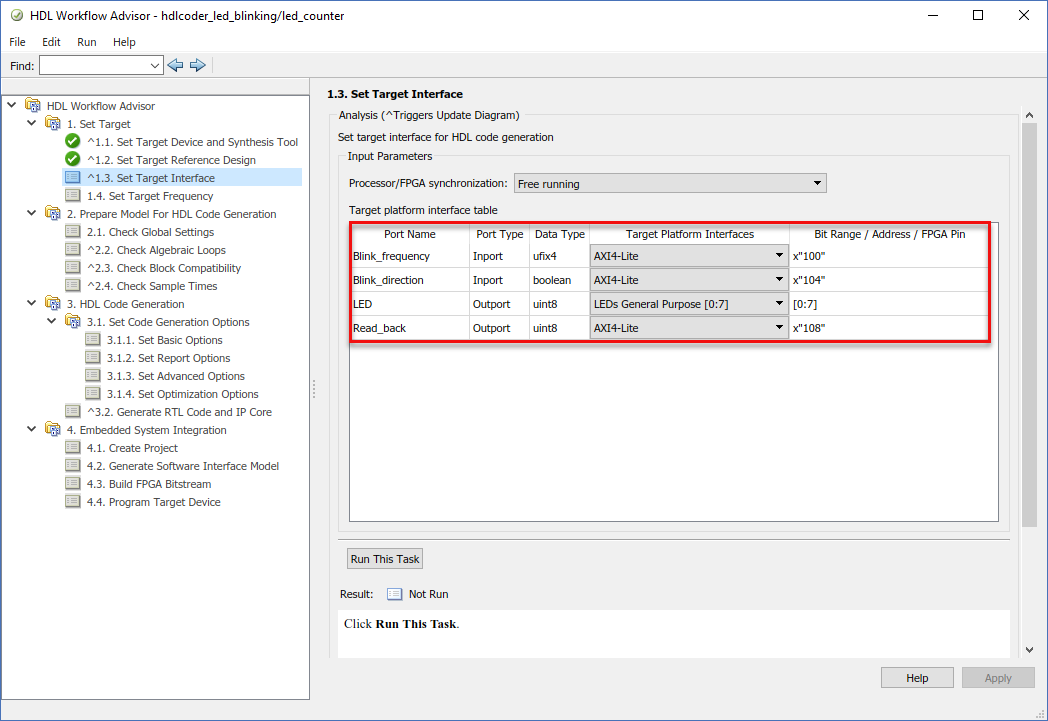

2.配置目标接口。

将DUT中的每个端口映射到其中一个IP核心目标接口。在此示例中,输入端口闪烁频率和blink_direction.映射到AXI4 Lite接口,因此HDL编码器为它们生成AXI接口可访问寄存器。这个发光二极管输出端口映射到外部接口,通用发光二极管[0:7],它连接到Zynq板上的LED硬件。

2.1在里面设定目标>设置目标接口任务,选择AXI4-Lite对于闪烁频率,blink_direction., 和回读.

2.2选择通用发光二极管[0:7]对于发光二极管.

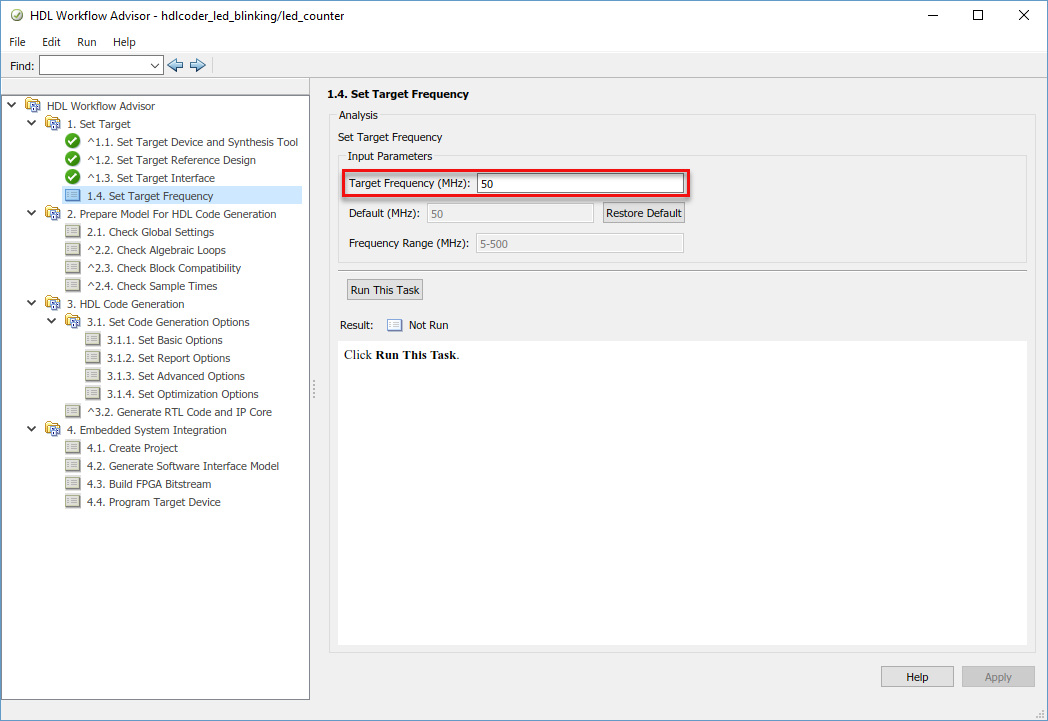

2.3在里面设定目标>设定目标频率任务,选择目标频率为50 MHz.

3.生成IP核心。

要生成IP核心,请右键单击生成RTL代码和IP核任务并选择运行到所选任务.

4.生成并查看IP核心报告。

生成自定义IP核心后,IP核心文件位于知识产权核项目文件夹中的文件夹。与自定义IP核心一起生成HTML自定义IP核心报告。该报告描述了生成的自定义IP核心的行为和内容。

将IP核心与Xilinx Vivado环境集成

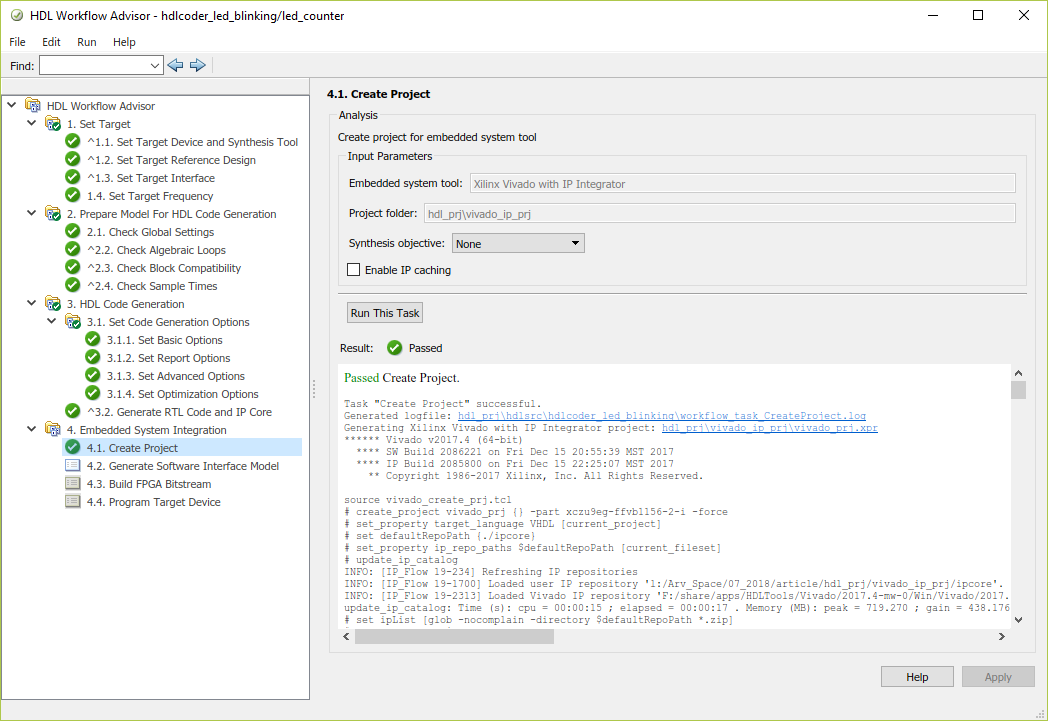

在工作流程的这一部分中,将生成的IP核心插入嵌入式系统参考设计,生成FPGA位流,并将位流下载到Zynq硬件。

参考设计是一个预定义的Xilinx Vivado项目。它包含Xilinx软件将您的设计部署到Zynq平台所需的所有元素,但您生成的自定义IP核心和嵌入式软件除外。

1.要与Xilinx Vivado环境集成,请选择创建项目任务嵌入式系统集成,然后单击运行此任务. 生成具有IP Integrator嵌入式设计的Xilinx Vivado项目,并在对话框窗口中提供指向该项目的链接。您可以选择打开项目进行查看。

2.如果您有嵌入式编码器许可证,您可以在下一个任务中生成软件接口模型,生成软件接口模型. 软件接口模型的详细信息将在本示例的下一节“生成软件接口模型”中解释。

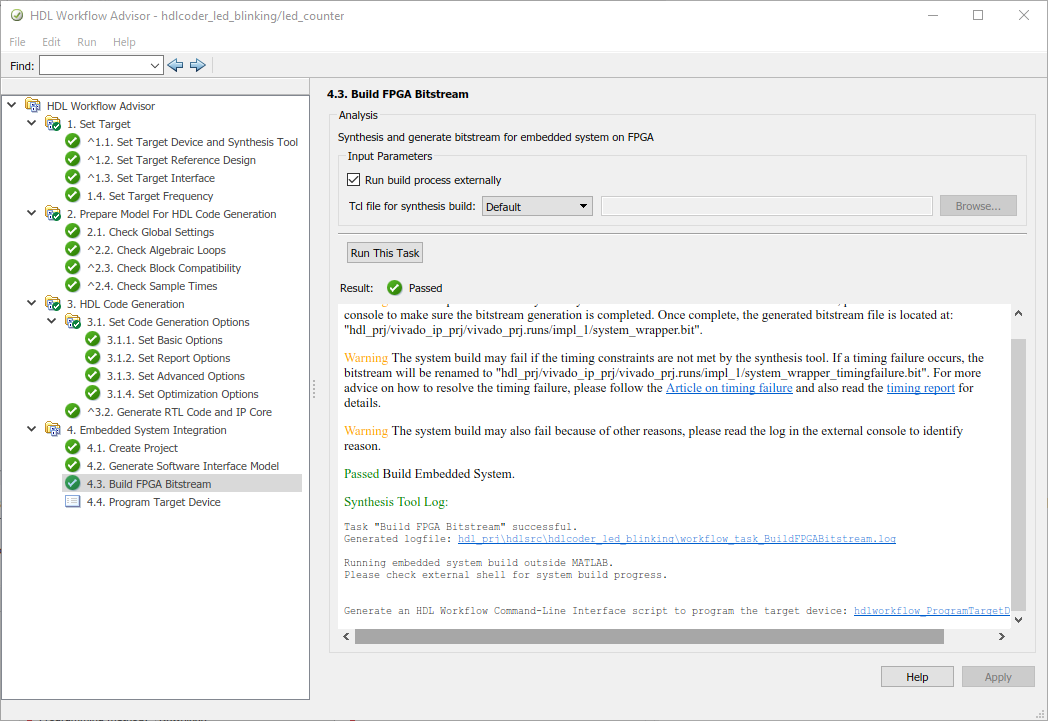

3.在构建FPGA比特流任务确保从外部运行构建过程选项检查,因此Xilinx综合工具将在Matlab的单独进程中运行。等待综合工具过程完成在“外部命令”窗口中运行。

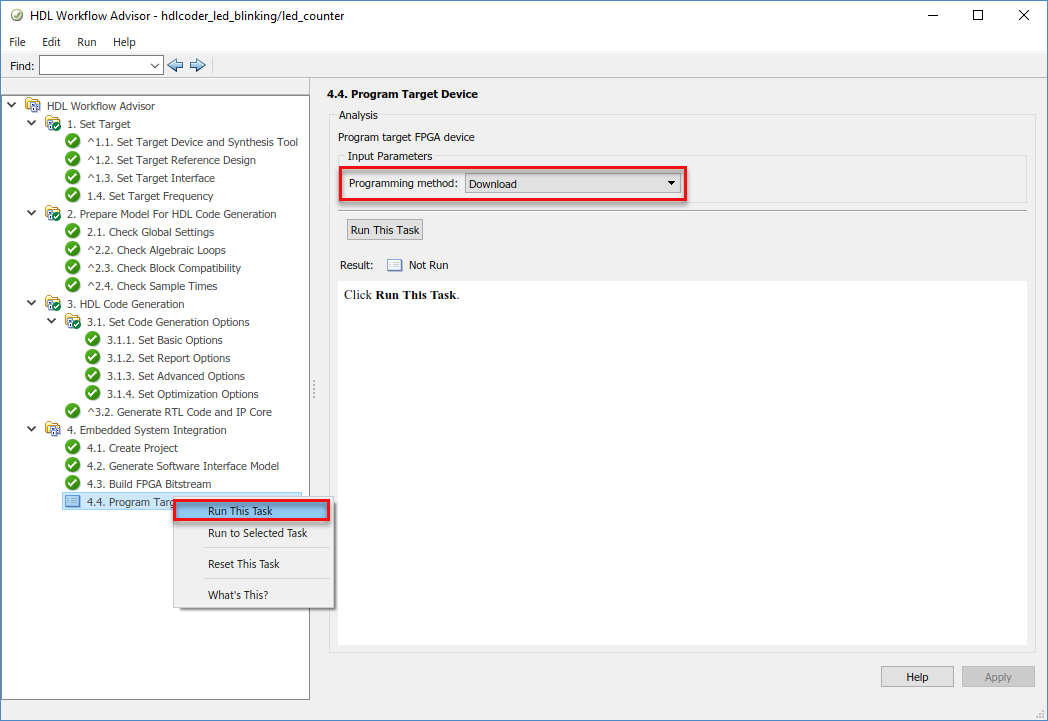

4.生成比特流后,选择程序目标设备任务选择下载对于编程方法将FPGA比特流下载到Xilinx Zynq UltraScale+MPSoC板上的SD卡上,这样当您关闭Zynq板电源时,您的设计将自动重新加载。点击运行此任务对Zynq硬件进行编程。

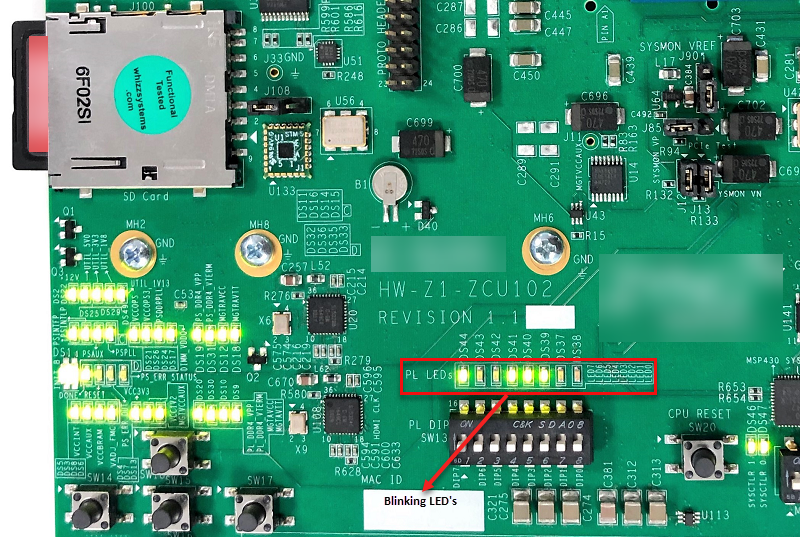

编程FPGA硬件后,Xilinx Zynq UltraScale+MPSoC ZCU102板上的LED开始闪烁。

接下来,您将生成在ARM处理器上运行的C代码,以控制LED闪烁频率和方向。

生成软件界面模型

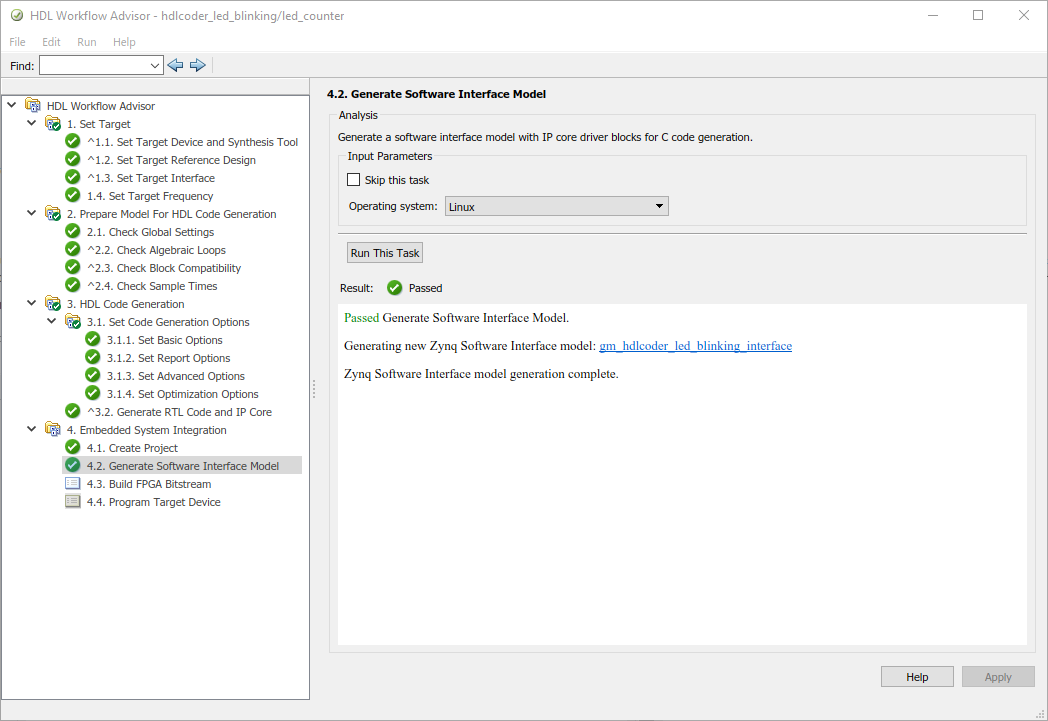

在HDL Workflow Advisor中,生成IP核心后,可以在步骤4.1中创建vivado项目,也可以在嵌入式系统集成>生成软件接口模型任务

软件界面模型包含在软件中运行的设计部分。它包括HDL子系统之外的所有块,并用AXI驱动程序块替换HDL子系统。如果您拥有嵌入式编码器许可证,您可以从软件接口模型自动生成嵌入式C代码,构建它,并在ARM处理器上的Linux上运行可执行文件。生成的嵌入式软件包括从AXI驱动程序块生成的AXI驱动程序代码,用于控制HDL IP核心。

运行生成软件接口模型任务,并查看是否生成了新模型。“任务”对话框显示指向模型的链接。

在生成的软件界面模型中,“LED_Counter”子系统被替换为AXI驱动程序块,该驱动程序块在ARM处理器和FPGA之间生成接口逻辑。

在Zynq ZCU102硬件上运行软件接口模型

在工作流的这一部分中,您将配置生成的软件接口模型,自动生成嵌入式C代码,并在Zynq硬件的ARM处理器上以外部模式运行您的模型。

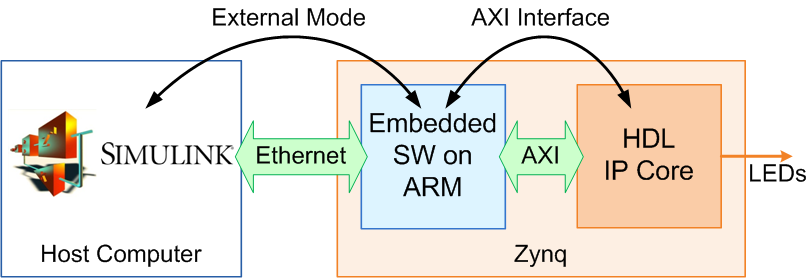

当您在原型设计和开发算法时,在运行硬件时监视和调整算法是有用的。Simulink中的外部模式功能可实现此功能。万博1manbetx在此模式下,您的算法首先将其部署到Zynq硬件中的ARM处理器,然后通过以太网连接与主机上的Simulink模型连接。万博1manbetx

Simulink模型的主要作用是调整和监控万博1manbetx硬件上运行的算法。由于ARM处理器通过AXI接口连接到HDL IP核,因此您可以使用外部模式调整参数,并从FPGA捕获数据。

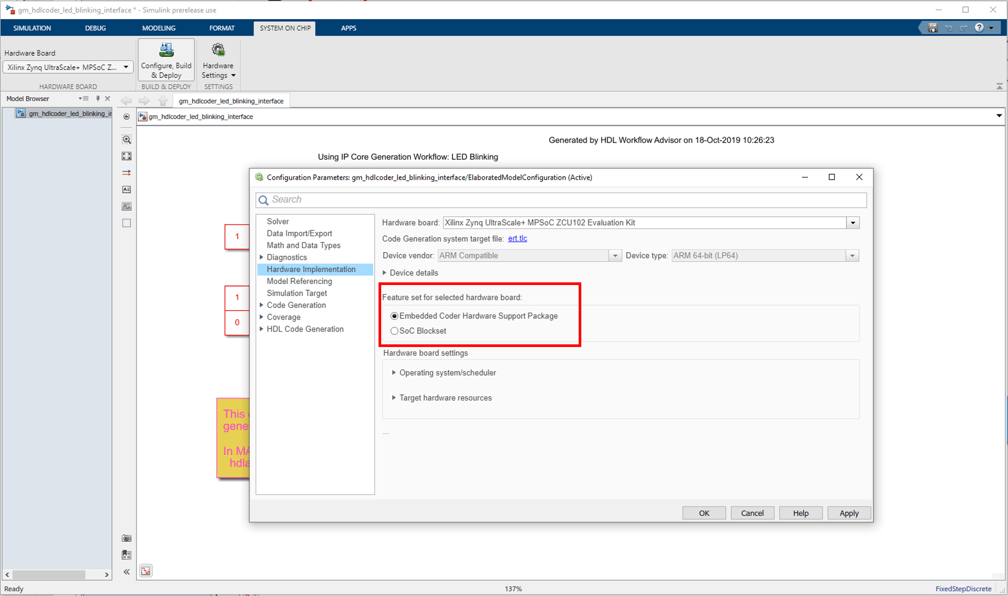

在生成的模型中,单击“硬件”窗格并转至硬件设置打开配置参数对话框。

选择求解器并将“停止时间”设置为“inf”。

选择硬件实现并将“所选硬件板的功能集”设置为“嵌入式编码器硬件支持包”。万博1manbetx

从硬件菜单中,单击监视和调谐模型工具臂上的按钮在外部模式下在Zynq UltraScale + MPSoC ZCU102硬件中运行您的臂架处理器。嵌入式编码器构建模型,将ARM可执行到Xilinx Zynq UltraScale + MPSoC ZCU102硬件,执行它,并将模型连接到Zynq硬件上的可执行文件运行。

双击滑动增益块更改滑块增益值,观察Zynq硬件上LED阵列闪烁频率的变化。双击手动开关块以切换闪烁LED的方向。

双击连接到的范围回读输出端口,观察FPGA IP核的输出数据是否被捕获并发送回Simulink示波器。万博1manbetx

完成更改模型参数时,单击停止模型上的按钮。

总结

此示例显示了软硬件协同设计工作流如何帮助将MATLAB和Simulink设计自动部署到Xilinx Zynq Ultrascale+MPSoC。通过迭代工作流,您可以探索划分和部署设计的最佳方法。万博1manbetx

下图显示了您在此示例中完成的工作流的高级图片。要了解有关硬件和软件共同设计工作流程的更多信息,请参阅HDL编码器文档.