高密度脂蛋白部分延迟(产)过滤器

这个例子演示了如何生成HDL代码部分延迟(产)过滤时间复苏在数字调制解调器。法罗滤波器结构提供了变量部分延迟下游符号采样之前接收到的数据流。这种特殊的冷杉滤波器结构允许简单的处理滤波器系数由一个有效的多项式插值公式实现提供变量部分重采样。

在一个典型的数字调制解调器应用程序,略微重新取样数据输出从法罗滤波器传递象征取样器和可选的载波恢复。这个完整的应用程序的更多细节请参考“定时恢复使用固定利率重采样”仿真软件®和通信工具箱™。万博1manbetx

设计滤波器

设计一个分数延迟滤波器使用立方拉格朗日插值方法中,首先创建一个规范对象过滤器的订单3和任意分数延迟的0.3。接下来,创建一个法罗过滤器对象高清,使用规范的对象的设计方法和参数拉格朗日。这种方法也被称为属性FilterStructure和它的价值fd。你可以调查的细节过滤器对象高清通过使用信息命令。

fDelay = 0.3;filtdes = fdesign.fracdelay (fDelay,“N”3);高清=设计(filtdes,“拉格朗日”,“FilterStructure”,“farrowfd”);信息(高清)

离散时间冷杉法罗滤波器(真正的)- - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - -滤波器结构:法罗分数延迟滤波器长度:4稳定:是的线性相位:没有算术:翻倍

法罗的分数延迟滤波器可调,可以改变导致不同程度的反应。你可以看到这个通过创建一组过滤器预先设计滤波器的副本高清每个不同的fracdelay值。

h = repmat(高清1 10);% preallocating大小为d = 0:9 h (d + 1) = (Hd)复印件;%创建独特的过滤器对象h (d + 1) .fracdelay = d / 10;结束fvtool (h)

fvtool (h,“分析”,“PhaseDelay”)

数字转换过滤器

设置过滤器对象到定点模式量化。假设八位输入数据与八位系数和six-bit分数延迟。修改定点数据字长度和相应部分的长度。的CoeffFracLength属性设置自动因为系数自动定量设置在默认的属性CoeffAutoscale。关掉FDAutoScale并设置FDFracLength6、允许部分延迟要代表的范围在0到1。

高清。算术=“固定”;高清。InputWordLength = 8;高清。InputFracLength = 7;高清。CoeffWordLength = 8;高清。FDWordLength = 6;高清。FDAutoScale = false; Hd.FDFracLength = 6;

从量化滤波器生成HDL代码

从正确的量子化的过滤器,您可以生成使用硬件描述语言(VHDL)或Verilog代码generatehdl命令。您将创建一个临时工作目录,然后使用generatehdl命令使用适当的属性-值。后生成HDL代码使用硬件描述语言(VHDL)为开发房地产在这种情况下,您可以在编辑器中打开生成的硬件描述语言(VHDL)文件点击超链接显示在命令行显示消息。

workingdir = tempname;generatehdl(高清“名字”,“hdlfarrow”,…“开发”,硬件描述语言(VHDL)的,…“TargetDirectory”,workingdir);

# # #开始硬件描述语言(VHDL)过滤器的代码生成过程:hdlfarrow # # #生成:/ tmp / Bdoc23a_2213998_478575 / tp08579f40_c4ff_4603_9067_66d6414b7e52 / hdlfarrow。vhd # # # # # #开始代hdlfarrow VHDL的实体开始代hdlfarrow硬件描述语言(VHDL)架构# # #成功完成硬件描述语言(VHDL)过滤器的代码生成过程:hdlfarrow # # # HDL延迟是2样本

产生高密度脂蛋白试验台

验证HDL代码,您可以生成一个高密度脂蛋白试验台模拟使用高密度脂蛋白HDL代码模拟器。试验台将验证的结果HDL代码与MATLAB®的结果过滤器命令。过滤器的刺激输入filter_in港口和分数延迟filter_fd端口可以使用属性来指定TestbenchStimulus,TestbenchUserStimulus和TestbenchFracDelayStimulus。

预定义的过滤器输入的刺激filter_in端口可以指定输入数据刺激使用属性TestbenchStimulus与其他滤波器结构。您可以指定自己的刺激输入数据通过使用属性TestbenchUserStimulus并通过MATLAB向量的值。

您可以指定分数延迟刺激使用属性TestbenchFracdelayStimulus。一个向量之间的两倍0和1通过指定要么是自动生成的吗RandSweep或RampSweep。默认行为是提供一个分数延迟刺激的一组常数fracdelay过滤器对象的价值。

下面的命令指定了输入的刺激尖声地说,分数延迟矢量被设置为一个常数0.3所有的模拟时间。这是默认行为的时候TestbenchFracDelayStimulus属性没有设置。

generatehdl(高清“名字”,“hdlfarrow”,…“GenerateHDLTestbench”,“上”,…“TestBenchName”,“hdlfarrow_default_tb”,…“开发”,硬件描述语言(VHDL)的,…“TargetDirectory”,workingdir);

# # #开始硬件描述语言(VHDL)过滤器的代码生成过程:hdlfarrow # # #生成:/ tmp / Bdoc23a_2213998_478575 / tp08579f40_c4ff_4603_9067_66d6414b7e52 / hdlfarrow。vhd # # # # # #开始代hdlfarrow VHDL的实体开始代hdlfarrow硬件描述语言(VHDL)架构# # #成功完成硬件描述语言(VHDL)过滤器的代码生成过程:hdlfarrow # # # HDL延迟是2 # # #样品开始一代的硬件描述语言(VHDL)试验台。刺激# # # # # #生成输入生成输入刺激;3100个样本长度。# # #生成试验台:/ tmp / Bdoc23a_2213998_478575 / tp08579f40_c4ff_4603_9067_66d6414b7e52 / hdlfarrow_default_tb。vhd # # #创造刺激向量……# # #完成生成硬件描述语言(VHDL)试验台。

自动生成测试向量的分数延迟端口,指定RampSweep为TestBenchFracDelayStimulus。它生成一个向量之间的值0和1以线性方式。这个向量的长度等于输入刺激向量。

generatehdl(高清“名字”,“hdlfarrow”,…“GenerateHDLTestbench”,“上”,…“TestBenchName”,“hdlfarrow_rampsweep_tb”,…“开发”,硬件描述语言(VHDL)的,…“TestBenchStimulus”,“唧唧喳喳”,…“TestbenchFracDelaystimulus”,“Rampsweep”,…“TargetDirectory”,workingdir);

# # #开始硬件描述语言(VHDL)过滤器的代码生成过程:hdlfarrow # # #生成:/ tmp / Bdoc23a_2213998_478575 / tp08579f40_c4ff_4603_9067_66d6414b7e52 / hdlfarrow。vhd # # # # # #开始代hdlfarrow VHDL的实体开始代hdlfarrow硬件描述语言(VHDL)架构# # #成功完成硬件描述语言(VHDL)过滤器的代码生成过程:hdlfarrow # # # HDL延迟是2 # # #样品开始一代的硬件描述语言(VHDL)试验台。刺激# # # # # #生成输入生成输入刺激;1028个样本长度。# # #生成试验台:/ tmp / Bdoc23a_2213998_478575 / tp08579f40_c4ff_4603_9067_66d6414b7e52 / hdlfarrow_rampsweep_tb。vhd # # #创造刺激向量……# # #完成生成硬件描述语言(VHDL)试验台。

您可以生成一个定制的输入刺激向量使用MATLAB命令并将其传递给试验台刺激用户定义的输入和属性fracdelay刺激。一个输入测试向量userinputstim使用生成尖声地说命令和分数延迟测试向量userfdstim生成测试向量的长度等于输入。

t = 2:0.01:2;% + / 2秒@ 100 Hz采样率userinputstim =唧唧声(t, 100, 1200,“问”);% @100Hz开始,跨越200赫兹在t = 1秒leninput =长度(userinputstim);samplefdvalues = (0.1, 0.34, 0.78, 0.56, 0.93, 0.25, 0.68, 0.45);samplesheld =装天花板(leninput /长度(samplefdvalues));第九= 1;为n = 1:长度(samplefdvalues) 1 userfdstim(第九:第九+ samplesheld-1) = repmat (samplefdvalues (n), 1, samplesheld);第九=第九+ samplesheld;结束userfdstim(第九:leninput) = repmat (samplefdvalues(结束),1,leninput-length (userfdstim));generatehdl(高清“名字”,“hdlfarrow”,…“GenerateHDLTestbench”,“上”,…“TestBenchName”,“hdlfarrow_userdefined_tb”,…“开发”,硬件描述语言(VHDL)的,…“TestBenchUserStimulus”userinputstim,…“TestbenchFracDelaystimulus”userfdstim,…“TargetDirectory”,workingdir);

# # #开始硬件描述语言(VHDL)过滤器的代码生成过程:hdlfarrow # # #生成:/ tmp / Bdoc23a_2213998_478575 / tp08579f40_c4ff_4603_9067_66d6414b7e52 / hdlfarrow。vhd # # # # # #开始代hdlfarrow VHDL的实体开始代hdlfarrow硬件描述语言(VHDL)架构# # #成功完成硬件描述语言(VHDL)过滤器的代码生成过程:hdlfarrow # # # HDL延迟是2 # # #样品开始一代的硬件描述语言(VHDL)试验台。刺激# # # # # #生成输入生成输入刺激;401个样本长度。# # #生成试验台:/ tmp / Bdoc23a_2213998_478575 / tp08579f40_c4ff_4603_9067_66d6414b7e52 / hdlfarrow_userdefined_tb。vhd # # #创造刺激向量……# # #完成生成硬件描述语言(VHDL)试验台。

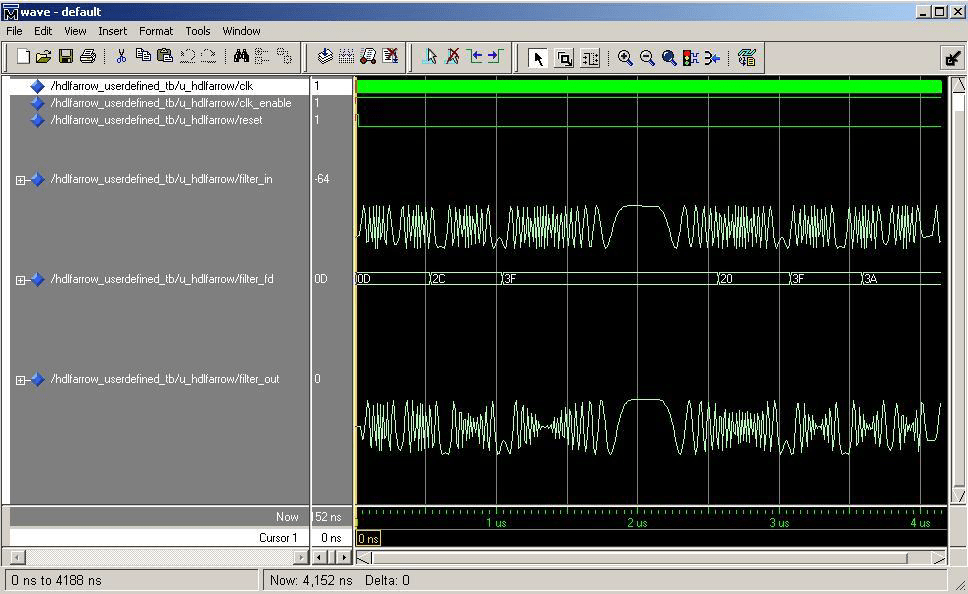

ModelSim®仿真结果

下面显示了ModelSim®HDL模拟器在运行硬件描述语言(VHDL)试验台之后。

结论

在本例中,我们为您介绍了如何设计一个双精度分数延迟滤波器满足给定的规范。我们还展示了如何量化滤波器并生成VHDL代码。然后我们为您介绍了如何生成硬件描述语言(VHDL)测试长椅使用几个选项指定输入和fracdelay刺激向量。

您可以使用任何HDL模拟器来验证这些结果。你也可以尝试Verilog过滤器和测试长椅。