利用fpga在环加速通信系统仿真

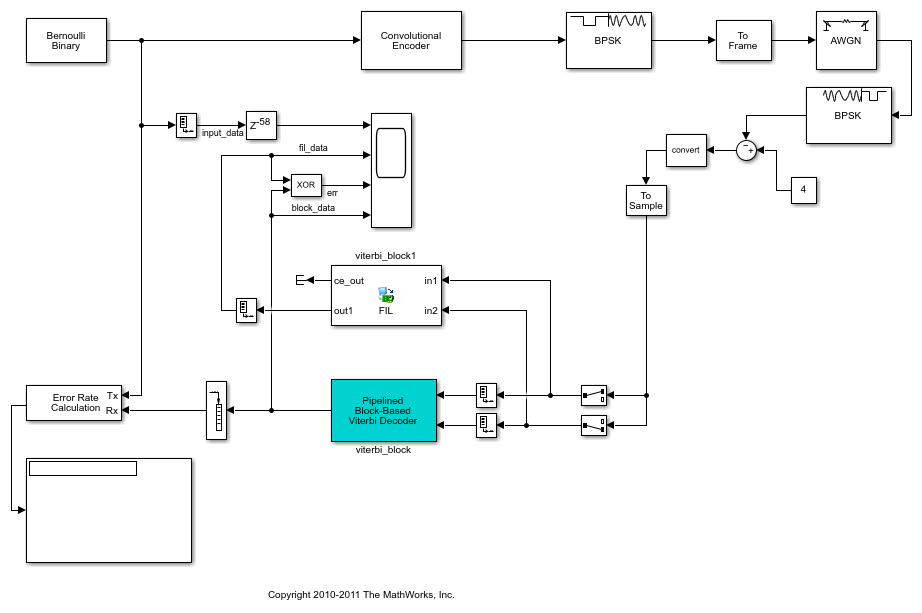

这个例子使用fpga在环(FIL)仿真来加速部分通信系统。该应用程序使用维特比算法对BPSK调制的卷积编码随机流进行解码,通过AWGN信道发送,然后解调。使用逐样采样方法可以比普通Simulink®模拟获得适度的加速,而使用“进程作为帧”选项则可以进一步加速。万博1manbetx

本示例使用通信工具箱™与HDL编码器™和HDL验证™结合,展示了使用fpga在环加速仿真的设计工作流。

需求和先决条件

运行此示例所需的工具:

FPGA设计软件

支持的FPGA开发板之万博1manbetx一。有关支持万博1manbetx的硬件,请参见万博1manbetx支持的FPGA设备用于FPGA验证.

使用以太网连接:主机上安装的千兆以太网适配器、千兆以太网交叉网线

使用JTAG连接:Intel FPGA板的USB Blaster I或II电缆和驱动器。用于Xilinx FPGA板的Digilent®JTAG电缆和驱动器。

PCI Express®连接:安装在上位机PCI Express槽位的FPGA板。

要求:MATLAB®和FPGA设计软件可以本地安装在您的计算机或网络可访问的设备上。如果使用来自网络的软件,则需要在计算机中安装第二个网络适配器,以便为FPGA开发板提供专用网络。请参阅计算机的硬件和网络指南,了解如何安装网络适配器。

1.打开并执行Simulink模型万博1manbetx

打开模型。由于要处理的数据量很大,在没有FIL的情况下,模拟大约需要9秒。我们将在以下步骤中使用FPGA在环路中提高模拟速度。

2.生成HDL代码

这一步需要HDL编码器。如果没有HDL编码器,则可以使用当前目录中预生成的HDL文件。

如果您打算使用这些复制的文件,请直接转到步骤3。

通过执行以下步骤,为维特比块子系统生成HDL代码:

A.右键单击标记为的现有FIL块viterbi_block1。单击“删除”以删除此块以生成代码。

b。在建模选项卡上,单击模型设置.

d。点击HDL代码生成窗格并确保hdlcoderviterbi_用于_fil/viterbi_块被选中。

e。点击生成.

或者,您可以通过在MATLAB提示符下输入以下命令来生成HDL代码:

makehdl (“hdlcoderviterbi_for_fil / viterbi_block”)

3.设置FPGA设计软件环境

在循环中使用FPGA之前,请确保您的系统环境已正确设置,以便访问FPGA设计软件。您可以使用该函数刀具轨迹将FPGA设计软件添加到当前MATLAB会话的系统路径。

4.在循环向导中运行FPGA

要启动FIL向导,在MATLAB提示符下输入以下命令:

费尔维齐;

4.1硬件选项

在单板列表中选择单板。单击Next继续。

4.2源文件

A.添加以前生成的所有HDL源文件维特比区块子系统。

b。选择文件viterbi_block.vhd作为顶级文件。您可能需要将FPGA in-the-Loop向导窗口加宽,以便查看这些选项。

c。请注意,viterbi_block已为您输入默认顶级模块名称。单击“下一步”继续。

4.3 DUT I/O端口

观察顶层模块的端口是否已正确识别。单击Next继续。

4.4构建选项

A.选择一个输出文件夹。

b。单击“构建”以构建FIL块和编程文件。

在构建过程中,会发生以下操作:

在新模型中生成名为viterbi_block的FIL块。

新模型生成后,FIL向导将打开一个命令窗口,在该窗口中,FPGA设计软件将执行合成、映射、放置和路由、时序分析和FPGA编程文件生成。对于该块,这些步骤大约需要20分钟。

当FPGA设计软件流程完成时,命令窗口中会显示一条消息,让您知道可以关闭该窗口。

5.打开并完成FIL的Simulink模型万博1manbetx

A.打开hdlcoderviterbi_for_fil.mdl

b。将前面生成的FIL块复制到它中,并将它平行地连接到viterbi_block或代替它。注意,原始块在右边有输入。要使FIL块在右边有它的输入,右键单击块,然后选择格式>翻转块.

6.配置费尔块

A.双击模型中的FIL块以打开块遮罩。

b。点击负载.

c。点击好啊关闭块掩码。

7.费尔模拟运行

运行模拟20480秒并观察性能。

FrameSize = 1;抽搐;sim卡(‘hdlcoderviterbi_for_fil’); fs1=总有机碳

您可以尝试将帧大小设置为一个较大的数字。对于本例,帧大小被设置为1024字节。

帧大小=1024;tic;sim(‘hdlcoderviterbi_for_fil’); fs2=总有机碳

在我们的测试中,当FrameSize = 1时,模拟时间大约为16秒,这与在Simulink中不使用FIL的模拟时间相同,但当使用Xilinx Spartan-6 SP605板将帧大小增加到1024时,模拟时间减少到大约12秒。万博1manbetx这个特殊的板和系统提供了大约1.7倍的整体加速,但其他板和通信系统可能更快。

加速比=fs1/fs2

通过删除Simulink块版本并万博1manbetx仅模拟FIL版本,以及通过向设计的FIL部分添加更多块并尽可能删除Simulink范围和显示,可以实现更大的加速。

最后给出了fpga在环加速通信系统仿真实例。