MATLAB AXI Master的设置

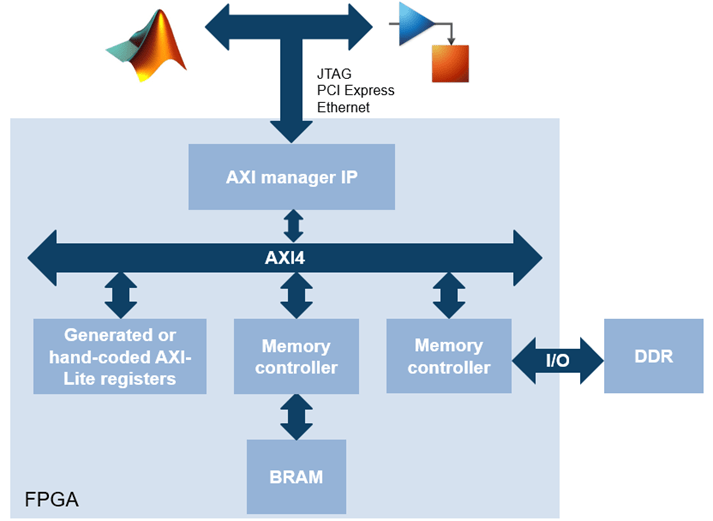

您可以在FPGA设计中使用MATLAB AXI master IP从MATLAB访问板载内存位置,以及aximaster对象。该对象通过物理电缆连接到IP,并允许从MATLAB命令行读取和写入从内存位置的命令。

要使用此功能,必须下载FPGA板的硬件支持包。看见万博1manbetx下载FPGA板支持包万博1manbetx.

从MATLAB访问车载存储器位置®,您必须在FPGA设计中包含MATLAB AXI主IP。该IP连接到板上的从内存位置。该IP还通过JTAG、PCI Express或以太网电缆响应来自MATLAB命令行的读写命令。

要设置AXI主IP以便从MATLAB访问,请执行以下设置步骤:

在FPGA设计中包括MATLAB AXI master IP。要将IP文件的路径添加到项目中,请调用

维瓦多大师或四夸脱肌功能。在FPGA项目中,指定允许AXI主IP访问的地址。

笔记

AXI主IP支持AXI4 Lite、万博1manbetxAXI4和Altera®Avalon从存储器位置。FPGA互连自动将AXI4事务转换为每个地址的协议。

编译您的FPGA项目,包括MATLAB AXI master IP。

使用物理电缆(JTAG、PCI Express或以太网电缆)将FPGA板连接到主机。

用编译后的设计对FPGA进行编程。

笔记

或者,您可以在HDL编码器中执行这些步骤™ 通过使用示例参考设计(如以下示例中包含的设计)指导工作流:无嵌入式ARM处理器的IP核心生成工作流:Arrow DECA MAX 10 FPGA评估工具包(HDL编码器)或(HDL编码器)。

一旦程序在FPGA板上运行,就可以创建MATLAB AXI master对象,aximaster.要访问板上的从存储器位置,请使用读存储器和书写记忆此对象的方法。

JTAG注意事项

当使用JTAG作为电路板的物理连接时,可能会有其他IP使用相同的JTAG连接。此类IP包括FPGA数据捕获、Altera SignalTap II或Xilinx®万岁®逻辑分析仪核心。在您的设计中,MATLAB AXI master IP可以与使用JTAG连接的其他IP共存,但是,一次只能有一个应用程序使用JTAG电缆。释放aximaster对象返回JTAG资源以供其他应用程序使用。

JTAG电缆最常见的冲突用途是重新编程FPGA。在使用电缆编程FPGA之前,请停止任何FPGA数据捕获或MATLAB AXI master JTAG连接。

主机和FPGA之间的最大数据速率受JTAG时钟频率的限制。对于Altera板,JTAG时钟频率为12 MHz或24 MHz。对于Xilinx板,JTAG时钟频率为33 MHz或66 MHz。JTAG频率取决于电缆类型和FPGA板支持的最大时钟频率。万博1manbetx