视频处理使用FPGA-in-the-Loop加速度

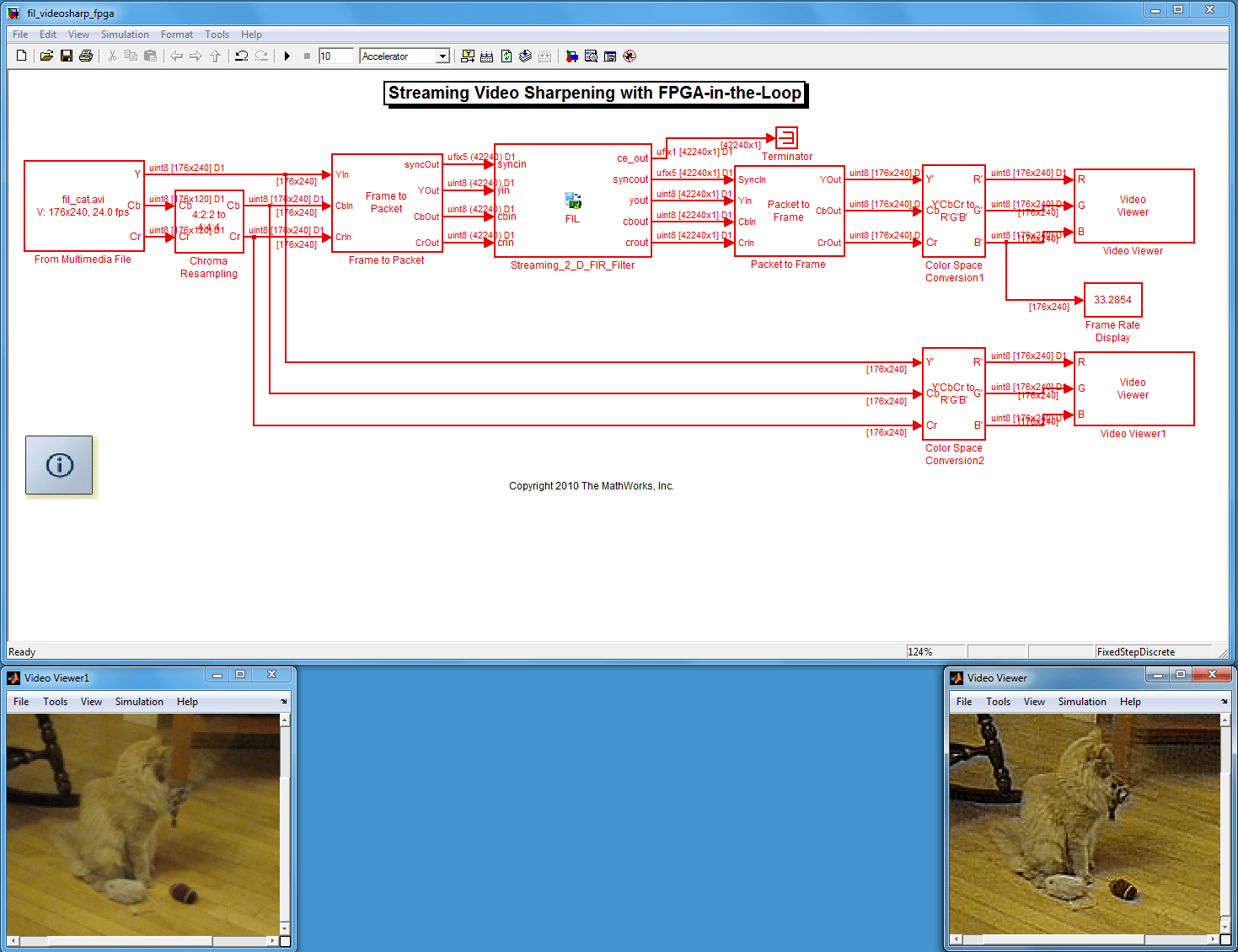

这个示例使用FPGA-in-the-Loop (FIL)模拟加速视频处理模拟与仿真软件通过添加一个FPGA®。万博1manbetx所示的流程分析一个简单的系统,提高一个RGB视频输入以每秒24帧。

下面的例子使用了计算机视觉工具箱™与高密度脂蛋白编码器™和HDL校验™实现费尔的工作流仿真显示设计。

工具需要运行这个例子:

FPGA设计软件(Xilinx ISE®®或Vivado®设计套件或英特尔®第四的®主要设计软件)

一个支持的FPGA开发万博1manbetx板及配件(ML403, SP601 BeMicro SDK,气旋三世Starter Kit董事会不支持这个例子)。关于硬件支持的更多信息,请参阅万博1manbetx万博1manbetx支持FPGA器件FPGA验证。

使用以太网连接:千兆以太网适配器安装在主机上,千兆以太网交叉电缆

连接使用JTAG: USB导火线I或II电缆Altera FPGA板和驱动程序。Digilent®JTAG电缆和司机Xilinx FPGA板。

连接使用PCI Express®: FPGA板安装到主机的PCI Express插槽。

MATLAB®和FPGA设计软件可以在本地安装在您的计算机或网络设备访问。如果你使用软件的网络需要第二个网络适配器安装在你的电脑提供一个私有网络的FPGA开发板。咨询您的计算机的硬件和网络指导学习如何安装网络适配器。

1。开放和执行仿真软件模型万博1manbetx

打开模型和仿真运行0.21 s。

由于大量的数据处理,仿真不流利。我们将在以下步骤提高仿真速度使用FPGA-in-the-Loop。

2。生成HDL代码

生成流媒体视频磨子系统的HDL代码通过执行以下步骤:

一个。右键单击标签流二维滤波器。

b。选择高密度脂蛋白HDL代码>生成子系统在上下文菜单中。

另外,您可以通过输入以下命令生成HDL代码在MATLAB提示:

makehdl (“fil_videosharp_sim /流二维滤波器”)

如果你不希望生成HDL代码,您可以使用HDL文件位于预先生成videosharp_hdlsrc文件夹中。

3所示。建立了FPGA设计软件

在使用FPGA-in-the-Loop之前,确保你的系统环境访问FPGA设计软件的设置正确。您可以使用函数hdlsetuptoolpathXilinx Vivado或英特尔第四的'添加到当前MATLAB系统路径。

Xilinx FPGA板运行

hdlsetuptoolpath (“ToolName”,“Xilinx Vivado”,“路径”,“C: \ Xilinx \ Vivado \ 2019.2 \ bin);

这个例子假定Xilinx Vivado可执行文件位于C: \ Xilinx \ Vivado \ 2019.2 \ bin。替代你的实际可执行的位置如果它是不同的。

英特尔公司董事会,运行

hdlsetuptoolpath (“ToolName”,“阿尔特拉第四的二世”,“路径”,“英特尔C: \ \第四的\ 18.1 \ bin64);

这个例子假定英特尔第四的'可执行文件位于C: \英特尔\第四的\ 18.1 \ bin64。替代你的实际可执行的位置如果它是不同的。

4所示。运行FPGA-in-the-Loop向导

输入以下命令启动费尔向导在MATLAB提示:

filWizard;

4.1硬件选项

选择一个在董事会名单。

4.2源文件

一个。添加以前生成的高密度脂蛋白的源文件流媒体视频锐化子系统。

b。选择Streaming_2_D_FIR_Filter.vhd作为顶级文件。

4.3 DUT的I / O端口

不改变任何事情在这个视图。

4.4构建选项

一个。选择一个输出文件夹。

b。单击Build构建费尔块和FPGA编程文件。

在构建过程中,发生以下行为:

费尔块名叫Streaming_2_D_FIR_Filter生成新的模型。不要关闭这个模型。

新模型生成后,费尔向导打开一个命令窗口,FPGA设计软件进行合成,健康,place-and-route时机分析,FPGA编程文件生成。当FPGA设计软件过程完成后,在命令窗口消息让你知道你可以关闭窗口。关闭窗口。

c。关闭fil_videosharp_sim。基金模式。

5。开放和费尔完成仿真软件模型万博1manbetx

一个。打开fil_videosharp_fpga。基金模式。

b。复制在它前面生成的费尔fil_videosharp_fpga块。基金,它说“与费尔块替换”

6。配置费尔块

一个。双击视频中的费尔块磨FPGA-in-the-Loop模型打开块面具。

b。点击负载。

c。点击好吧关闭块面具。

7所示。费尔模拟运行

运行仿真10年代,观察性能改进。

总结了视频处理加速度使用FPGA-In-the-Loop例子。