fpga仿真软件中波束形成:算法设计万博1manbetx

这个例子展示了上半年的工作流开发beamformer仿真软件®适合在硬件上实现,如现场可编程门阵列(FPGA)。万博1manbetx它还展示了如何实现模型的比较结果与行为模式。

第二部分的例子fpga仿真软件中波束形成:代码生成万博1manbetx显示了如何生成HDL代码的实现模型,并验证所生成的HDL代码产生正确的结果相比,行为模型。

这个例子展示了如何实现一个FPGA-ready beamformer匹配相应的行为模型在仿真软件利用相控阵系统工具箱™、DSP系统工具箱™和定点设计师™库。万博1manbetx验证实现模型,这个例子比较了模拟输出的实现模型和行为模型的输出。

相控阵系统工具箱用于设计和验证浮点算法功能,它提供了行为参考模型。然后行为模型被用于验证的结果定点实现模型用于生成HDL代码。

定点设计师提供数据类型和工具发展中定点和单精确算法优化性能在嵌入式硬件。您可以执行bit-true模拟观察有限的范围和精度的影响没有实现对硬件的设计。

FPGA分区模型

有三个关键的建模概念要记住当准备针对fpga仿真软件模型:万博1manbetx

纸浆包处理:通常也称为串行处理、纸浆包处理是一种有效的数据处理技术在硬件设计,使您能够权衡资源和吞吐量。

子系统针对HDL代码生成:为了生成HDL代码从一个模型,实现算法必须在仿真软件子系统。万博1manbetx

Time-aligned行为和实现模型的输出:比较输出的行为和FPGA实现模型,必须通过添加时间调整其输出延迟行为模型。

波束形成算法

这个例子显示了一个相移beamformer行为算法,重新实现的高密度脂蛋白算法子系统通过使用仿真软件支持HDL代码生万博1manbetx成的块。万博1manbetxbeamformer计算所需的阶段之间的十个通道接收信号功率最大化的方向入射角度。行为的图显示了仿真软件模型算法及其相应的实万博1manbetx现算法的FPGA。

modelname =“万博1manbetxSimulinkBeamformingHDLWorkflowExample”;open_system (modelname);集(allchild (0)“可见”,“关闭”);

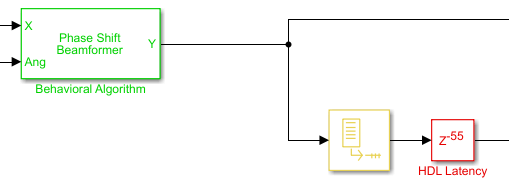

仿真软件万博1manbetx模型有两个分支。顶端分支行为,浮点算法和模型底部分支的功能与使用块定点版本支持HDL代码生成。万博1manbetx除了策划的输出两个分支比较两个,这个例子还计算和情节的不同,或错误,两国输出。

模型有一个延迟( )块的输出行为的算法。这种延迟是必需的,因为实现算法使用55延迟实现流水线创建延迟,需要占。占这个延迟称为延迟之间的平衡和必要time-align输出行为模型和实现模型,让它更容易比较结果。

)块的输出行为的算法。这种延迟是必需的,因为实现算法使用55延迟实现流水线创建延迟,需要占。占这个延迟称为延迟之间的平衡和必要time-align输出行为模型和实现模型,让它更容易比较结果。

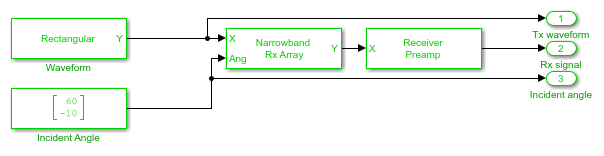

多通道接收信号

合成相控阵天线的接收信号,该模型包含一个子系统,生成一个多通道的信号。的基带多通道信号子系统模型传输波形和接收到的目标回波的入射角捕获通过10-element天线阵列。高保真前置子系统还包括一个接收机模型占接收机噪声。这个子系统生成的输入刺激我们的行为和实现模型。

open_system ([modelname/基带多通道信号的]);

序列化和量化

该模型包括一个串行化和量化子系统将浮点数转换,信号不定位定点,纸浆包信号建模流媒体数据在硬件所必需的。这个模型使用标量流处理,因为这个算法运行低于400 MHz。硬件实现可以优化资源,而不是更高的吞吐量。

open_system ([modelname/串行化和量化的]);set_param (modelname“SimulationCommand”,“更新”)

序列化子系统的输入信号有10 300样本/频道的频道或300 x10大小信号。子系统序列化或unbuffers信号产生一个纸浆包1 x10的信号,即。每通道,一个样本,然后量化,以满足系统的需求。

输出数据类型数字转换信号的块fixdt (1、12、9),这是一个与12位字长签署了价值和9-bit分数长度精度。字长是12位,因为设计是针对Xilinx®Virtex®7 FPGA是连接到一个12位ADC。长度比例提供最大范围的输入信号。

设计实现子系统

的高密度脂蛋白算法子系统,它是针对HDL代码生成,使用仿真软件实现了beamformer,设计支持HDL代码生成的块。万博1manbetx万博1manbetx

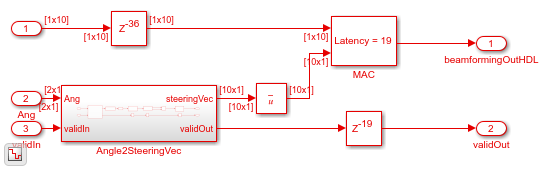

的Angle2SteeringVec子系统计算信号的延迟在每个天线元素均匀线性阵列(ULA)”。然后美联储延迟相乘,积累(MAC)子系统进行波束形成。

open_system ([modelname“/ HDL算法”]);

该算法的高密度脂蛋白算法子系统的功能与行为相移波束形成算法可生成HDL代码。有三个主要的差异使这个子系统生成高效HDL代码。

设计过程的输入顺序,即使用纸浆包处理。

该子系统使用定点计算的数据类型。

实现包括延迟,使流水线的高密度脂蛋白合成工具。

确保适当的时钟计时,实现模型的任何延迟添加到一个分支必须匹配所有其他并行分支如上图所示。的Angle2SteeringVec子系统,例如,36延误;因此,顶部的分支高密度脂蛋白算法子系统包括36个样品之前的延迟MAC子系统。同样,MAC子系统使用19延迟,必须平衡通过添加19延迟的输出Angle2SteeringVec子系统。这个图显示的内部MAC子系统说明19延迟。

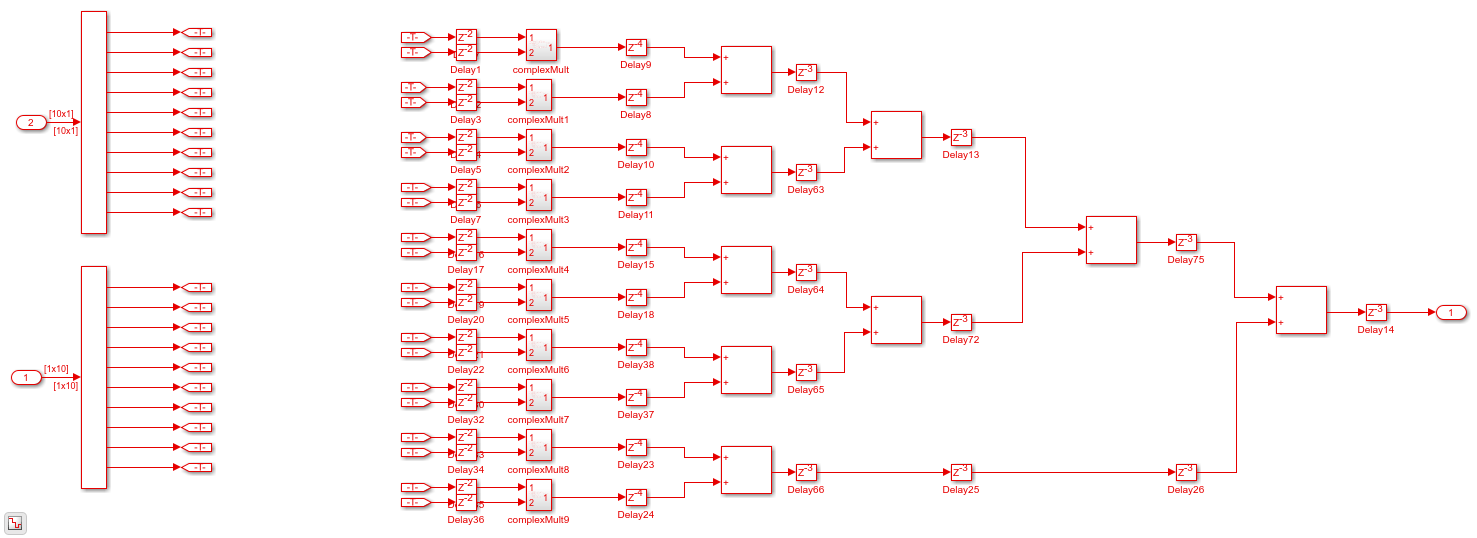

open_system ([modelname' / HDL算法/ MAC ']);set_param (modelname“SimulationCommand”,“更新”)

的底部MAC子系统有一个 块,其次是复杂的乘法块包含一个

块,其次是复杂的乘法块包含一个 ,那么

,那么 4块,其次是延迟的

4块,其次是延迟的 总共19延迟。中定义的延迟值PreLoadFcn模型属性的回调。

总共19延迟。中定义的延迟值PreLoadFcn模型属性的回调。

计算转向向量

的Angle2SteeringVec子系统计算转向矢量信号的到达角。它首先计算各传感器信号的到来推迟matrix-multiplying天线元素在数组中的位置的入射方向的信号。然后传递到延迟要求子系统的计算正弦和余弦三角函数使用简单而高效CORDIC算法。

open_system ([modelname“/ HDL算法/ Angle2SteeringVec”]);

因为这个设计由10元素齿龈间隔半波,天线元素的位置是基于每个天线元素之间的间距测量表面上从天线阵的中心。定义元素的向量之间的间距10数从-6.7453到6.7453,即。间距的1/2波长,2.99 / 2。在定点运算,数据类型用于空间向量的元素fixdt (1、8、4),即,a signed value with 8-bit word length and 4-bit fraction length.

反序列化

比较你的定点和浮点实现纸浆包框架行为设计你需要反序列化实现子系统的输出并将它转换成浮点数据类型。或者,您可以比较结果直接与纸浆包信号然后你必须unbuffer行为模型的输出与纸浆包信号输出与实现算法,如这个图所示。

在这种情况下,您只需要转换的输出高密度脂蛋白算法子系统通过设置浮点数据类型转换的输出块双。

比较HDL模型行为模型的输出

运行模型来显示结果。您可以运行仿真软件模型通过单击播万博1manbetx放按钮或从命令行调用sim命令MATLAB®。使用范围比较输出视觉。

sim (modelname);

Beamformed信号的时间范围和Beamformed信号(HDL)显示两个信号几乎是相同的。误差在10 ^ 3的顺序在误差范围内。这个结果表明,高密度脂蛋白算法子系统产生相同的输出行为模型量化误差之内。这个验证生成HDL代码之前是重要的第一步。

因为使用的HDL模型55延误,名为HDL Beamformed范围信号延迟了55 ms相比原始传输或Beamformed信号显示在行为Beamformed信号范围。

总结

这个例子是分两部分的教程系列的第一篇关于如何设计一个FPGA-ready算法,自动生成HDL代码,验证仿真软件中的HDL代码。万博1manbetx这个例子展示了如何使用块从相控阵系统工具箱建立行为模型作为金色的参考,以及如何创建一个子系统使用仿真软件对硬件实现支持HDL代码生成的块。万博1manbetx万博1manbetx还比较了实现模型的输出相应的输出行为模型来验证两种算法在功能上是等同的。

一旦你确认您的实现算法功能与你的黄金参考,您可以使用HDL编码器™HDL代码生成模型万博1manbetx(高密度脂蛋白编码器)和HDL校验™生成Cosimulation模型(高密度脂蛋白编码器)试验台。

这个分两部分的教程系列的第二部分fpga仿真软件中波束形成:代码生成万博1manbetx显示了如何生成HDL代码的实现模型,并验证所生成的HDL代码产生相同的结果作为浮点行为模型以及定点实现模型。