ADC IBIS-AMI模型基于COM

这个例子展示了如何使用SerDes Toolbox™库中的库块和自定义块创建IEEE 802.3ck规范基于ADC的发射机和接收机IBIS-AMI模型来建模时间无关的ADC。生成的模型符合IBIS-AMI标准。虚拟采样节点存在于基于切片的SerDes系统中,但不存在于基于adc的SerDes系统中,通过仿真可以在Simulink®和IBIS-AMI模拟器中生成虚拟眼图,以评估通道。万博1manbetx

使用MATLAB脚本建立SerDes IBIS-AMI模型

这个例子使用MATLAB®脚本首先构建一个代表ADC架构的发射机和接收机的SerDes系统,然后导出到SerDes Simulink模型。万博1manbetx在MATLAB命令窗口中输入命令来运行脚本:

buildSerDesADC

在导出到Simulink之前,使用以下属性配置SERDES系统。万博1manbetx请注意,自定义块将用作传递算程序,直到应用示例中稍后讨论的Simulink自定义。万博1manbetx

配置设置

符号时间设置为18.8235ps,因为802.3ck的最大允许操作数据速率是106.25Gb/s。

目标BER.设置为1e-4。

每个符号样本设置为32。

调制设置为PAM4。

信号被设置为差异。

发射机模型设置

Tx FFE区块设置为3个预点击和1个后点击,包括5个点击权重。

Tx VGA模块用于控制发射振幅。

Tx AnalogOut模型是这样设置的电压是1 v,上升时间6.161 ps,R.(输出电阻)为50欧姆C(电容)根据802.3ck规范为5fF。

通道模型设置

频道损失设置为15dB。

目标频率设置为奈奎斯特频率。

差分阻抗保持默认100欧姆。

接收器模型设置

Rx AnalogIn模型是这样建立的R.(输入电阻)为50欧姆C(电容)根据802.3ck规范为5 fF。

噪声自定义块将高斯噪声注入时域波形。

分别设置3个RX CTL块的级联分别为7,21和1个配置。这GPZ(增益极点零)矩阵数据从802.3ck行为CTLE规范中给出的传递函数中得到。

RX VGA自定义模块适用适应增益。

饱和放大器模块采用无记忆非线性。

ADC自定义块量化时域信号。

Rx FFE自定义有21次点击(3次前光标和17次后光标点击),其权重将在Rx全局适应期间自动计算。

RX DFECDR块设置为一个DFE抽头。DFE Tap仅限于+/- 0.5V幅度。

在Simulink中建立基于adc的SerDes Tx/Rx IBIS-AMI模型万博1manbetx

本例的第二部分采用脚本导出的SerDes系统,并根据Simulink中基于adc的SerDes的需要对其进行定制。万博1manbetx

回顾Simul万博1manbetxink模型设置

导出到Simulink的Serdes系统包括配置,刺激,TX,模万博1manbetx拟通道和RX块。

推入Tx子系统。

推入Rx子系统。

为基于adc的SerDes定制模型

从SERDES应用程序导出的模型需要首先自定义以通过自定义其他RX块并修改RX Init块代码来表示基于ADC的Serdes Rx。

配置输入参考Rx噪声块

Rx子系统中的噪声可以在输出或输入处建模。输入参考噪声源由随后的均衡阶段(CTLE和FFE)塑造,因此更好地反映了噪声是如何被真实系统塑造的。另一方面,输出参考噪声是不成形的,并且没有捕捉到改变CTLE和FFE上的设置对噪声的影响。

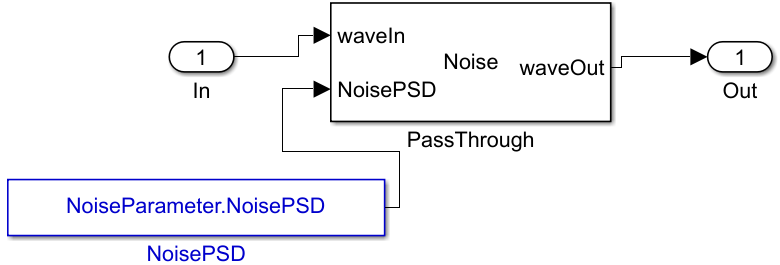

通过单击块上的向下箭头,进入名为Noise的直通块。

将现有的系统对象指向Noise。M系统对象。看到在Serdes Toolbox Passthrough块中实现自定义CTL。

在系统对象掩码中,使用系统变量配置“符号时间”、“采样间隔”和“调制”。

在IBIS-AMI管理器中为名为Noise的块创建IBIS-AMI参数NoisePSD使用图中的属性。值8.2e-9来自COM标准。看到管理AMI参数。

将生成的常量块连接到Noise输入端口。

配置VGA块

下降到名为VGA的传递块。

将现有的系统对象指向serdes。包含在SerDes工具箱中的VGA系统对象。

在系统对象掩码中,关闭“模式端口”以强制块处于开启状态。

在IBIS-AMI管理器中为名为的VGA块创建IBIS-AMI参数获得使用图中的属性。

连接生成的数据存储读取到增益输入端口。删除数据存储写,因为该值只在Init中更新,不在time域中更新。

VGA适应

VGA自适应很简单,所需增益在Init中计算为目标脉冲振幅与输入脉冲响应的最大峰值的比值。然而,对于不同的CTLE设置,所需的VGA增益可能是不同的,因此需要在前面描述的通用算法的每次迭代中评估VGA增益。

ADC配置块

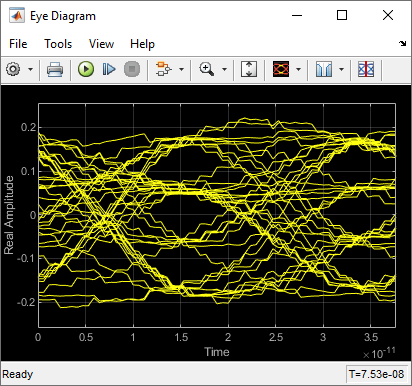

使用的ADC模型是一个时间无关的ADC,这意味着模拟中的每个点都是量化的,而不仅仅是在采样瞬间。然而,DFE和时钟恢复仍然只在采样瞬间使用ADC采样。一个不确定时间的ADC允许生成一个等效波形,如图所示在DFE求和节点:允许构建具有代表性高度和宽度的信号眼图。

下行到名为ADC的直通块

将现有系统对象指向示例目录中的ADC.M系统对象。

在系统对象掩码中,使用系统变量配置“符号时间”、“采样间隔”和“调制”。

配置Rx FFE

下降到名为Rx_FFE的直通块

将现有系统对象指向SERDES工具箱中包含的Serdes.ffe系统对象。

在“系统对象屏蔽的主选项卡”中,关闭模式端口并关闭标准化抽头。在“高级”选项卡中,使用系统变量配置符号时间和采样间隔。

在IBIS-AMI Manager中为Rx_FFE块创建一个tap结构,包括3次前光标点击、17次后光标点击和如图所示的属性。

[Zeros(1,3)1零(1,17)]

连接生成的数据存储读取轻按权重输入端口。当数据存储不再使用时,删除该数据存储的写操作。

企业适应

RX FFE在ADC采样数据上运行,而不是在连续波形上运行。然而,在统计适应期间,假设即使在数据样本之间也可以使用所有波形点。RX FFE仅适用于自定义用户初始代码;通过提供的Adapffe功能辅助适应。考虑到输入脉冲响应,RX FFE适配目标是驱动输出脉冲响应,使得预先和光标数据样本被驱动为零。这并不意味着除光标点之外的脉冲响应将是零。相反,与同步波形一样,ISI在数据采样点处仅被驱动为零。

由于Rx FFE对采样数据进行操作,在adaptFFE中,自适应过程的第一步是假定输入脉冲响应的数据采样相位。使用的方法是贪婪地假设我们可以强制采样,以便光标停留在传入脉冲响应的峰值上。

由于在Rx子系统中,Rx FFE之后是一个1-tap DFE,因此Rx FFE不需要强制第一个后光标为零。相反,Rx FFE需要确保第一个后光标落在1-点击DFE的均衡范围内。注意,如果没有使用后Rx DFE,那么目标将是零强迫所有前光标和后光标ISI。

给定现在采样的输入脉冲响应,目标是找到一个过滤器响应,使光标前和后数据样本为零,或者在第一个后光标样本的情况下,进入DFE的范围。这个优化问题与求解一组线性方程组密切相关,我们需要找到矩阵的逆。这个需要反求的矩阵是由循环移位的输入采样脉冲响应组成的矩阵。这个反矩阵然后乘以期望的输出目标脉冲响应:[0,0,0,1,bmax, 0,0…]对于3-tap前驱Rx FFE的情况,其中1表示光标位置,bmax表示DFE的最大范围。所需的Rx FFE FIR滤波器系数是反向的、循环移位的输入脉冲响应矩阵和所需的输出脉冲响应的乘积。

DFECDR适应

DFECDR适应遵循RX FFE适应。dfecdr是Serdes工具箱中的标准块,请参阅DFECDR块的在线文档。

本示例使用一个Alexander (bang-bang)鉴相器,而不是通常用于基于adc的SerDes系统的波特率鉴相器。这种建模选择简化了示例,因为波特率相位检测器将与自适应收敛相互作用。基于adc的SerDes系统需要应对CDR锁定点与Rx FFE和DFE自适应之间的交互。

自定义Rx子系统初始化代码块

在本例中,Rx子系统的自适应是在统计域内执行的:涉及CTLE、FFE和DFE的共同自适应,以在给定使用的信道和Tx FFE设置的情况下实现尽可能最好的误码。在时域模拟期间,CTLE和FFE的优化设置将保持固定,而DFE和CDR在时域模拟期间继续适应。

使用示例中提供的代码修改Init的自定义用户代码区域。看到全局适应接收器组件,使用脉冲响应度量来提高Serdes性能。

单击Init掩码对话框上的Refresh Init以根据前面的步骤更新代码。

单击Init Mask对话框上的Show Init以打开Init代码。

复制代码

adcInitCustomUserCode.m在示例目录中。

编辑adcInitCustomUserCode.m

在自定义用户代码区域结束之前粘贴复制的代码。确保保留自定义用户区域顶部的AMI参数。不要修改超出自定义用户区域的末尾的代码。

统计适应算法

统计自适应算法通过每个Rx子系统块处理脉冲响应,并测量得到的脉冲响应优值。由于这是一个基于adc的系统,使用的优点是信噪比(SNR),其中噪声项还包括残留的前光标和后光标ISI。

通常,统计RX适配将按如下方式进行:

选择了一个初始的CTLE设置

选择VGA设置使脉冲振幅落在目标范围内

RX FFE自动调整,以便在数据采样点处进行ISI。

DFE被用来去除后光标ISI。

计算了数据采样点的信噪比。

对每个可能的CTLE设置重复上述步骤,跟踪每个设置的信噪比值。选取信噪比最高的设置作为全局自适应点。

运行Simuli万博1manbetxnk模型

访问激励块掩码对话框并将符号数更改为4000。

访问IBIS-AMI Manager的导出选项卡并将Rx忽略位更新为2000。这和之前的修改将确保时域自适应有足够的时间收敛。更多的符号和忽略时间将产生更现实的结果。

运行该模型对基于adc的SerDes系统进行仿真。

更新ADC量化

在本例中,默认情况下ADC量化设置为6b。尝试将ADC量化到一个较低的量,观察ADC精度降低对时域眼形的影响。

生成基于adc的SerDes IBIS-AMI模型

本示例的最后一部分采用定制的基于adc的SerDes Simulink模型,然后生成一个符合IBIS-AMI的模型:包括模型可执行文件、I万博1manbetxBIS和AMI文件。

目前的IBIS AMI标准对ADC的SERDES没有本机支持。万博1manbetx目前标准是针对基于SliCer的SERDES编写的,其包含一个信号节点,其中观察到均衡信号波形。在基于SliCer的Serdes中,此节点存在于DFE之前的DFE内部。在该节点处可观察到连续的模拟波形,该节点包括所有上游均衡器(例如CTLE)的效果和由于DFE引起的均衡,因为拍摄加权和反馈之前的决定。由于系统中的ADC,这种总结节点不存在于基于ADC的SERDES中。在基于ADC的Serdes系统中,ADC证明了虽然在采样瞬间的眼睛。要模拟虚拟节点,使用时间不可止结的ADC。该ADC在模拟时间步速率下量化进入的模拟波形中的每个点:即1 / FB / SPS,其中SPS是每个符号的样本数,FB是波特率。RX FFE还将输入信号处理为连续波形,而不是样本。但是,RX FFE适用于SPS-仿真时间步骤的单个抽自值。 The DFE is the stock DFE from the SerDes Toolbox and is written for slicer based SerDes. This signal chain allows for the signal integrity simulator to be able to observe a virtual eye in an ADC-based system.

出口IBIS-AMI模型

打开出口选项卡。

验证二元模型为Tx和Rx AMI模型设置选择。这将创建支持统计(Init)和时域(GetWave)分析的模型可执行文件。万博1manbetx

设置Tx模型忽略值的比特到5,因为在Tx FFE有三次点击。

设置Rx模型忽略值的比特数到20,000,以便有足够的时间让Rx DFE接头在时域模拟期间稳定下来。

放模型出口作为Tx和Rx都有以便选择要生成的所有文件(IBIS文件、AMI文件和DLL文件)。

按下出口按钮在目标目录中生成模型。

另请参阅

CTLE|DFECDR|固定资产|SaturatingAmplifier|VGA