在并行转换器系统时钟和数据恢复

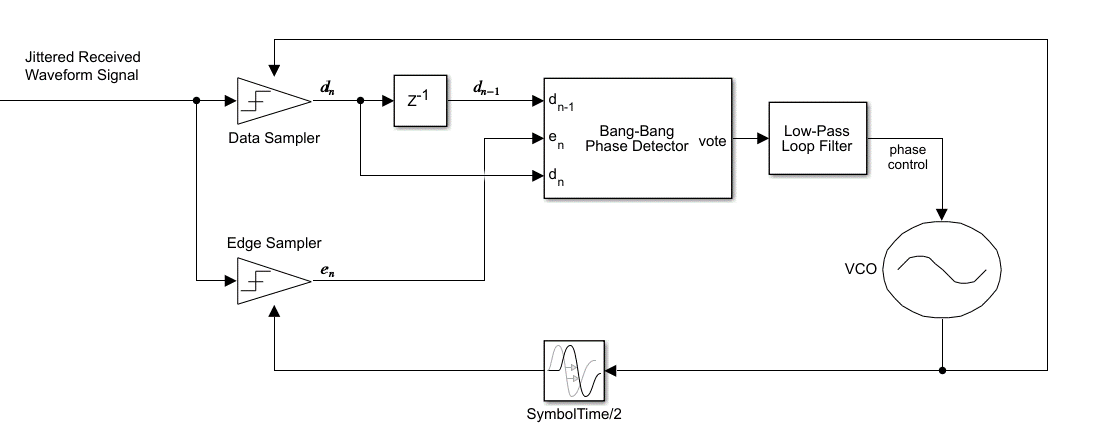

高速模拟并行转换器系统使用时钟和数据恢复(CDR)电路提取正确的时间正确的样本输入的波形。CDR电路产生一个时钟信号一致的阶段,在一定程度上传播的频率信号。相位跟踪(一阶CDR)通常是通过使用非线性砰砰的枪声或亚历山大相位侦测器驱动压控振荡器(VCO)。二阶频率跟踪(CDR)集成了剩余相位误差和补偿总差异发射机参考时钟和接收机参考时钟。serdes.CDR和serdes.DFECDR使用一阶CDR算法。

相位侦测器

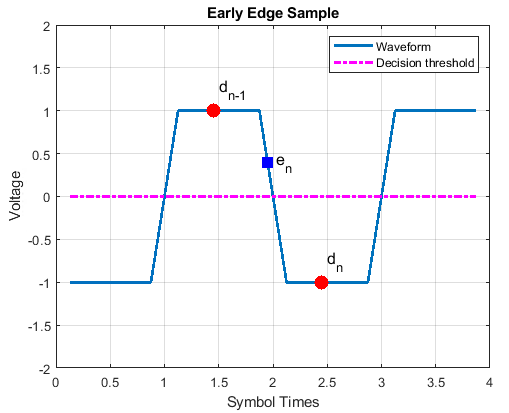

亚历山大或继电器式控制相位探测器接收到的波形样本在每个符号的边缘和中间。边缘样本(en(d)和数据样本n1和dn)是处理一些数字逻辑来确定边缘的样本,因此时钟相位,是早或晚。边缘样本,en和数据样本,dn,由一个符号时间的一半。

考虑波形数据转换发生的,和两个en和dn低于阈值电压决定。的二进制值解决en和dn匹配,这表明时钟阶段是晚了。

同样的,当e的二进制值解决n和dn1匹配,时钟是早期阶段。

代表二进制输出±1,取样器的相位检测器的行为对NRZ或PAM4调制进行了总结:

| dn1 | en | dn | 行动 |

|---|---|---|---|

| −1 | −1 | 1 | 时钟是早期阶段。转变阶段。 |

| 1 | 1 | −1 | |

| −1 | 1 | 1 | 时钟相位迟了。阶段转向左边。 |

| 1 | −1 | −1 | |

| −1 | X | −1 | 不采取行动是必要的。 |

| 1 | X | 1 |

PAM3调制,象征水平−0.5,0,0.5。默认阈值水平(th)±0.25。修改后的真值表因此成为:

| dn1 | en | dn | 行动 |

|---|---|---|---|

| −0.5 | en>−th | 0 | 晚些时候 |

| −0.5 | en<−th | 0 | 早期 |

| −0.5 | en> 0 | 0.5 | 晚些时候 |

| −0.5 | en< 0 | 0.5 | 早期 |

| 0 | en>th | 0.5 | 晚些时候 |

| 0 | en<th | 0.5 | 早期 |

| 0 | en>−th | −0.5 | 早期 |

| 0 | en<−th | −0.5 | 晚些时候 |

| 0.5 | en>th | 0 | 早期 |

| 0.5 | en<th | 0 | 晚些时候 |

| 0.5 | en> 0 | −0.5 | 早期 |

| 0.5 | en< 0 | −0.5 | 晚些时候 |

直接开车VCO相位检测器输出结果的过度时钟抖动。消除抖动、相位检测器的输出低通滤波器过滤通过累积投票。当累积投票超过一个特定的阈值,递增或递减阶段的VCO。

恢复时钟信号

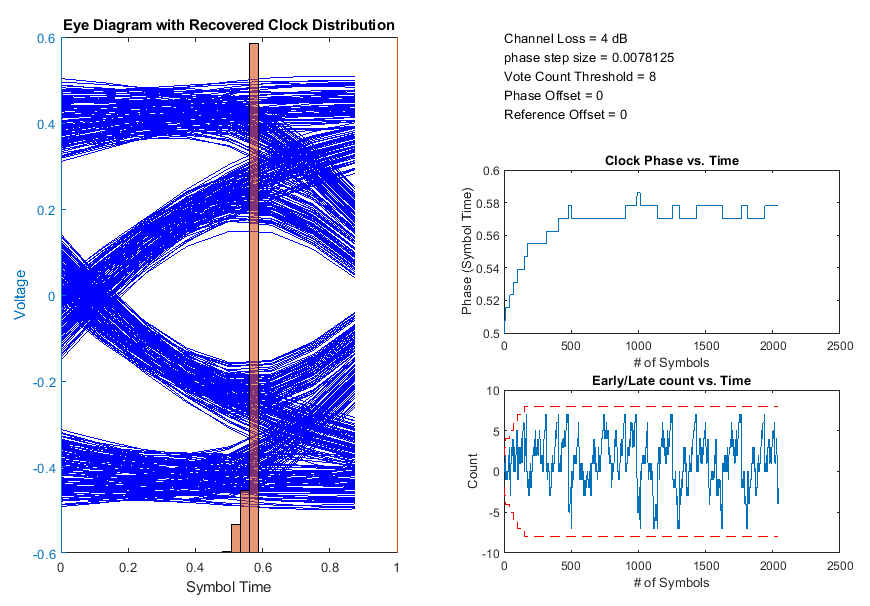

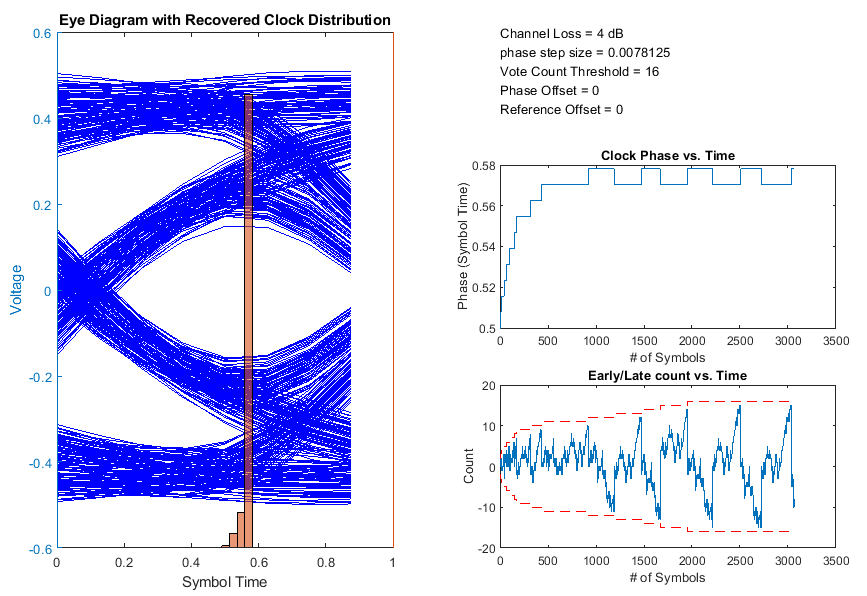

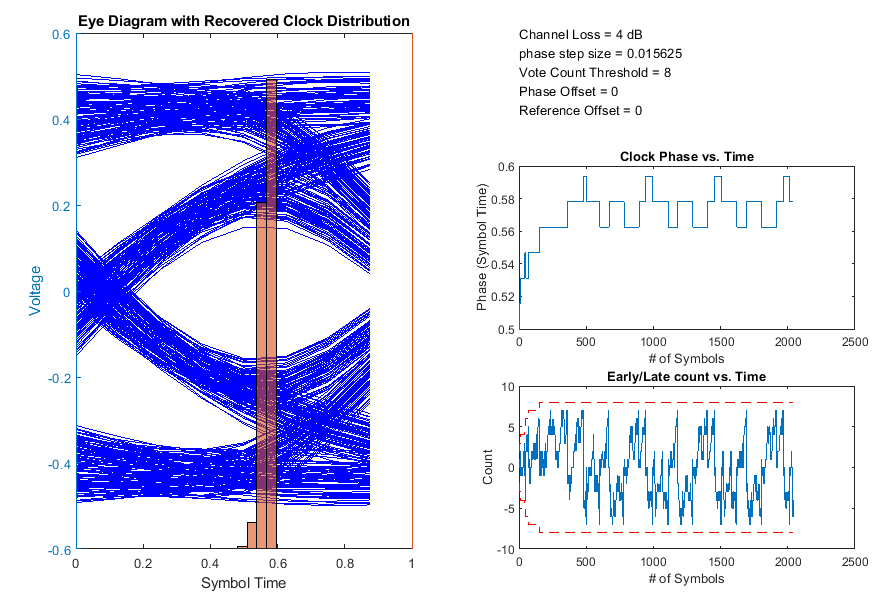

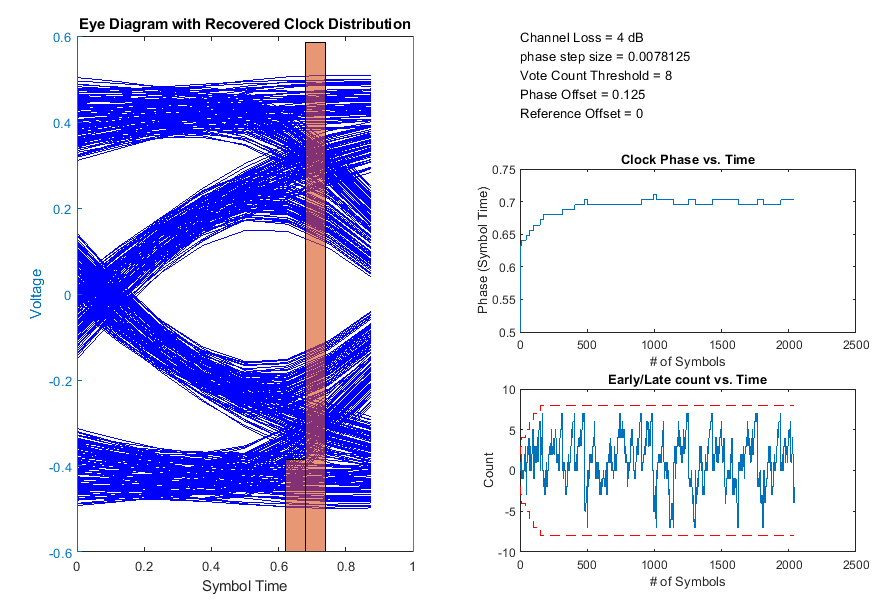

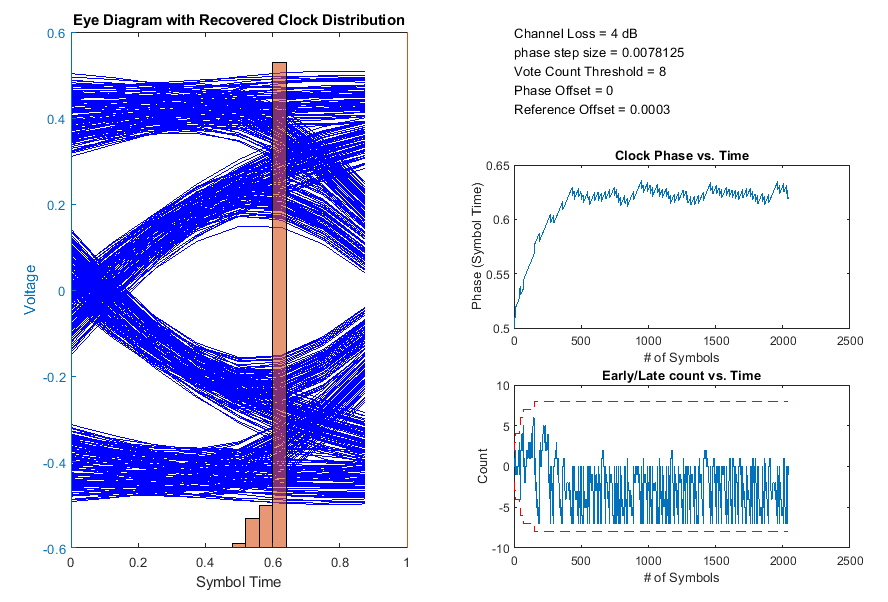

恢复时钟信号从一个重复伪随机二进制序列(PRBS9)不归零(NRZ)信号。考虑频道4 dB损失,相位步长 投票数阈值是8,没有阶段或引用偏移量。

眼图的基线行为显示和时钟产生的概率分布函数(PDF)。PDF是非常靠近眼睛的中心。时钟相位落定之间的一个值为0.5703和0.5781符号时间象征。两个值之间的抖动是非线性的结果砰砰的枪声相位检测器和CDR狩猎抖动的来源。为了减少抖动的大小,减少阶段步长。减少犹豫的时间,减少投票计数阈值。

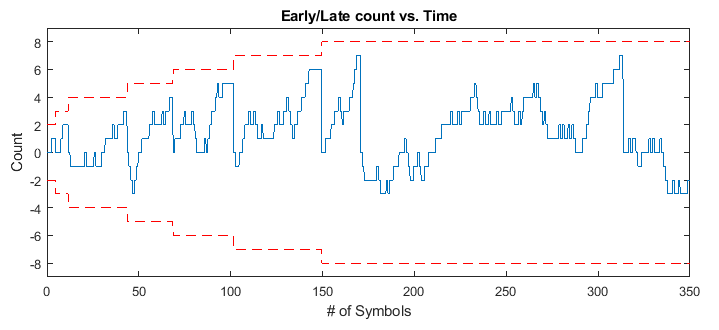

相位检测器的输出中积累早/晚投票计数。当计数超过选票计数阈值,递增或递减阶段。CDR加速收敛,计算阈值从2开始,每次投票的大小超过了阈值,阈值增加,直到达到最大计数。这图显示了前350早/晚数的象征(蓝色)和阈值(虚线红线)。内部的CDR块,投票是递增或递减,在必要时针对阈值,然后检查复位。外部投票值图所示不碰阈值但很明显当投票复位为0。

显示时钟收敛于一个不同的阶段,换频道损失2 dB。时钟相位现在适应约0.35的象征。

增加投票计数阈值为16的结果在一个更大的抖动。

增加阶段步长 增加了抖动大小。

手动移动数据取样器位置平衡的眼睛时不显示左/右对称也可以最大化眼睛的高度。例如,时钟相位转移到正确的 象征着时间的改变输出时钟相位从0.57时间0.7符号象征。

你也可以注入少量的参考时钟频率偏移障碍来实现一个更现实的CDR。

引用

[1]周日,J·l·Stonick, J。“数字时钟和数据恢复架构Multi-Gigabit / s二进制链接。”IEEE固态电路杂志》上,2006年。

[2]哈,B。“挑战在设计高速时钟和数据恢复电路。”IEEE通讯杂志,2002年。