射频接收机的自顶向下设计

本例使用自顶向下的方法为ZigBee®类应用程序设计了一个射频接收器。验证了无损伤设计的误码率,分析加入损伤模型后的误码率性能。该示例使用射频预算分析仪应用程序对影响噪声和非线性预算的元素进行排序。

设计指标:

数据速率= 250 kbps的

OQPSK调制用半正弦脉冲成形,如在IEEE®802.15.4中规定的ZigBee的物理层

直接序列扩频与码片速率= 2 M码片/秒

灵敏度规范= -100 dBm的

误码率(BER)规范= 1E-4

模拟到数字转换器(ADC)具有10个比特和0 dBm的饱和功率

要建立符合标准的全面的ZigBee波形,可以使用用于ZigBee协议的通信工具箱库添加在。

这个例子指导你通过以下步骤:

建立基带发射机的波形生成模型

确定信噪比规格,以实现1e- 4ber从链路级的理想基带模型

从RF接收器和ADC的等效基带模型派生RF子系统规格

从射频接收机的电路包络模型推导出直接转换规范

对干扰信号进行多载波仿真,推导出直流偏置补偿算法

设计和验证基带发射机

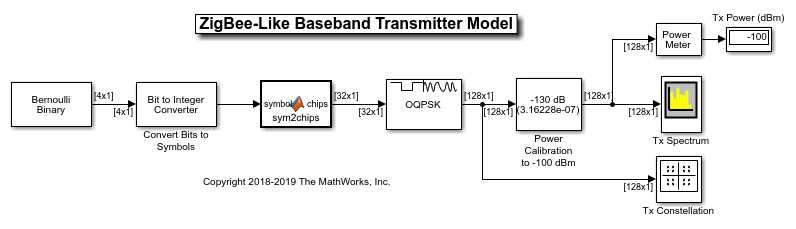

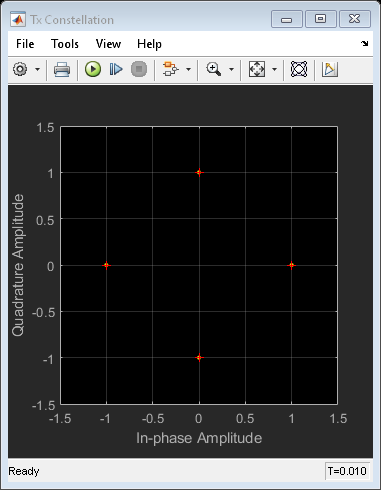

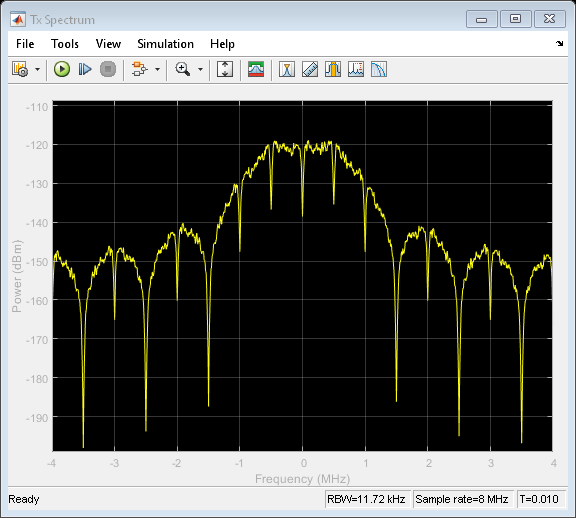

为了评估射频接收机设计的性能,使用具有802.15.4波形代表性的信号频谱是必要且充分的。

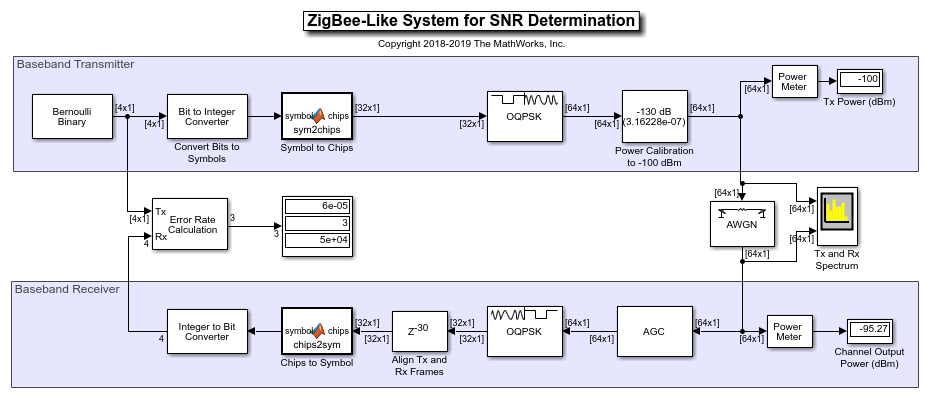

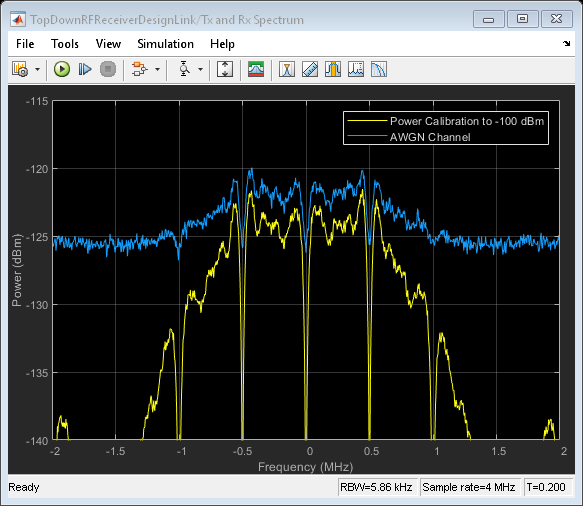

该基带传输模型创建并示出了在光谱和星座域的频谱代表的ZigBee波形。这种模式和所有的后续机型使用回调创建参数化系统MATLAB工作空间的变量。

确定接收机信噪比要求

要设计接收机,首先要确定达到规定的误码率小于1e-4所需要的信噪比。在仿真带宽计算为4mhz时。运行链路级别的模型模拟接收机实现目标误码率所需的处理过程。

准确地计算误码率需要对发射和接收信号进行校准。仿真必须补偿接收信号相对于发射信号的双样本延迟。此外,为了确保正确的芯片到符号到比特的映射,模拟必须在芯片的输入端将芯片与帧边界对齐到帧边界上的符号块。考虑到接收信号延迟和帧边界对齐,需要增加a延迟块恢复接收的符号之前设置到接收器上的分支32-2 = 30的延迟。

该模型在-2.7 dB的信噪比下达到了1e-4 BER,可以通过收集100位错误来验证。

在链路级别的模型中,AWGN块占整个信道和RF接收器SNR的预算。

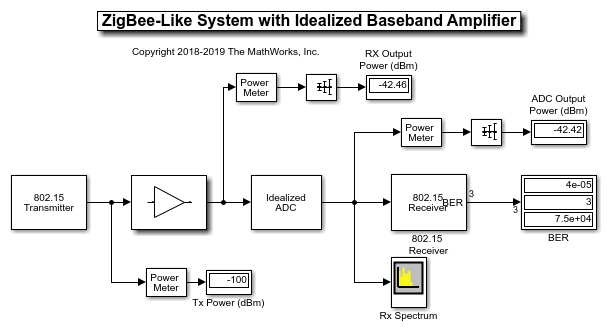

加入ADC并确定接收器的总增益和噪声系数(NF)

本节使用传统的启发式推导来确定射频接收器和ADC的高级规范。

B = 4兆赫=模拟带宽=模拟采样频率

kT = 174 dBm/Hz =热噪声地板功率

灵敏度= -100 dBm的=接收机灵敏度

SNR = -2.7分贝

仿真带宽中的噪声功率= Pn =灵敏度-信噪比= -100 dBm - (-2.7 dB) = -97.3 dBm

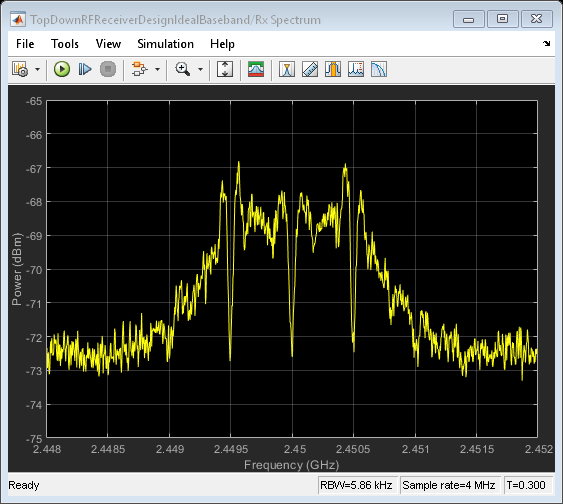

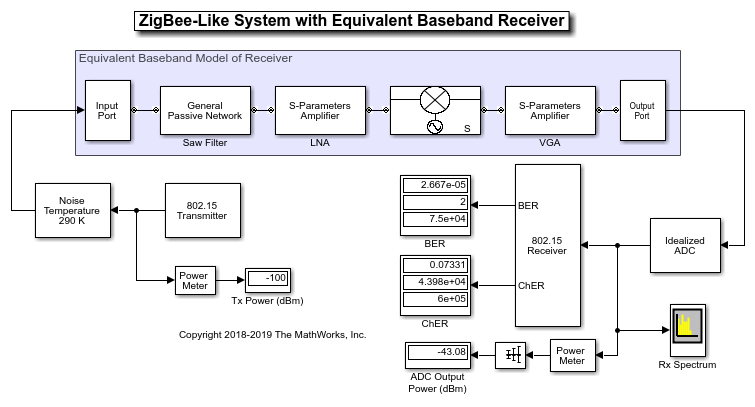

模拟的理想化的基带模型对RF接收机,验证初步的RF接收机规格(NF = 10.7 dB,接收机增益= 53.4 dB)。这可以通过收集100个错误来实现。

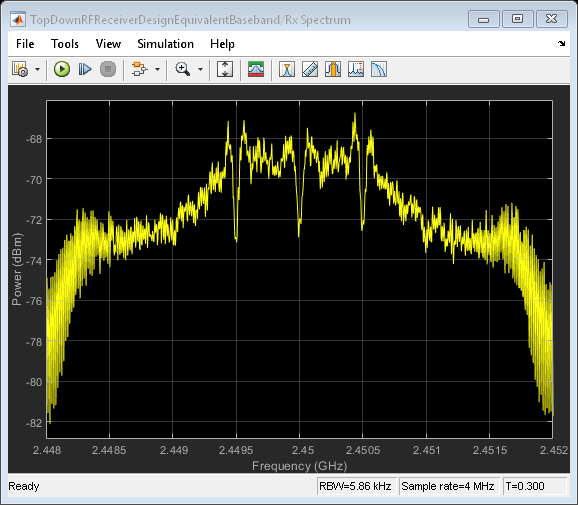

频谱分析仪显示,在没有ADC的情况下,ADC接收到的频谱与前一段的频谱形状大致相同。

细化射频接收机的架构描述

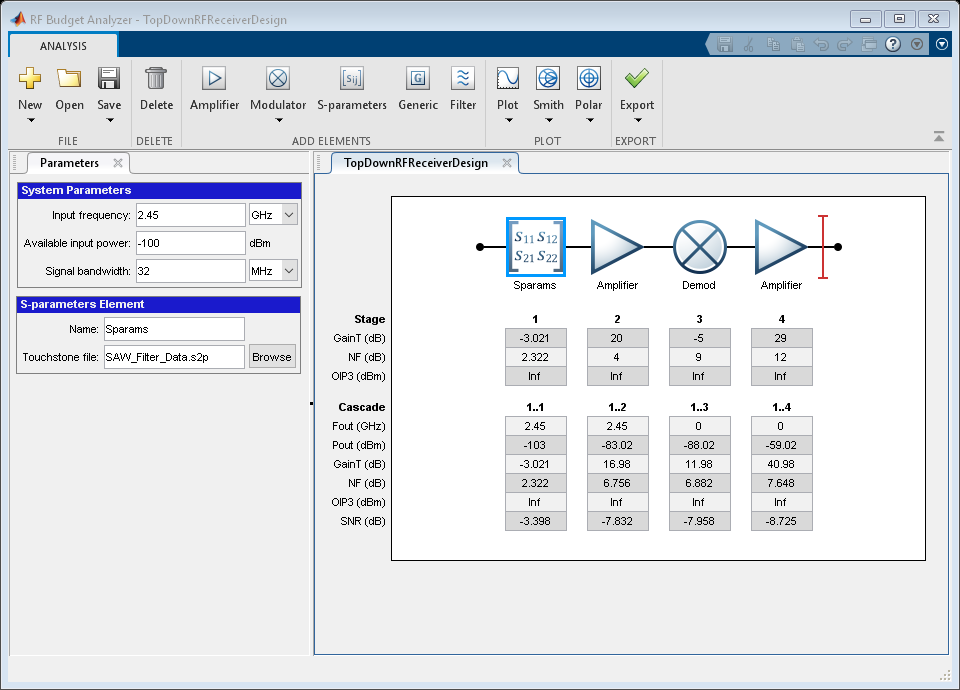

在本节中,射频接收机及其噪声数字和增益预算规范通过使用具有以下特征的四个离散子组件建模:

声表面波滤波器:噪声图= 2.5 dB,增益= -3 dB

LNA:噪声系数= 6分贝增益=22分贝

无源混频器:噪声系数= 10分贝,增益= -5分贝

VGA:噪声系数= 14分贝增益=40分贝

SAW过滤器的性能来自于一个指定s参数特征的试金石文件。您可以在工作频率为2.45 GHz时,通过可视化X-Y平面中的S21参数来验证增益。您可以通过在工作频率为2.45 GHz的X-Y平面上可视化NF参数来验证噪声图。低噪声高增益的低噪声放大器一般采用声表面波滤波器,大大降低了噪声对器件的影响。此外,无源混频器指定一个高IP2。与SAW过滤器类似,您可以通过在用户指定的频率范围[2e9 3e9]上可视化X-Y平面中的S21参数来验证混频器增益。

一个等效基带模型模拟改进的射频接收器。

运行仿真并使用“输出端口可视化”窗格验证射频接收器链路预算。四个阶段的总噪声值和增益按如下预算进行划分:

成分NF(分贝)= [2.5,6,10,14]

分量噪声系数F(线性)= 10 ^(NF / 10)= [1.78 3.98 10.0 25.1]

功率增益(dB)= [-3,22 -5,40] = 54分贝>53.4分贝

电压增益VG(线性)= 10 ^(功率增益/ 20)= [0.71 12.59 0.56 100.0]

系统噪声系数FSYS(线性)=

![$ $ 1 + (F (1) - 1) + {{[F (2) - 1]} \ / {VG (1)}} + {{[F (3) - 1]} \ / {VG (1) \ * VG (2)}} + {{[F (4) - 1]} \ / {VG (1) \ * VG (2) \ * VG(3)}} = 11.8美元](//www.tianjin-qmedu.com/help/examples/comm_simrf/win64/TopDownRFReceiverDesignExample_eq12418652090045556706.png)

系统的噪声系数NFsys(分贝)= 10 * LOG10(FSYS)=10.7分贝

使用此模型,您可以验证BER < 1e-4对应的芯片错误率(ChER)约为7%。通过计算ChER,您可以以更少的时间运行后续模型,并且仍然可以收集准确的BER统计信息。

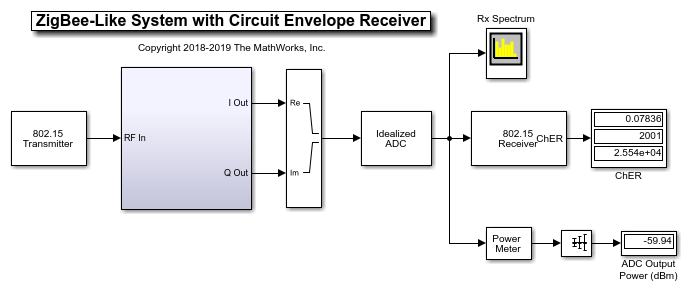

使用电路包络来模拟附加RF减值

使用电路包络建模方法,继续通过添加更多的现实损伤炼RF接收器体系结构。

该电路包络模型从等价基带模式,因为它的射频接收器的不同:

替换等价基带混频器与正交调制器,其由可参数化的I和Q混频器和移相器块,以及与损伤的LO的

用途宽带阻抗(50欧姆),以明确地模拟块之间的动力传递

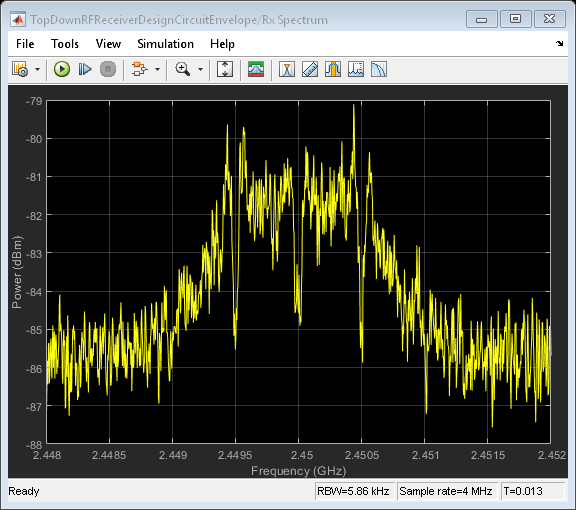

频谱,功率测量,和雪儿相较于等效基带模型,没有显著的性能差异。然而,随着电路包络模型,你可以包括甚至阶非线性效应,I/Q不平衡,和规格的有色噪声分布的每个组件。

可以通过使用块从手动构建射频接收器的电路包络模型电路包络库,或它可自动使用RF预算分析仪应用程序生成。

RF预算分析程序

使用Friis方程确定射频链的噪声、增益和非线性预算

允许您浏览的接收器设计空间,并确定如何在整个链条中的元素分解规格

帮助您确定哪个元素对噪声和非线性预算的贡献最大

可以生成,使用它可以执行多载波模拟和进一步修改的RF接收器的模式。

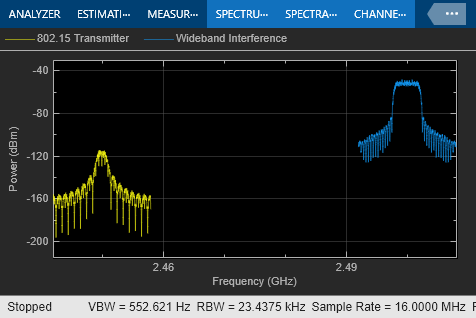

增加宽带干扰、漏损和直流偏移抵消

此部分修改电路包络模型创建这个射频接收机模型包括宽带干扰信号和这些损伤:

在正交解调器中90分贝的低射频隔离

OIP2等于70 dBm的在正交解调器

类似wcdma的阻滞剂,在2500 MHz时为-30 dBm

该仿真模型具有功率和频谱分布特性现实的WCDMA信号兼容非标准的干扰信号。

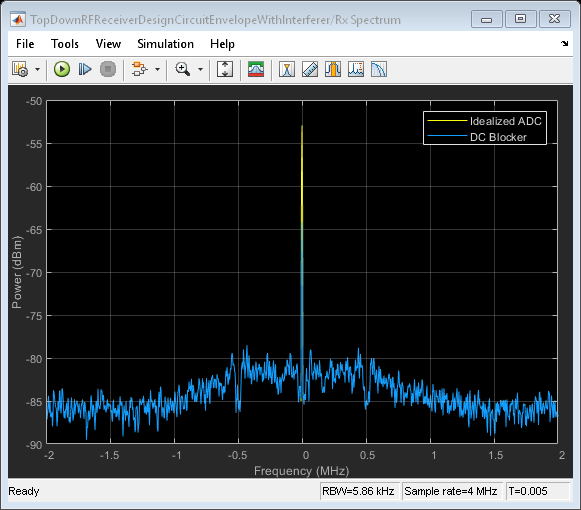

设计需要一个DC偏移补偿算法以实现期望的CHER由于DC偏移从LO泄漏和所引起的高出来的带外干扰信号功率的解调器的非线性的结果。在这种情况下要包含非常有选择性的过滤器,其引入了长延迟与所述CHER测量块相应的计算延迟增加。

频谱的中心在0Hz示出了DC偏移补偿减小DC偏移。当你运行模型,请注意直流偏移最终被完全删除。

结论

采用自顶向下的设计方法,推导出射频接收机组件规范。对损伤、干扰和射频接收机子组件模型进行迭代细化,以提高保真度,并在每个阶段进行验证,以确认实现了整个系统的性能目标。

![$ $ 1 + (F (1) - 1) + {{[F (2) - 1]} \ / {VG (1)}} + {{[F (3) - 1]} \ / {VG (1) \ * VG (2)}} + {{[F (4) - 1]} \ / {VG (1) \ * VG (2) \ * VG(3)}} = 11.8美元](http://www.tianjin-qmedu.com/help/examples/comm_simrf/win64/TopDownRFReceiverDesignExample_eq12418652090045556706.png)