总线中的变体元素

创建具有不同条件的总线

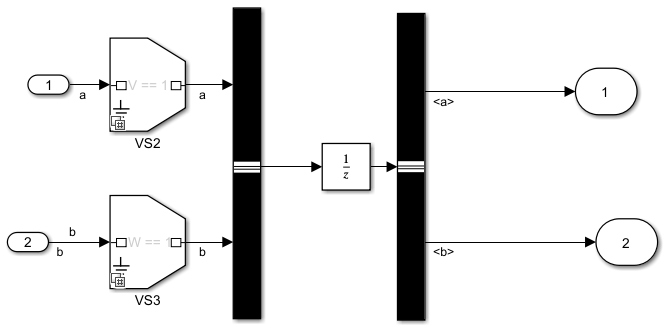

这个例子展示了如何使用具有不同变量条件的元素创建总线信号。这个模型有两个信号(' a ', ' b '),它们被合并成一个总线信号。这两个信号有不同的变异条件,V==1和W ==1。

总线选择器由两个具有两种不同变量条件(V==1和W==1)的信号提供。当这个总线信号被输入到总线选择器中,并且当您从总线中选择单个信号时,变量条件也被选择。

请注意

变体总线支持使用组合端口万博1manbetx作为输入和输出端口。

要查看完成的模型,请打开slexVariantBus模型。

用总线传播可变条件

一个变异来源块可以接受虚拟或非虚拟总线输入。

考虑这个模型。

总线是在V = 1和W = 1的条件下创建的。当条件V和W通过总线传播时,当从总线中选择单个元素时,也会选择条件。

代码生成

您可以为模型生成代码。要做到这一点,就应用程序2 .单击工具条页签嵌入式编码器,然后在C代码选项卡上,单击构建.有关配置模型以生成代码的更多信息,请参见为代码生成准备包含变量的模型.

在使用预处理器条件生成代码时,所有总线输入的总线类型和层次结构必须相同。

虚拟和非虚拟总线行为

虚拟总线提供了在框图中使用总线来减少信号杂波的最简单方法。非虚拟总线支持建模组件(如s函数或万博1manbetxMATLAB函数块),需要显式指定接口。当变量条件通过虚拟或非虚拟总线传播时,变量条件的传播行为不会发生变化。

为虚拟总线生成的代码如下所示。

/*块状态(默认存储)为系统“根> <”* /类型结构体{#如果V == 1 real_TUnitDelay_1_DSTATE;/*< Root > /单元的延迟*/ #定义D_WORK_EX_BUS_VAR_COND_VARIANT_EXISTS #endif /* V == 1 */ #如果W == 1 int32_TUnitDelay_2_DSTATE;/*< Root > /单元的延迟*/ #define D_WORK_EX_BUS_VAR_COND_VARIANT_EXISTS #endif /* W == 1 */ #ifndef D_WORK_EX_BUS_VAR_COND_VARIANT_EXISTS char_rt_unused;#endif} D_Work_ex_bus_var_cond;

为非虚拟总线生成的代码如下所示。

/*块状态(默认存储)为系统“根> <”* /类型结构体{#如果V == 1 || W == 1 myBusUnitDelay_DSTATE;/*< Root > /单元的延迟*/ #define D_WORK_EX_BUS_VAR_COND_VARIANT_EXISTS #endif /* V == 1 || W == 1 */ #ifndef D_WORK_EX_BUS_VAR_COND_VARIANT_EXISTS char_rt_unused;#endif} D_Work_ex_bus_var_cond;

您必须在总线中有一个相关联的总线对象,该对象提供了Simulink所需要的属性万博1manbetx®用于验证总线信号。有关总线对象的更多信息,请参见使用Simulink指定总线属性。万博1manbetx总线对象数据类型.总线中使用的总线对象是无条件的,它生成不受保护的代码,如下所示。

类型定义结构体{real_T一个;int32_Tb;} myBus;

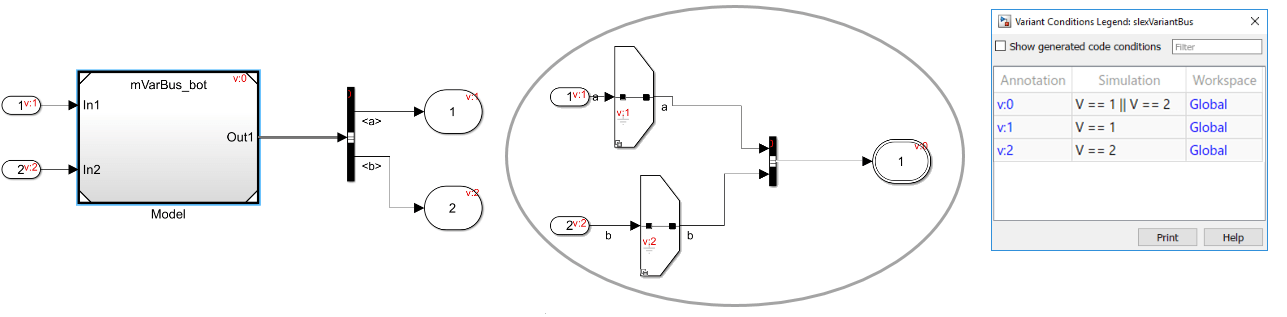

具有模型块的变体总线

考虑这个模型包含模型块。

该模型有两个信号(' a ', ' b '),它们具有不同的变异条件,V==1和V==2。

从模型block时,总线选择器被输入两个具有两种不同变量条件的信号(V==1和V==2)。当您从总线中选择单个信号时,也会选择不同的条件。

已知的限制

不支持状态日志记录块(例如,万博1manbetx单位延迟),它接收一个总线,其中一些元素被移除。