主要内容

MATLAB AXI Master

从MATLAB访问FPGA板上的AXI从存储器®或者模万博1manbetx拟®

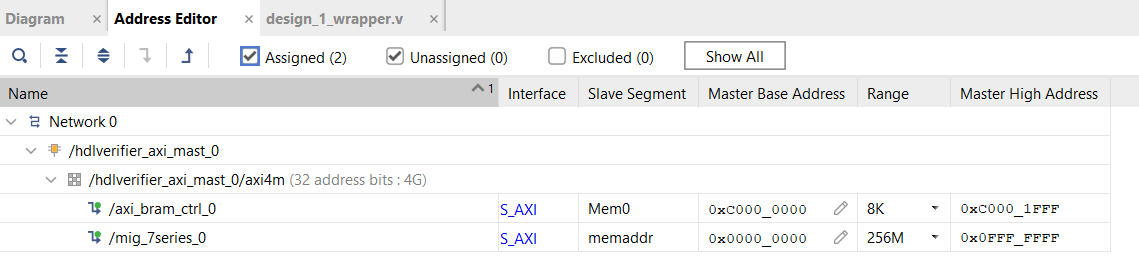

通过使用FPGA设计中的Matlab Axi Master IP,从MATLAB或Simulin万博1manbetxk访问载板内存位置。此IP连接到电路板上的从存储器位置。IP还响应来自MATLAB或SIMULINK,JTAG,PCI Express或以太网电缆的读写命令。万博1manbetx

职能

维瓦多大师 |

添加AXI Master IP路径Vivado项目 |

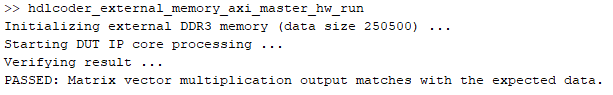

读存储器 |

读取AXI4内存映射从站的数据 |

Writememory. |

将数据写入AXI4内存映射从机 |

释放 |

释放JTAG或以太网电缆资源 |

CopyImageToHostsCardPath |

将特定于板的SD卡图像文件复制到主机SD卡位置 |

loadimagetotargetsdcardpath. |

将特定于板的SD卡图像文件加载到目标SOC设备SD卡位置 |

loadbitstream. |

加载自定义FPGA比特流及其对应的DTB文件到目标SOC设备 |

物体

Aximaster. |

从FPGA板上读取和写入内存位置马铃薯 |

块

| AXI Master阅读 | 读取FPGA板上的内存位置万博1manbetx |

| Axi Master写道 | 从写入FPGA板上的内存位置万博1manbetx |

话题

从MATLAB或Simulink访问FPGA板上内存映射位置的高级步骤。万博1manbetx

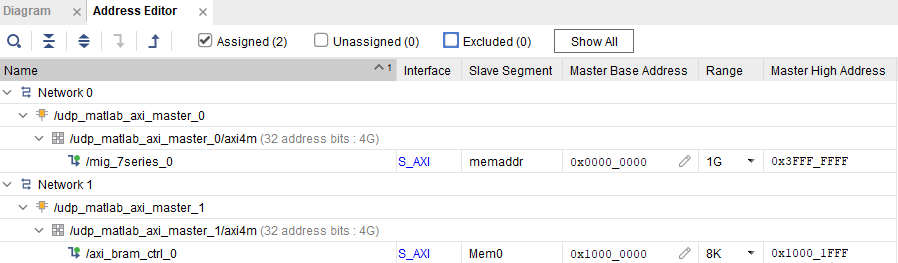

集成和配置以太网MATLAB AXI主站。

Xilinx Zynq SoC设备以太网MATLAB AXI Master

为Xilinx Zynq SoC设备配置以太网MATLAB AXI主机。

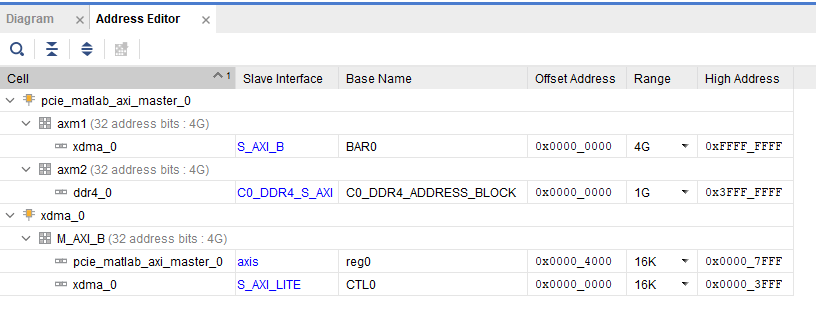

通过PCI Express集成和配置MATLAB作为AXI Master IP。

从Simulink访问FPGA板上的内存映射位置。万博1manbetx

使用Vivado Simulator模拟Matlab Axi主机。