基于AD9361/AD9364模拟器件的ADS-B接收机软硬件协同设计实现

这个例子展示了如何在Zynq无线电平台上实现算法,这些算法被划分在ARM和FPGA结构上。具体来说,这个示例涉及自动相关监视广播(ADS-B)传输的接收和解码,接收功能在硬件和软件中实现,发送波形嵌入在硬件中。

所需产品:s manbetx 845

万博1manbetx

通信工具箱

高密度脂蛋白编码器

Xilinx Zyn万博1manbetxq平台的HDL编码器支持包

嵌入式编码器

万博1manbetx仿真软件编码器

Xilinx Zynq平台嵌入万博1manbetx式编码器支持包

Xilinx zynq无线电通信工具箱支持包(万博1manbetx此包)

简介

本例涉及从空中接收ADS-B传输,或从先前记录的S模式信号接收ADS-B传输,该S模式信号可使用嵌入式传输波形在本地传输。发送和接收FPGA实现被合并到一个HDL IP核上,并在Zynq可编程逻辑(PL)上实现。数据解码在Zynq ARM处理器上通过代码生成运行。一些控制参数被添加到FPGA IP核,以显示如何使用从Simulink访问的AXI4-Lite寄存器实时调整设计。万博1manbetx

设置

如果您还没有这样做,请确保您遵循硬件-软件协同设计的安装在文档中。

Mode S消息介绍

S模式是一种应答机讯问模式,用于根据询问系统的请求传送有关飞机的信息。S模式信号可以是短(56位)或长(112位)。不同模式S消息类型的内容可能有很大差异,尽管大多数将包含有关消息类型、飞机的ICAO24识别地址和循环冗余校验(CRC)校验和的信息。在这个例子中,我们将特别考虑Mode S Extended Squitter (Mode S ES)传输,它是112位信号,可以包含关于飞机的高度、位置、速度、飞行状态和呼号的附加信息。典型模式S ES信号的结构如下图所示。

任何S模式信号的前8位是控制位。这些位包含下行链路格式(DF)的信息,用于描述正在接收哪种类型的模式S消息。对于Mode S ES, DF的值应该等于17。其次是ICAO24代码,这是一个唯一的24位飞机识别代码。S模式ES信号中包含的额外56位信息构成了ADS-B消息。

ADS-B消息的内容是通过其类型代码(TC)来识别的,TC是消息的前5位。根据类型代码的不同,ADS-B消息可以包含有关飞机ID (TC=4)、以高度、纬度和经度(TC=9)表示的机载位置以及水平和垂直速度(TC=19)的信息。本例具体涉及机载位置信息的解码,其结构如下图所示。

模式S信号之前有一个8位的前导模式,接收器使用它来确定是否传输了有效的消息,以及消息位何时开始。信号以1090mhz的数据速率1mbit /s传输,并使用脉冲位置调制(PPM)进行调制,如下图所示。

对于PPM,当一个比特间隔的前半段信号是ON的,后半段信号是OFF的时候,逻辑1得到。同样,当一个比特间隔的前半段信号为OFF,后半段信号为ON时,逻辑0被获得。由于PPM调制对时间非常敏感,因此S模式接收器能够使用序文来确定消息位开始的确切样本是非常重要的。

硬件生成模型

硬件生成模型用于开发希望在FPGA结构上实现的功能。这涉及建模一个hdl优化的ADS-B接收器,以便在PL上实现。在本例中,我们在一块单板上传输和重复(通过使用嵌入式传输波形),然而,该示例可以修改为从空中接收ADS-B信号。这可以通过将接收中心频率从默认的2.4GHz值更改为1090MHz,并禁用发射机块来实现。

硬件/软件划分:一般来说,FPGA的可编程逻辑用于高速率的信号处理,而ARM用于较慢速率的控制功能。在本例中,接收机算法完全在PL中实现,因为匹配滤波和循环冗余检查(CRC)引入了高速率信号处理需求。在PL中也实现了嵌入式发射波形。Tx和Rx算法被放置在两个独立的子系统中HDLTxIpCore而且HDLRxIpCore-在主要的HDL_ADSB子系统。ARM用于将接收到的数据发送回主机进行解码和打印。

该模型包含一个AXI4-lite控制端口,TxTransmitPeriod.这允许控制ADS-B消息的传输速率。的阈值Port设置注册一个正确接收的序文所需的最小接收振幅。发射子系统如下所示。

预录制的ADS-B扩展squitter消息存储在2-D Lookup Table块中,其中每列包含512个样本。方法指定的值TxTransmitPeriod端口。一旦到达周期值,第一个计时器重置,同时在同一实例中增加第二个计时器,后者选择要读取的下一列。第二个计时器每8个周期重置一次,用于存储8个扩展的squitter消息。该模型被配置为允许使用最多4s的传输周期。

接收算法,如下所示,使用一个离散的FIR滤波器块将接收到的数据与前文关联起来。然后,Timing Control状态机使用这个相关值来触发数据的接收。

本例中的定时控制状态机已在MATLAB代码中使用MATLAB函数块实现。如果FIR滤波器输出一个振幅大于阈值的峰值,则检测前导。门限值是使用接收信号功率的估计值动态计算的。定位了序文之后,状态机将等待第一个消息位的开始,然后触发消息的处理。

在一些过程子系统,计算和比较比特周期的前半段和后半段的采样幅值,以确定当前比特是Logic 1还是Logic 0。这可以被认为是PPM解调的一种形式。在这个子系统中还使用了HDL计数器,以便根据系统的4MHz采样率确定每个新位的起始点。对象中的CRC校验和计算和检查CRC子系统,然后将其与收到的校验和进行比较,以确保收到的ADS-B消息是有效的。为了进行这种比较,定时控制状态机将为接收到的消息的最后24位清空CRC寄存器。这可以通过适当地设置EmptyReg信号来实现。

在输出端,接收和处理的数据被一个长S模式信号的长度延迟,并转换为16位整数以方便解码。如果有效输出位于逻辑1,则将使用MATLAB代码对消息进行解码。

该模型可以使用嵌入式发射波形进行运行,以确认其操作HDLTxIpCore子系统。当您运行模型时,接收到的消息将被解码并显示在表格GUI上。

IP核生成流程

一旦您对硬件子系统的模拟行为感到满意,就可以开始生成HDL IP Core的过程,将其与SDR参考设计集成,并生成在ARM上运行的软件。

在为目标定位做准备时,必须通过调用设置Xilinx工具链hdlsetuptoolpath.例如:

> > hdlsetuptoolpath (“ToolName”,“Xilinx Vivado”,“路径”,“C: \ Xilinx \ Vivado \ 2019.1 \ bin \ vivado.bat ');

控件启动目标工作流HDL_ADSB子系统与选择HDL代码/ HDL工作流顾问.

在步骤1.1中选择

IP核生成工作流和适当的Zynq无线电平台的选择:ADI RF SOM, ZC706和FMCOMMS2/3/4, ZedBoard和FMCOMMS2/3/4, ZCU102和FMCOMMS2/3/4, ZC706和FMCOMMS5。

在步骤1.2中,选择

接收和发送路径参考设计。您可以将参考设计参数保留为默认值。

在步骤1.3中,可以使用接口表将用户逻辑信号映射到参考设计中可用的接口信号。在本例中,我们只使用一个通道,因此通道1连接应该连接到如下所示的相关端口。

在步骤1.4中,确保目标频率被设置为一个合理的数字,给定系统的基带采样率。在本例中,采样率为4MHz,因此8MHz左右的合成频率就足够了。

步骤2通过进行一些设计检查,为HDL代码生成准备模型。

步骤3为IP核执行实际的HDL代码生成。

步骤4将新生成的IP核集成到更大的Zynq SDR参考设计中,生成比特流并帮助您将其加载到板上。

按顺序执行每个步骤以体验完整的工作流程,或者,如果您已经熟悉准备和HDL代码生成阶段,请右键单击左侧目录中的步骤4.1并选择运行到选定的任务.

软件生成模型和块库

在步骤4.2中,工作流生成了一个Zynq软件生成接口模型和一个块库。单击

运行此任务按钮,使用默认设置。

软件接口库

类生成的AXI Interface块HDL_ADSB子系统。注意,这只公开了AXI4-lite控制端口,而不公开数据端口。数据端口出现在接收器/发射器块上,代表FPGA用户逻辑和ARM之间的数据接口。如果您在下游模型中使用库块,那么当您运行工作流时,您对HDL子系统所做的任何更新都将自动传播到这个库,然后传播到软件生成模型。在本例中,硬件生成模型不包含任何SDR传输或接收块,因此无法填充这些块上的参数。使用库块时,必须确保为应用程序正确配置参数。

软件接口模型

软件接口模型可以作为针对Zynq的完整软件开发的起点:外部模式模拟、处理器在环和完全部署。注意,这个生成的模型将在每次运行步骤4.2时被覆盖,因此建议将这个模型保存在一个唯一的名称下,并在其中开发软件算法。提供了一个软件接口模型,它展示了您可以如何决定构建这个模型,请参阅部分在Zynq板上运行软件和硬件.

位流生成和加载

工作流的其余部分用于为FPGA结构生成位流,并将其下载到电路板上。

在步骤4.3中,工作流顾问为FPGA结构生成一个位流。您可以通过勾选所选选项来选择在外部shell中执行此步骤

在外部运行构建过程.此选择允许您在构建FPGA映像时继续使用MATLAB。在完成一些基本的项目检查后,该步骤将在几分钟内完成,并且该步骤将被标记为绿色复选标记。但是,必须等到外部shell显示成功的位流构建后才能继续下一步。

步骤4.4下载比特流到设备上。在继续此步骤之前,调用

zynq函数,以确保MATLAB设置为正确的无线电硬件的物理IP地址。

>> devzynq = zynq(“linux”,“192.168.3.2”,“根”,“根”,“/ tmp”);

默认情况下,无线硬件的物理IP地址为192.168.3.2。如果在硬件设置过程中更改了无线电硬件IP地址,则必须提供该地址。

或者,如果你想在外面加载比特流工作流的顾问,创建一个SDR无线电对象并调用downloadImage函数在对象上。

如果在步骤1.1中,您选择了ADI RF SOM, ZC706和FMCOMMS2/3/4, ZedBoard和FMCOMMS2/3/4,或ZCU102和FMCOMMS2/3/4无线电设备,创建一个AD936x无线电对象。

>> radio = sdrdev(“AD936x”);

如果在步骤1.1中选择了ZC706和FMCOMMS5无线电设备,则创建一个FMCOMMS5无线电对象。

>> radio = sdrdev(“FMCOMMS5”);

下载比特流使用无线电对象接口选定的无线电设备。

> > downloadImage(广播,“FPGAImage”,...“hdl_prj \ vivado_ip_prj \ vivado_prj.runs \ impl_1 \ system_top.bit ')生成的比特流的路径

在Zynq板上运行软件和硬件

提供了一个软件界面模型,它展示了如何修改生成的模型,以将其设置为ADS-B Mode S示例。该接口模型将允许您运行该模型监视和调优模式或完全部署。

注意,发射器块仍然有一个数据输入。即使没有数据从ARM发送到FPGA,这个块也需要初始化所需的RF参数并启用传输数据路径,因此它必须包含在接口模型中。

该模型已配置为使用Xilinx Zynq-7000基于板目标运行以下硬件:ADI RF SOM ZedBoard和FMCOMMS2/3/4 ZC706和FMCOMMS2/3/4/5

如果您正在使用ZCU102和FMCOMMS2/3/4,双击“Selected Hardware Board Target”块以更改配置,以使用Xilinx Zynq UltraScale+ MPSoC ZCU102 IIO Radio板目标。

该模型已配置为从计时器驱动的调度器运行。下游解码和显示处理将在接收到由数据有效输出控制的有效波形时进行。如果没有收到有效的ADS-B信号,从FPGA接收数据的尝试将超时。

为了在本例中成功接收ADS-B信号,您可以采用以下两种方式之一:

探测到空中的信号。对于这个选项,您需要将接收块的中心频率设置为ADS-B传输频率,即1090MHz。你还应该注释掉发射机块,以确保没有干扰信号被传输。

使用所提供的嵌入式发射波形。在这种情况下,发射块的中心频率应设置为在您所在区域使用的未经许可且合法的频率,接收块应设置为相同的中心频率。

监视和调优模式允许您从Simulink模型控制配置。万博1manbetx您还可以完全部署设计以在板上运行,与Simulink断开连接。万博1manbetx2 .在“Si万博1manbetxmulink”工具栏中单击构建、部署和启动.在此模式下,您将无法调优参数。

一旦ARM成功地接收到ADS-B消息,它就会使用软件接口模型中的UDP发送块通过以太网链路将结果发送回主机。UDP发送块已经使用主机的默认IP地址“192.168.3.1”配置。如果在硬件安装过程中更改了IP地址,则必须提供该地址。提供了一个简单的UDP接收模型,其中有一个MATLAB函数块用于解码接收的消息。

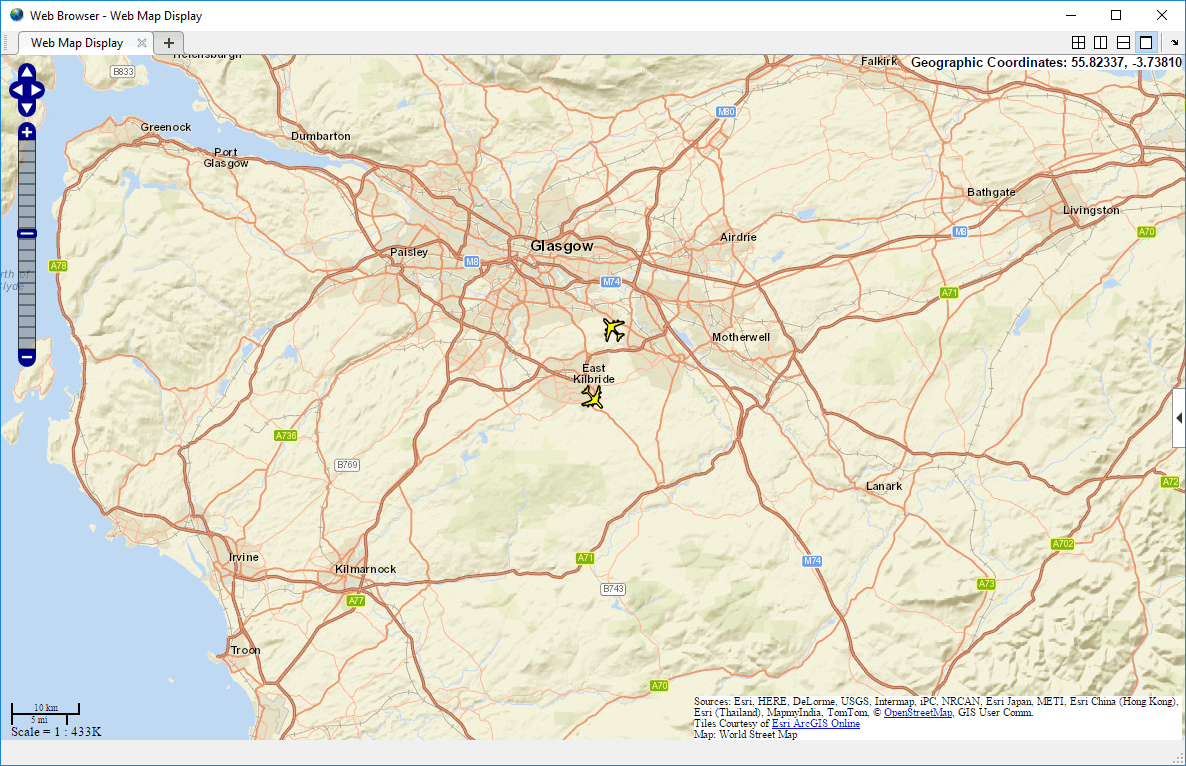

解码后的信息显示在表格图形用户界面上,如果按下按钮,可以将更详细的信息记录到文本文件中开始登录按钮。如果你想观察你所在地区的飞机交通情况,你必须将你的接收器调到1090MHz的接口模式。

此外,如果您拥有映射工具箱的有效许可证,则可以在地图上观察平面。这个例子所记录的波形包含了8个捕捉到的ADS-B扩展的两个不同航班的斜射信息。对于每一次飞行,有2个机载位置(TC=9), 1个飞机ID (TC=4)和1个垂直速度(TC=19)消息,这些消息以规则的速率重复传输TxTransmitPeriod控制端口。