直方图均衡化

此示例演示如何使用Vision HDL工具箱™ 直方图库块实现直方图均衡化。

此示例模型提供了一个硬件兼容的算法。您可以从该算法生成HDL代码,并使用Xilinx在板上实现它™ Zynq™ 参考设计。参见基于Zynq的硬件直方图均衡化(基于Xilinx Zynq的硬件的Vi万博1manbetxsion HDL工具箱支持包).

介绍

该模型展示了如何利用直方图库块应用直方图均衡化来增强图像的对比度。要了解更多,请参阅直方图块引用页。在这个直方图均衡化示例中有三个组件。

视频分割将一幅大图像分割成四幅不重叠的小图像,用于并行直方图计算。

高密度直方图计算图像的累积直方图。

均衡化将均衡直方图应用于原始图像并生成对比度增强图像。

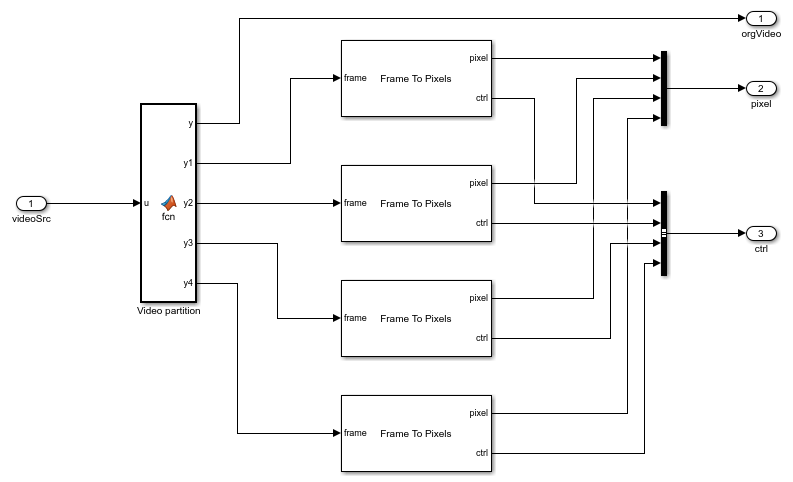

视频分割

在某些使用情况下,直方图是在整个图像上计算的,或者在表示图像部分的感兴趣的小区域上计算的。计算大图像的直方图非常耗时。本例中的视频分割组件将大图像分割为四个不重叠的小图像。直方图是在四个小图像上计算的同时,每个输入帧被划分成四个120×160的小图像。每个小图像连接到一个帧到像素块,以生成像素流和相应的控制信号。

高密度直方图

高密度直方图子系统针对HDL代码生成进行了优化。使用直方图块计算像素流的直方图。由于输入图像为灰度级,数据类型为uint8,因此将输入像素分组到256个存储单元中。一旦该存储单元断言就绪的信号。bin值被发送用于累积直方图计算。在读取所有256个bin值之后,模型进行断言宾塞将所有容器重置为零。然后将收集到的每个小图像的直方图相加,计算出大图像的累积直方图。

读取和重置直方图存储箱的时序图如下图所示。

均衡化

直方图均衡化可应用于计算累积直方图的当前帧或之后的帧。如果应用于当前帧,则需要存储输入视频。此示例将输入视频延迟一帧,并对原始视频执行均匀均衡。然后将均衡后的视频与原始视频进行比较原创视频。

HDL代码生成

利用Xilinx ISE在Virtex6 (XC6VLX240T-1FFG1156) FPGA上合成了由直方图生成的HDL代码,电路运行在190 MHz左右,足以实现数据的实时处理。

要检查并生成此示例的HDL代码,您必须拥有HDL编码器™ 许可证

您可以使用这些命令

makehdl(“组织图定性HDL/HDL组织图”)

或

makehdltb(“组织图定性HDL/HDL组织图”)

为HDL示图子系统生成HDL代码和测试台。注:由于数据量大,测试台生成需要很长时间。在生成测试台之前,考虑减少仿真时间。