滤波OFDM(F-OFDM)发射机的HDL码生成

滤波OFDM(F-OFDM)对发射机中IFFT后的符号应用滤波器,以提高带宽,同时保持复杂符号的正交性。此示例实现了用于HDL代码生成的发射机F-OFDM。该示例显示如何从MATLAB®参考模型转换为HDL优化Simulink®模型。包括从doubl转换e转换为定点类型,并最大限度地减少FPGA上设计的资源使用。万博1manbetx

提到F-OFDM与OFDM调制用于比较OFDM和F-OFDM波形。

系统参数

设置所需的F-OFDM属性。

NDLRB=108;波形类型=“F-OFDM”;子载波间隔=60*1e3;%赫兹CellRefP=1;CyclicPrefix=“正常”;过滤器长度=513;音调偏移=2.5000;周期延长=“关”;

打电话给h5gOFDMInfo函数计算F-OFDM参数。该方法计算FFT长度、循环前缀长度和子载波数。

genb=struct(“NDLRB”,NDLRB,...“波形类型”,波形类型,....“子载波间隔”,子载波间隔*1e-3,...“过滤器长度”,过滤器长度,...“音调偏移”,音调偏移,...“CellRefP”,CellRefP,...“CyclicPrefix”,CyclicPrefix,...“周期扩展”,cyclecextension);info=h5gOFDMInfo(genb);

生成输入数据的网格

调音=“64QAM”;TotSubframes=5;[txgrid,bitsIn]=generateOFDMGrid(genb,info,QAMModulation,TotSubframes);

参考MATLAB模型

参考模型运行浮点F-OFDM系统并绘制频谱。使用参考模型与支持HDL代码生成的定点模型进行比较。万博1manbetx

[txSig_ref,txinfo]=h5gOFDMModulate(genb,txgrid);

通过向信号中添加噪声对信道进行建模。

snrdB=18;S=RandStream(‘mt19937ar’,“种子”,1);rxSig_ref=awgn(双(txSig_ref),snrdB,“测量”,S);

接收到的信号必须同步并对齐。在实际情况下,接收器包括符号同步。在本例中,接收器通过发射机滤波器校正帧的偏移 .

.

rxSig_ref_sync=循环移位(rxSig_ref,-地板(滤波器长度/2));

恢复数据、计算误码率并显示星座图。

[constDiagRx,ber,rxgrid_ref]=FOFDM_接收器(rxSig_ref_sync,bitsIn,genb,...QAMModulation,“F-OFDM接收(REF)”);disp([“F-OFDM接收(REF)”,“贝尔”num2str(ber(1))“至少num2str(snrdB)“dB”]);constDiagRx(rxgrid_ref(:);

信噪比为18 dB时F-OFDM接收(参考)误码率为0.0094568

频谱显示子带信号的带外辐射明显改善,有效带宽增加。

FOFDM传输频谱(txSig_参考,txinfo,genb,“F-OFDM频谱(REF)”);

万博1manbetxSimulink定点模型

模型=“FOFDMTransmitterthdlexample_FixPt”加载系统(模型);开放系统(模型,“/F-OFDM”]);

要从模型生成HDL,必须使用定点数据类型,而不是双精度数据类型。对于64点QAM,至少需要6位+1符号位。然而,考虑到FPGA的局限性,为了获得合理的误码率,必须增加输入字长。FPGA中的乘法器具有有限的输入字长。例如,Xilinx的DSP48具有18*25位乘法器。为了优化设计,选择字长,以便FFT和滤波器中的所有乘法器都小于18*25位乘法器。在此示例中,FFT HDL优化块使用“将蝶形输出除以二”选项。输入字长度为16位。

通过设置WORDLENGTH=-万博1manbetx1,可以使用浮点数据运行Simulink模型。但是,HDL代码生成不支持此模式。万博1manbetx

字长=16;

将小数位数设置为字长-2位,以覆盖-1<=符号<=1。

FRACTIONLENGTH=字长-2;

生成OFDM符号

IFFT的输入数据假定为适当的OFDM符号,并驻留在内存中(模型中的OFDM符号子系统)因此,发射机的采样率取决于存储器中的数据可用性和FPGA时钟频率。如果数据始终可用,则采样率限制为

.

.

另一方面,所需的采样率通过以下公式计算: 在这个例子中,它等于122.88 Msps。要达到122.88 Msps,时钟频率应至少为135.36 MHz。

在这个例子中,它等于122.88 Msps。要达到122.88 Msps,时钟频率应至少为135.36 MHz。

ifftin=generateOFDMSymbol(txgrid,info,genb);

滤波器设计

适当的滤波器应在子载波上具有平坦的通带和急剧的过渡以最小化保护带。它还需要足够的阻带衰减。原型滤波器 在哪里使用

在哪里使用 是一个SINC函数,并且

是一个SINC函数,并且

.

.

fnum=generateFilterCoef(genb,info);

模拟

设置模型并运行。请注意,由于系统延迟,需要更长时间模拟模型以收集足够的数据。

Nfft=info.Nfft;CyclicPrefixLengths=info.CyclicPrefixLengths;SymbolsPerSubframe=info.SymbolsPerSubframe;停止时间=4*TotSubframes*info.SamplesPerSubframe;sim(型号);txSig_fixpt=TX_波形(1:大小(txSig_ref));

通过向信号中添加一些噪声对信道进行建模。请注意,使用的噪声与参考MATLAB模型中使用的噪声相同。

S=RandStream(‘mt19937ar’,“种子”,1);rxSig_fixpt=awgn(double(txSig_fixpt),snrdB,“测量”,S);

执行符号同步、恢复数据、计算误码率并显示星座图。

rxSig_fixpt_sync=circshift(rxSig_fixpt,-floor(genb.FilterLength/2));[constDiagRx,ber,rxgrid_fixpt]=FOFDM_接收机(rxSig_fixpt_sync,bitsIn,...genb,QAMModulation,'F-OFDM接收(定点)');disp(['F-OFDM接收(定点)',“贝尔”num2str(ber(1))“至少num2str(snrdB)“dB”]);constDiagRx(rxgrid_fixpt(:);

信噪比为18 dB时F-OFDM接收(定点)误码率为0.0094453

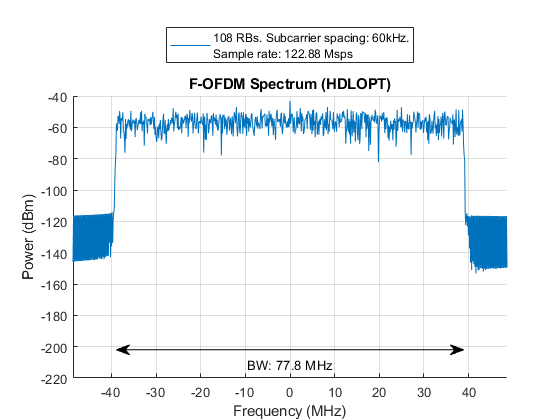

频谱显示,即使对于固定点,子带信号的带外辐射也有明显改善,有效带宽也有所增加。

FOFDM传输频谱(txSig_fixpt、txinfo、genb、,‘F-OFDM频谱(定点)’);

万博1manbetxSimulink HDL优化模型

定点模型在时域中使用513抽头滤波器。由于IFFT的输出很复杂,该滤波器需要2*513乘法器。即使使用对称滤波器实现,也需要513乘法器,这对于正常大小的FPGA来说太多了。为了减少滤波器中的乘法器数量,HDL优化模型滤波器在频域中。频域FIR滤波器要求输入的FFT乘以系数的FFT,然后IFFT结果。在这种情况下,复数乘法器的数量为

.

.

本例中的频域滤波器使用11个复数乘法器。请注意,实数乘法器的实际数量取决于FFT和IFFT块设置(复数乘法选项)在HDL优化模型中,时域FIR滤波器被采用重叠存储结构的频域FIR滤波器取代。由于重叠存储结构的重叠特性,采样率被限制在

.

.

因此,为了实现该示例的122.88 Msps采样率,时钟频率必须至少为196.8 MHz。

模型=“FOFDMTransmitterthdlexample_HDLOpt”加载系统(模型);开放系统(模型,“/F-OFDM”]);

设置滤波器的FFT长度。对于频域滤波,长度必须至少为2*滤波器长度。然而,由于它必须一次处理整个OFDM符号,所以在滤波器内部使用Nfft作为FFT长度。然后,计算系数的FFT。位反转由于滤波器的FFT输出是位反转的结果。

filterftlen=Nfft;fftFnum=bitrevorder(fft(fnum,filterftlen)。');

对于定点输入数据,滤波器内FFT的输出具有位增长=log2(Nfft)=11位。若要将大多数乘法器映射到FPGA中的DSP块,请限制输入字长。例如,如果DSP有一个25*18位乘法器,则字长必须为14位,以实现滤波器内FFT的25位输出。此外,使用18位系数。

WORDLENGTH=14;FRACTIONLENGTH=WORDLENGTH-2;如果字长>0%对于定点数据COEF_WL=18;COEF_FR=COEF_WL-2;fftFnum=fi(fftFnum,1,COEF_WL,COEF_FR,“取整法”,“最近的”,...“溢出动作”,“包装”);终止STOPTIME=4*TotSubframes*info.SamplesPerSubframe;sim(型号);txSig_HDLOpt=TX_波形_HDLOpt(1:大小(txSig_参考));

通过向信号中添加一些噪声对信道进行建模。请注意,使用的噪声与参考MATLAB模型中使用的噪声相同。

S=RandStream(‘mt19937ar’,“种子”,1); rxSig_HDLOpt=awgn(双(txSig_HDLOpt),snrdB,“测量”,S);

执行符号同步、恢复数据、计算误码率并显示星座图。

rxSig_HDLOpt_sync=circshift(rxSig_HDLOpt,-floor(genb.FilterLength/2));[constDiagRx,ber,rxgrid_HDLOpt]=FOFDM_接收机(rxSig_HDLOpt,sync,bitsIn,...genb,QAMModulation,‘F-OFDM接收(HDLOPT)’);disp([‘F-OFDM接收(HDLOPT)’,“贝尔”num2str(ber(1))“至少num2str(snrdB)“dB”]);constDiagRx(rxgrid_HDLOpt(:);

信噪比为18 dB时F-OFDM接收(HDLOPT)误码率为0.010038

频谱显示,即使对于固定点,子带信号的带外辐射也有明显改善,有效带宽也有所增加。

FOFDM传输频谱(txSig_HDLOpt,txinfo,genb,“F-OFDM频谱(HDLOPT)”);

生成HDL代码和测试台

为生成的文件使用临时目录:

systemname='fofdmtransmitterthdlexample_HDLOpt/F-OFDM';workingdir=tempname;

您可以运行以下命令来检查F-OFDM子系统的HDL代码生成兼容性:

checkhdl(系统名,'TargetDirectory',workingdir);

运行以下命令以生成HDL代码:

makehdl(系统名,'TargetDirectory',workingdir);

运行以下命令以生成测试台:

makehdltb(系统名,'TargetDirectory',workingdir);

综合结果

该设计针对Xilinx Zynq-7000(xc7z045-ffg900,速度等级2)进行综合设计使用Vivado。该FPGA具有900个DSP48片,因此,该设计的定点版本不适合该设备。HDL优化版本的设计适合该芯片,并实现205.8 MHz的时钟频率,满足196.8 MHz的时钟频率要求。该设计使用94个DSP48(10%)和24个块RAM(4%)。

结论

在本例中,开发并优化了Simulin万博1manbetxk定点模型的硬件。该模型通过在FPGA上优化DSP的使用来最小化资源使用。将浮点模型的结果与定点模型的结果进行比较表明,16位数据具有与浮点数据相似的误码率。