简单锁相环模型的设计与评价

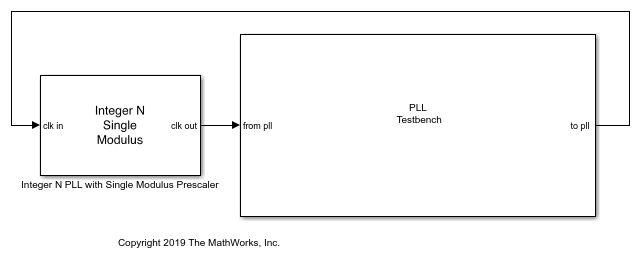

这个例子展示了如何使用参考架构设计一个简单的锁相环(PLL),并使用PLL Testbench验证它。

锁相环是一种频率合成器系统,它产生的输出信号的相位取决于输入信号的相位。在最简单的形式中,锁相环由相位/频率检波器(PFD)、电荷泵、环路滤波器、压控振荡器(VCO)和反馈回路中的时钟分压器组成。PFD和电荷泵一起产生一个与两个输入信号相位差成正比的误差信号。环路滤波器去除误差信号的高频成分,从而驱动VCO。VCO的输出通过时钟分压器馈送到PFD的输入,产生负反馈回路。

Mixed-Signal Blockset™提供了设计简单锁相环模型的参考架构和测试平台,以验证所设计的模型符合设计规范。

建立锁相环试验台模型

打开模型simplePLL作为支持文件附在本示例中。万博1manbetx该模型由一个带单模量预标器的整数N锁相环块和一个锁相环试验台块组成。

open_system (“simplePLL.slx”)

锁相环规格和减值

使用的数据表Skyworks SKY73134-11设计锁相环系统锁相频率为2.8 GHz。

双击“整数N锁相环与单模量预分频器”块,打开“块参数”对话框,并验证这些设置:*检查在PFD而且电荷泵选项卡。*在电荷泵选项卡,输出电流设置为2.7妈的死区补偿而且输入阈值参数保持默认值。

在VCO选项卡,VCO的敏感性设置为

20.MHz / V。的自由运行频率略低于目标锁定频率并设置为2.78GHz。的相位噪声频率偏移设置为[100e3 1e6 3e6 10e6]Hz和相位噪声电平(dBc/Hz)设置为[−108−134−145−154]dBc / Hz。

考虑到锁相环的参考输入频率为

1.6兆赫,时钟分频值和最小时钟分频值在预定标器TAB设置为 .

.

在循环过滤选项卡,环路带宽设置为

160kHz,参考输入频率的十分之一。相位裕度默认为45度。过滤组件值自动计算。

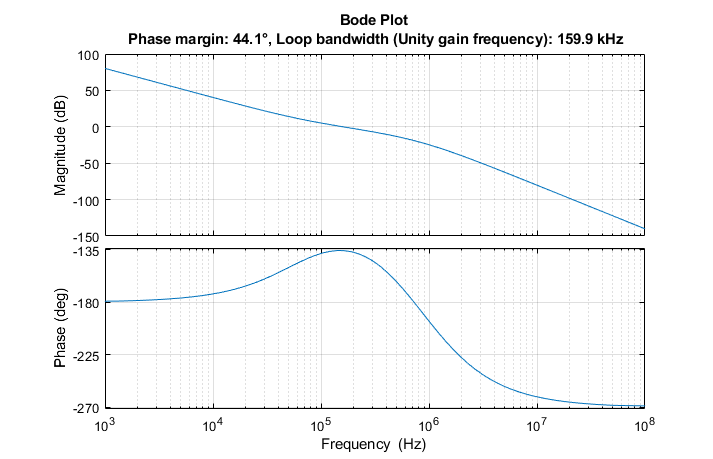

在分析选项卡,开环分析而且闭环分析已选择地块。

图预模拟锁相环动力学

单击情节循环动态按钮,查看预仿真结果,评估系统稳定性。

闭环分析包括极点-零点映射、幅度响应、阶跃响应和脉冲响应。系统3db带宽为288.51kHz。系统稳定。

开环分析由锁相环系统的波德图组成。相位裕度为44.1度和单位增益频率是159.9kHz。

改进相位噪声测量锁相环试验台

双击PLL Testbench打开块参数对话框,并验证这些设置刺激tab时,锁相环的输入信号定义为的方波1.6MHz。

在设置Tab,检查相位噪声选择测量选项。操作频率而且锁定时间取消选择测量选项。设置分辨率带宽来

50kHz,不。光谱平均值来4而且拖延时间来1.5 e-5年代。

在目标指标选项卡,设置相位噪声(dBc/Hz)来

[−108−134−145−154],与锁相环相位噪声剖面相同。

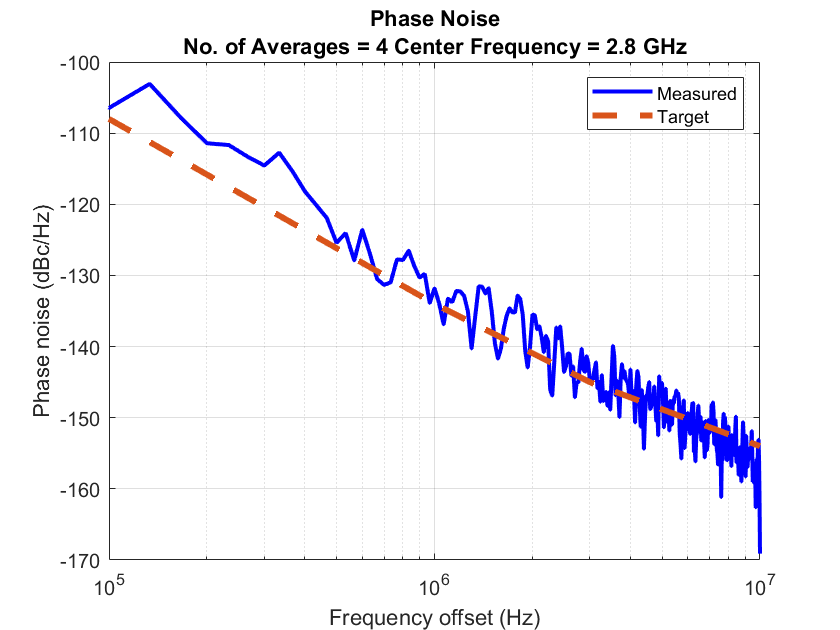

绘制锁相环相位噪声剖面

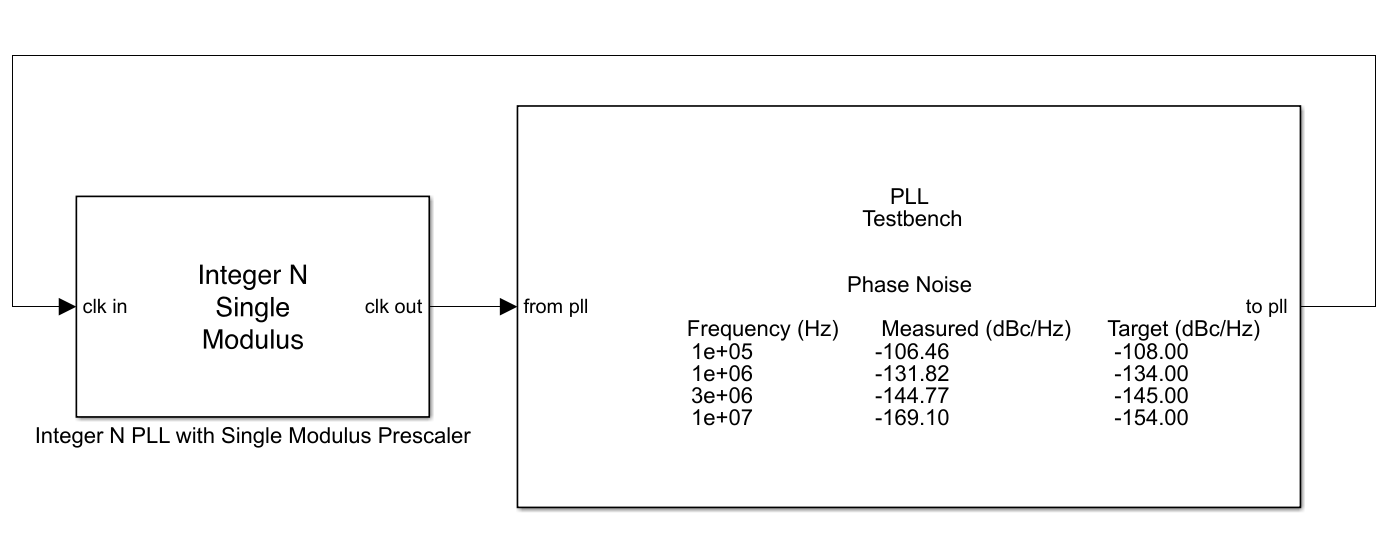

运行模拟1.35的军医s.仿真结果显示在锁相环测试台的图标上。在特定频率偏移处测量的相位噪声电平与其目标值一致。

双击PLL Testbench块,打开块参数对话框。单击图相位噪声剖面按钮。锁相环的工作频率为2.8GHz,测量的相位噪声轮廓与目标轮廓相匹配。