级联逻辑块的MCDC分析

此示例说明了Simulink®覆盖率是如何实现的™ 记录逻万博1manbetx辑运算符块级联的MCDC度量。

示例模型

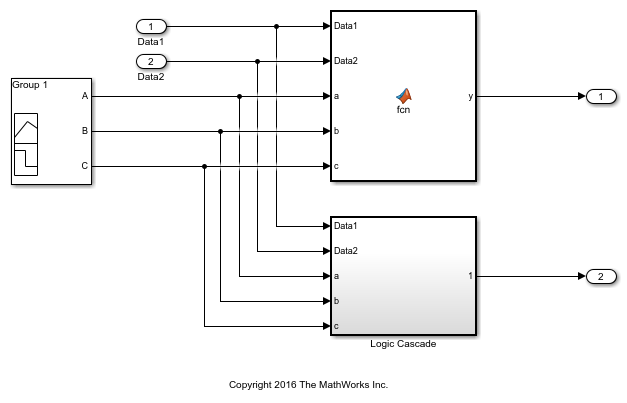

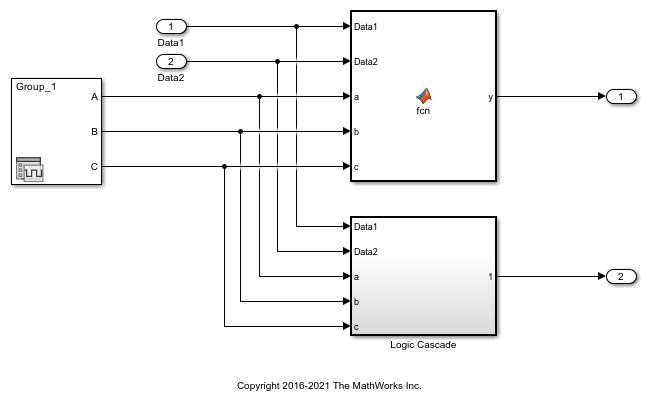

在Si万博1manbetxmulink中,有多种实现布尔逻辑的方法,例如通过使用如果MATLAB函数块中的语句,状态流图中的条件转换,或级联中连接在一起的多个逻辑运算符块的组合。

示例模型slvnvdemo_cv_逻辑_级联通过在MATLAB功能块中使用MATLAB代码以及级联逻辑运算符块,实现相同的布尔表达式。

使用以下命令打开模型slvnvdemo_cv_逻辑_级联:

open_system (“slvnvdemo\u cv\u逻辑\u级联”);

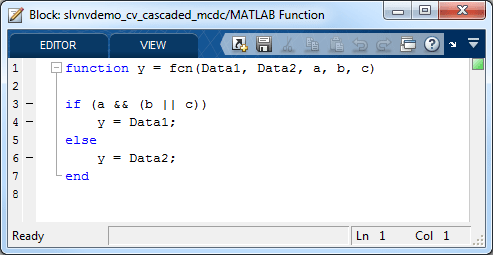

打开MATLAB功能块以查看相关函数。

open_system (“slvnvdemo_cv_logic_cascade / MATLAB函数”)

在MATLAB功能块中,如果(a && (b | | c))如果是真的,那么信号数据1将输出;否则,信号数据2是输出。

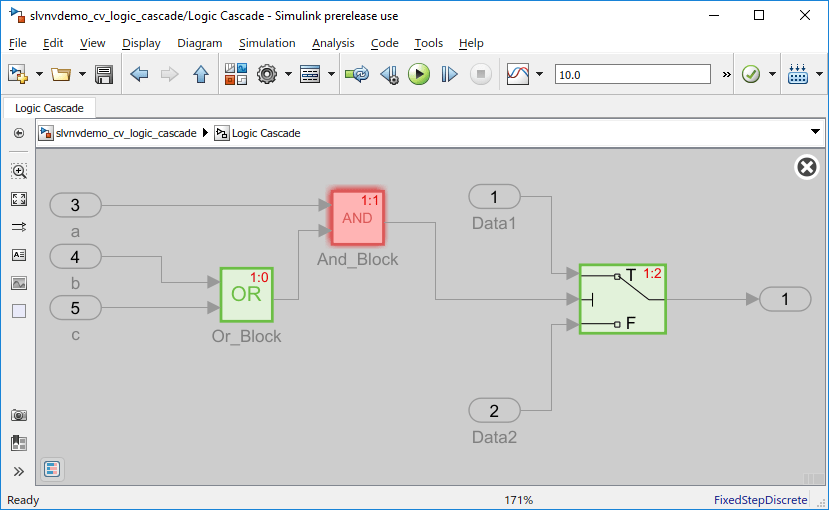

使用以下命令打开子系统“逻辑级联”,注意该子系统使用逻辑运算符块和开关实现完全相同的逻辑。

open_system (“slvnvdemo_cv_logic_cascade /逻辑级联”);

最后,打开信号生成器,注意布尔输入有三种组合A.,B,C.这些组合FFF,薄膜晶体管,TTT.

open_system (“slvnvdemo_cv_logic_cascade /信号生成器”);

关闭Signal Builder。

close_system (“slvnvdemo_cv_logic_cascade /信号生成器”, 0);

比较覆盖报告中的MCDC结果

模拟模型并生成覆盖率报告。

testObj=cvtest(“slvnvdemo\u cv\u逻辑\u级联”);testObj.settings.decision=1;testObj.settings.condition=1;testObj.settings.mcdc=1;covdata=cvsim(testObj);%模拟覆盖率cvhtml (“exampleReport.html”, covdata);%生成覆盖率报告

MCDC结果为MATLAB函数块

在生成的报告中,导航到MATLAB功能块的详细信息。

MCDC结果为如果给定指定的输入,MATLAB功能块中的语句与预期一样。

逻辑级联的MCDC结果

接下来检查逻辑级联的结果。回想一下,这种块的组合实现了与MATLAB功能块中的MATLAB代码相同的逻辑;因此,我们预计MCDC结果也会相同。

让我们先看看上游或_块.

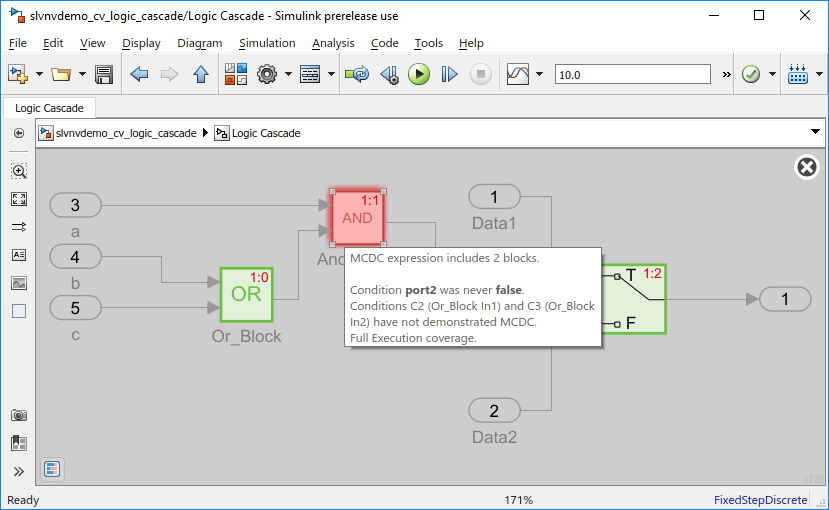

注意,这个块的MCDC摘要有一个带有文本的链接“请参阅和_块”,引用级联根的逻辑运算符。单击此链接可转到显示此块结果的报告部分。

位于级联根的逻辑运算符块(在本例中和_块)报告整个级联的MCDC结果。

级联MCDC分析的详细信息首先显示一个链接,说明级联中包括多少块。点击链接“包括2个区块”将打开模型并突出显示级联中包含的两个块(或_块和和_块).

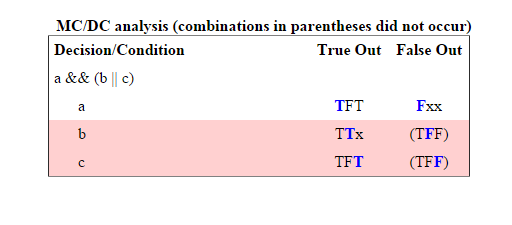

在本例中,报告的这一部分显示了由级联表示的布尔表达式C1 && (c2 | | c3),在那里C1,C2,C3是与级联的三个输入相对应的条件。对于每个条件,该表说明了相关的块及其输入(括号中显示)以及MCDC结果。这些结果表明,输入组合TTx,Fxx,薄膜晶体管都锻炼过了,但是TFF没有。这与给定信号生成器生成的输入的预期相符(TTT,FFF,薄膜晶体管).

此外,如预期的那样,该级联显示的布尔表达式和MCDC结果都与如果语句实现MATLAB函数块中的等价逻辑。

覆盖信息和模型着色

使用以下命令在模型上显示覆盖率结果:

cvmodelview(covdata);

正如覆盖率报告中所示,MCDC目标未记录为级联中的单个逻辑运算符块;相反,MCDC目标记录为级联中的块组合表示的布尔表达式,并在级联中的最终块上报告结果。模型的突出显示也反映了这一点。给定输入组合FFF,薄膜晶体管,TTT对于三个输入A.,B,C,或_块接收完全覆盖,因为所有区块的条件覆盖目标都已满足。但是,由于与此级联相关的MCDC目标尚未满足,And_block(级联中的最后一个块)以红色高亮显示。

悬停And_block为更多的信息。

工具提示正确地报告此块未完全覆盖,因为级联的某些MCDC目标未得到满足。

命令行

您还可以使用以下命令从MATLAB命令行检索逻辑块级联的MCDC结果mcdcinfo.同样,级联的MCDC目标将在级联的最后一块上找到。

[coverage_casc, description_casc] = McDcinfo (covdata,“级联slvnvdemo_cv_logic_cascade /逻辑/ And_Block”) description_casc.condition(1) description_casc.condition(2) description_casc.condition(3)

coverage_casc = 1 3 description_casc =结构体字段:文字:“C1 & & (C2 | | C3)的条件:[1 x3 struct] isFiltered: 0 filterRationale:“justifiedCoverage: 0 ans =结构体字段:文字:“C1 (And_Block In1)”实现:1 trueRslt:“TFT”falseRslt:的Fxx isFiltered: 0 isJustified: 0 filterRationale:“trueExecutedIn: [] falseExecutedIn:[] ans =结构体字段:文字:“C2 (Or_Block In1)”实现:0 trueRslt:“TTx”falseRslt:“(TFF)”isFiltered: 0 isJustified: 0 filterRationale:“trueExecutedIn: [] falseExecutedIn: [] ans =结构体字段:文字:“C3 (Or_Block In2)”实现:0 trueRslt:“TFT”falseRslt:“(TFF)”isFiltered: 0 isJustified: 0 filterRationale:" trueExecutedIn: [] falseExecutedIn: []

级联的其他模块不会显示MCDC目标。

[coverage_or, description_or] = McDcinfo (covdata,“slvnvdemo_cv_逻辑_级联/逻辑级联/或_块”)

覆盖率\u或=[]说明\u或=[]

MCDC布尔表达式的短路

在模型示例slvnvdemo_cv_逻辑_级联,设置覆盖率设置,以便将逻辑运算符块视为短路。

由于此设置,在分析逻辑运算符块的级联时,出于MCDC的目的,相应布尔表达式中的运算符被视为短路。如上所示的结果所示,这意味着MCDC能够识别逻辑运算符块内部和之间发生的短路。因此,逻辑运算符块级联的MCDC结果与如果语句,因为后者总是被视为短路。

块内短路

请注意,在上面的示例中,对于C2是TTx,表示当C1和C2都是真的,,C3是无关紧要的,因为短路内或_块.

多个区块的短路

此外,考虑假MCDC的客观结果C1,Fxx此结果说明MCDC分析如何识别模块间短路。因为和_块如果为false,则第二个输入短路。随后,出于MCDC的目的,该短路或_块(和它的两个输入)完全相同。MCDC对于逻辑块级联的短路行为是基于相应布尔表达式中操作的优先级发生的(无论模拟期间逻辑运算符块的执行顺序如何)。

Non-short-circuiting布尔表达式

在MCDC分析期间,如果使用MCDC的屏蔽定义,还可以将由逻辑运算符块级联表示的布尔表达式视为非短路。为此,设置参数CovLogicBlockShortCircuit到“关闭”并确保共模被设置为“掩蔽”. 实际上,这些是创建新模型时这些参数的默认设置。

注意,如果CovLogicBlockShortCircuit是“关闭”和共模被设置为“独一无二的事业”那么级联中的逻辑运算符块将被单独分析以实现MCDC,而级联所代表的布尔表达式的MCDC将不会被计算。

请注意,当本例中的级联未被视为短路时,某些MCDC目标不再由给定输入满足。

set_param (“slvnvdemo\u cv\u逻辑\u级联”,“CovLogicBlockShortCircuit”,“关闭”);设置参数(“slvnvdemo\u cv\u逻辑\u级联”,“COVCMODE”,“掩蔽”); covdata\u non\u sc=cvsim(“slvnvdemo\u cv\u逻辑\u级联”);%模拟逻辑块短路关闭时的覆盖范围cvhtml (“exampleReport_non_sc.html”,covdata_non_sc);%生成覆盖率报告