利用FPGA中断触发软件任务

本例展示了如何对硬件和软件之间划分的算法进行建模。硬件IP在FPGA结构中实现,并触发在嵌入式处理器中实现的软件任务。在SoC硬件上设计、模拟和实现完整的设计。

万博1manbetx支持的硬件平台:

Xilinx®Zynq®ZC706评估套件

Xilinx Zynq UltraScale™+ MPSoC ZCU102评估试剂盒

Xilinx Zynq UltraScale™+ RFSoC ZCU111评估工具包

刨花板™ Zynq-7000开发板

Altera®Cyclone®VSoC开发套件

AlteraArria®10SoC开发套件

介绍

多系统片上系统(SoC)应用程序需要硬件设备触发处理器上的异步任务。当实现跨越硬件和软件之间的低延迟控制循环时,此功能非常有用。它还可用于处理软件发出的紧急硬件请求。对于此类设计,硬件设备会引发中断请求st发送到中断控制器,表示数据已准备好由处理器上的软件任务执行操作。

设计任务

此示例包括FPGA中的两个硬件IP核。这些IP核异步生成中断信号。中断触发处理器上的两个独立任务,每个硬件IP核一个。处理器任务通过读取或写入寄存器访问硬件设备。

模型结构

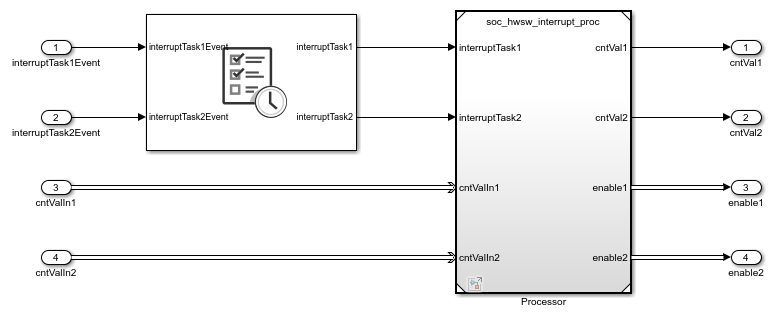

顶级模型sw_hw_interrupt_top.包括FPGA模型软硬件中断fpga和处理器模型软件硬件中断程序作为模型参考。顶部模型还包括中断通道和寄存器通道块,以将数据从FPGA传输到处理器。

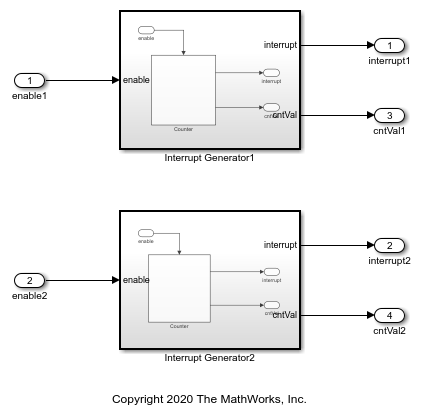

FPGA模型实现了两个IP核心,基于递增32位计数器值生成中断。当计数器值的第16位或第18位从0变为1.时,第一IP核心会生成中断。当计数器值的第14位或第16位从0变为1.时,第二IP内核在14或第16位发生时会产生中断生成中断时的计数器值被注册并使用寄存器通道块传送到处理器。处理器模型实现两个软件任务,一个用于每个IP核心,它读取以前由FPGA注册的计数器值。

模拟

模拟系统0.03秒,并在顶部模型上打开范围块,以便在处理器读取时可视化计数器值。

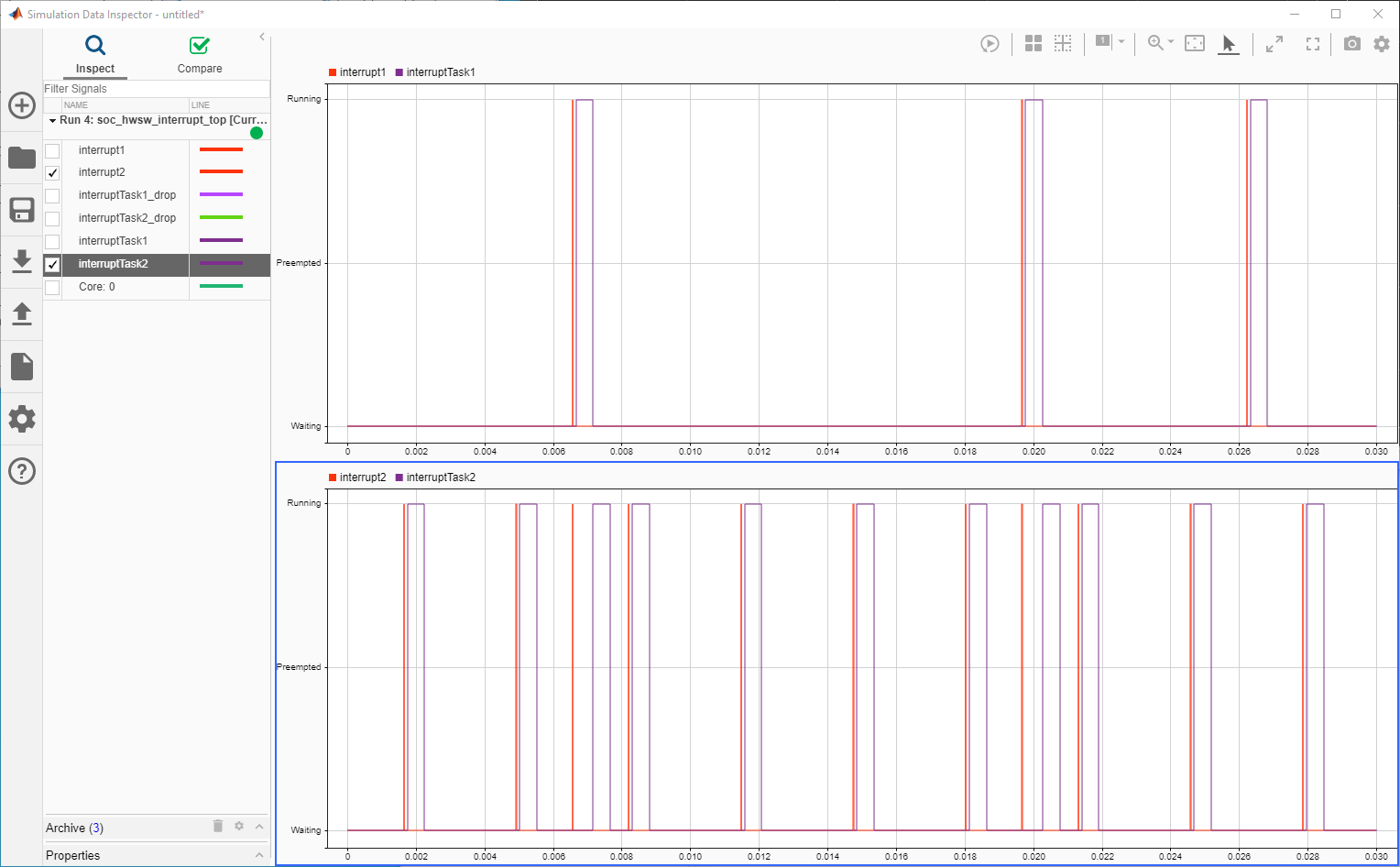

下一个,模拟选项卡,单击数据检查器查看由中断触发的各种事件的定时。在顶视图中添加中断1和InterruptAsk1信号,并在底部视图中添加Interrupt2和InterruptTask2信号。仿真图表明,每次触发中断时,都会执行相应的任务。在0.01802秒时,中断2被提升,需要100微秒来处理中断通道块,并触发相应的InterrukTask2,占用500微秒运行。

在时间0.01966秒时,中断1和中断2同时被触发,处理器根据它们的相对优先级为它们提供服务。由于中断1首先连接在中断通道块的输入端口,因此其优先级高于中断2。由于interrupt1的优先级较高,interruptTask2等待执行,而interruptTask1仍在执行。

实现并运行硬件

本节要求这些s manbetx 845产品:

HDL编码器™

嵌入式译码器

适用于Xilinx设备的S万博1manbetxoC块集支持包,或适用于Intel设备的SoC块集支持包

有关支持包的更多信息,请参阅万博1manbetxSoC BlockSet支万博1manbetx持硬件。

要在受支持的SoC板上实现该模型,请使用万博1manbetxSoC Builder.工具。默认情况下,模型将实现刨花板因为它配置了该板。打开SoC Builder.在ToolStrip中单击,“配置,构建和部署”按钮,然后按照下列步骤操作:

选择构建模型上设置屏幕上。点击下一个。

点击下一个上点评任务地图屏幕上。

在查看内存映射屏幕,点击查看/编辑内存映射查看内存映射。点击下一个。

指定项目文件夹选择项目文件夹屏幕上。点击下一个。

选择构建、加载外部模式上选择构建操作屏幕上。点击下一个。

在验证模型屏幕,点击证实要检查要实现的模型的兼容性,请单击下一个。

在构建模型屏幕,点击建筑开始构建模型。当FPGA合成开始时,会打开一个外壳。单击下一个。

点击测试连接上连接硬件屏幕以测试主计算机与SOC板的连接。点击下一个去…运行应用程序屏幕上。

FPGA合成可能需要超过30分钟才能完成。要节省时间,您可能希望按照以下步骤使用提供的预生成的比特流:

关闭外壳以终止合成。

通过运行此操作将Pregenerated比特流复制到项目文件夹中

复制文件下面的命令点击加载和运行加载预生的比特流并在SOC板上运行模型

copyfile(完整文件(matlabshared.supp万博1manbetxortpkg.getSupportPackageRoot,“工具箱”那'soc'那......'万博1manbetx支持包装'那'xilinxsoc'那“xilinxsocexamples”那'比特流'那......'soc_hwsw_interrupt_top-zedboard.bit'),'./soc_prj');

加载比特流后,运行生成的软件模型soc_hwsw_interrupt_sw.在外部模式下。从“模型”工具栏中,打开数据检查器并在顶视图中添加InterruptTask1和InterruptTask2进入底视图。观察到每次触发中断时,执行相应的任务。

其他委员会的执行情况:要在除ZedBoard以外的受支持板上实现模型,请首先将模万博1manbetx型配置为受支持板,然后按如下所示设置示例参数。

在这一点硬件选项卡,单击硬件设置打开“配置参数”窗口。

在这一点硬件实现选项卡,从而从中选择您的董事会硬件板在顶部和处理器模型上。

在这一点目标硬件资源>FPGA设计(顶级)选项卡启用将MATLAB作为基于主机的交互的AXI主IP和集合IP核心时钟频率(MHz)到10 MHz。

接下来,点击配置、构建和部署在要打开的工具条上SoC Builder.并按照前面针对ZedBoard所述的步骤进行操作。修改复制文件命令匹配与您的电路板相对应的比特流。如果是AlteraArria®10SoC开发套件和AlteraCyclone®VSoC开发套件在下面使用复制文件指令对应于您的电路板。在AlteraArria®10SoC开发套件的情况下,复制'.periph.rbf'和'.core.rbf'文件。

copyfile(完整文件(matlabshared.supp万博1manbetxortpkg.getSupportPackageRoot,“工具箱”那'soc'那......'万博1manbetx支持包装'那“国际电信组织”那“互联网示例”那'比特流'那......‘soc_hwsw_中断_top-c5soc.rbf’),'./soc_prj');

以下是可用的预生成位流文件:

‘soc_hwsw_中断_top-zc706.位’

'soc_hwsw_interrupt_top-zedboard.bit'

‘soc_hwsw_中断_top-zcu102.位’

'soc_hwsw_interrupt_top-xilinxzynqultrascale_rfsoczcu11.evalizationkit.bit'

‘soc_hwsw_中断_top-c5soc.rbf’

‘soc_hwsw_中断_top-a10soc.periph.rbf’

'soc_hwsw_interrupt_top-a10soc.core.rbf'

总之,此示例显示了如何从处理器中的FPGA触发动作中断。您使用SoC块集建模了该行为,并通过在SoC设备上实现它所需的工作流程。