基于AD9361/AD9364模拟器件的软硬件协同设计QPSK收发

这个例子展示了如何在Zynq®无线电平台上实现无线通信算法,这些算法被划分在ARM®处理系统和FPGA可编程逻辑上。针对该系统设计了基于qpsk的通信系统。

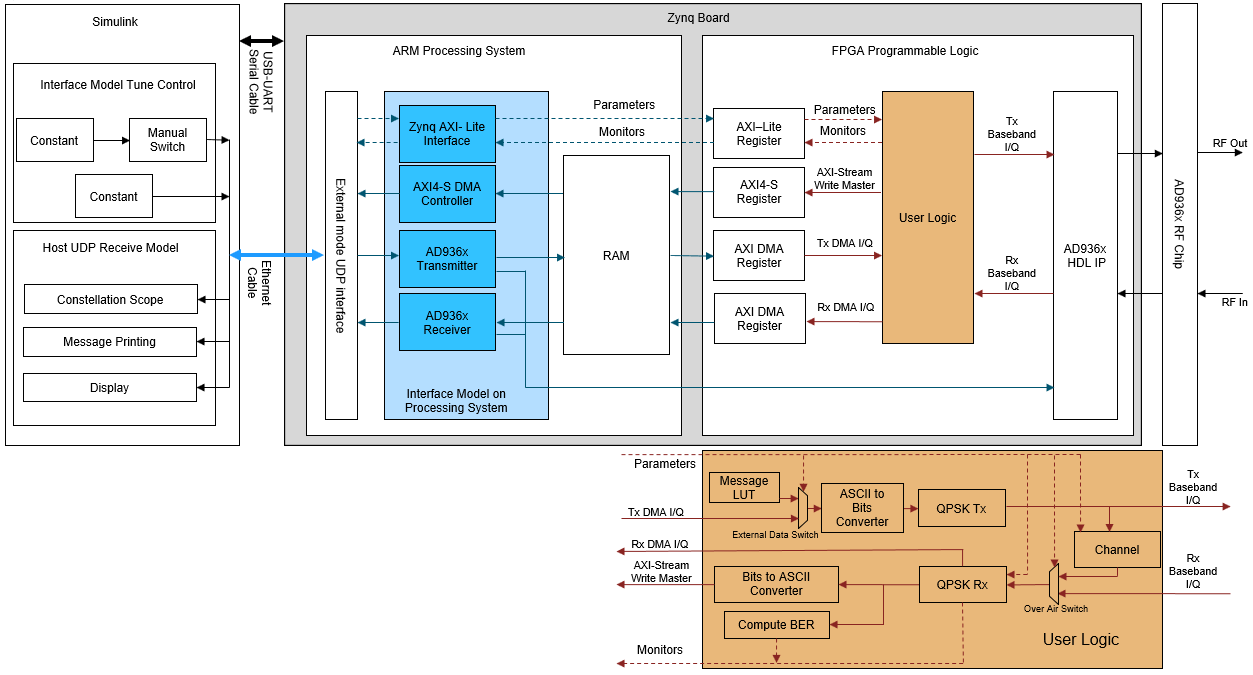

下面的框图描述了系统的软硬件划分和实现的用户逻辑。

设置

要使用HW/SW协同设计工作流,您必须安装和配置额外的支持包和第三方工具。万博1manbetx有关更多信息,请参见硬件-软件协同设计的安装.

硬件生成模型

您需要一个硬件生成模型来实现运行在可编程逻辑(PL)上的任何设计。在本例中,采用了hdl优化的QPSK发射机和接收机HDL QPSK发射机和接收机用实例实现了硬件生成模型。为硬件生成模型生成HDL代码,并使用HDL Workflow Advisor生成软件接口模型模板。使用软件接口模型模板,开发一个运行在处理系统(PS)上的接口模型。

硬件软件分区

一般来说,FPGA的可编程逻辑用于高速率的信号处理,而ARM用于较慢速率的控制功能。FPGA可编程逻辑中的用户逻辑实现了高速率处理模块、ASCII码到比特转换器、QPSK发射机设计、信道设计、QPSK接收机设计、比特码到ASCII转换器和误码率计算模块。一些控制参数和监测信号被添加到FPGA IP核,以实时调整设计,并通过处理系统使用从Simulink®访问的axis - lite寄存器查看FPGA信号的状态。万博1manbetxARM处理系统从FPGA中提取状态信号信息,并在主机上显示。

在硬件平台上实现FPGA IP核,请使用IP核生成工作流,具体要求如下。

HDL_QPSK子系统是工作流的待测设备。DUT子系统端口不支持复杂数据,因此在子系统边界处建模实信号和虚信万博1manbetx号。使用单独的数据和有效信号建模数据输入和输出端口。DUT子系统的输入和输出时钟速率必须相等。

AXI4-lite端口:externalDataActive输入端口将消息从内部LUT (Hello World消息)切换到外部消息(Zynq无线电HW/SW Co-design QPSK)。的overAir输入端口通过FPGA内部的通道将数据流通过空气切换到QPSK Tx和QPSK Rx之间的环回。的插入首席财务官而且插入CPOinput ports设置要引入到通道波形中的载波频率偏移(CFO)和载波相位偏移(CPO)的值。的rstCS输入端口复位QPSK接收器中的载波同步器。的bitErrors而且bitReceivedports流错误的数量和从QPSK接收器接收到的比特数。的numOfFramesSynced而且estimatedCoarseCFOports流输出同步帧数和估计的粗CFO。

生成IP核

如果硬件子系统的模拟行为符合预期,您可以开始生成HDL IP Core的过程,将其与SDR参考设计集成,并生成在ARM上运行的软件。

在为目标定位做准备时,必须通过调用设置Xilinx®工具链hdlsetuptoolpath.例如:

> > hdlsetuptoolpath (“ToolName”,“Xilinx Vivado”,“路径”,“C: \ Xilinx \ Vivado \ 2019.1 \ bin \ vivado.bat ');

要生成HDL IP核,右键单击HDL_QPSK子系统和选择HDL代码> HDL工作流顾问.

扩大1.设定目标并点击1.1.设置目标设备和合成工具.在右侧窗格中,设置目标工作流程来

IP核生成而且目标平台来ZC706和FMCOMMS2/3/4.

点击1.2.设定目标参考设计.在右侧窗格中,设置参考设计*

接收和发送路径.对于本例,使用参考设计参数窗格。

点击1.3.设置目标接口.在右侧窗格中目标平台接口表窗格将DUT信号映射到参考设计中可用的接口信号。因为本例使用单个通道,所以配置通道1连接和AXI寄存器接口,如图所示。

点击1.4.设定目标频率.在右侧窗格中,设置目标频率(MHz)来

61.44.对于本例,使用Set . properties中的默认设置目标频率窗格。

点击2.为HDL代码生成准备模型.在右侧窗格中,单击运行所有.该应用程序通过执行设计检查来为HDL代码生成准备模型。

点击3.HDL代码生成.在右侧窗格中,单击运行所有.该应用程序为IP核生成HDL代码。

接下来,继续使用HDL Workflow Advisor生成软件接口模型和块库。

生成软件接口模型和块库

扩大4.嵌入式系统集成.该步骤将新生成的IP核项目集成到Zynq SDR参考设计中,生成相应的比特流,并将比特流加载到板上。

点击4.1.创建项目.在右侧窗格中,单击运行此任务.该应用程序为嵌入式系统工具创建一个项目。

点击4.2.生成软件接口模型.在右侧窗格中,单击运行此任务.该应用程序生成一个软件接口库和一个软件接口模型模板。

类生成的AXI Interface块HDL_QPSK子系统。此块只公开axis -lite控制端口,而不公开数据端口。数据端口出现在发射器和接收器块上,对应于中选择的硬件1.1.设置目标设备和合成工具.发射端和接收端的数据端口是FPGA用户逻辑与ARM处理器之间的流数据接口。

在下游模型中使用库块时,必须为应用程序正确配置参数。考虑到任何更新HDL_QPSK子系统在运行时从下游模型中的库块自动传播4.2.生成软件接口模型一次。

软件接口模型模板

将软件接口模型作为针对Zynq的软件开发的起点:外部模式模拟、处理器在环或完全部署。运行步骤4.2生成软件接口模型覆盖软件接口模型。因此,建议用唯一的名称保存模型并开发您的软件算法。本例提供了一个软件接口模型,展示了如何构建该模型。

生成和加载比特流

HDL Workflow Advisor的最后一步是为PL生成一个比特流,并将比特流下载到电路板上。

点击4.3.构建FPGA位流.在右侧窗格中,单击运行此任务.应用程序为PL生成一个比特流。你可以通过选择在外部shell中执行这一步运行构建过程外部。此选择允许您在构建FPGA映像时继续使用MATLAB®。在基本项目检查完成后,应用程序用绿色复选标记标记此检查。但是,必须等到外部shell显示成功的位流构建后才能继续下一步。

点击4.4.程序目标设备.在右侧窗格中,单击运行此任务.应用程序将比特流下载到设备上。在继续此步骤之前,调用zynq函数,以确保MATLAB具有正确的无线电硬件物理IP地址:

>> devzynq = zynq(“linux”,“192.168.3.2”,“根”,“根”,“/ tmp”);

缺省情况下,无线硬件的物理IP地址为192.168.3.2.如果在硬件设置过程中更改了无线电硬件IP地址,则必须提供该地址。

或者,如果您想在HDL Workflow Advisor之外加载比特流,可以使用sdrdev对象,并使用downloadImage函数。中所创建的对象类型取决于目标平台设置1.1.设置目标设备和合成工具窗格。

如果选择的无线电平台为Adi rf som,ZC706和FMCOMMS2/3/4,或ZCU102和FMCOMMS2/3/4,创建AD936x无线电对象。

>> radio = sdrdev(“AD936x”);

如果在步骤1.1中选择了ZC706和FMCOMMS5无线电设备,创建FMCOMMS5无线电对象。

>> radio = sdrdev(“FMCOMMS5”);

使用与所选无线电设备接口的无线电对象下载比特流。

> > downloadImage(广播,“FPGAImage”,...“hdl_prj \ vivado_ip_prj \ vivado_prj.runs \ impl_1 \ system_top.bit ')生成的比特流的路径

构建软件接口模型

本例中提供了一个软件接口模型,展示了如何构造生成的模型。您可以在监视和调优模式或完全部署模式下运行此接口模型。

注意,在软件接口模型中,AD936x发射器块处理帧到样本序列化。

建立在ARM处理器上运行的软件模型

方法中的指导原则设置应用程序模型硬件-软件协同设计工作流,部分软件接口模型配置.配置模型以使用目标板Xilinx Zynq-7000基于IIO无线电ADI RF SOM, ZedBoard和FMCOMMS2/3/4,以及ZC706和FMCOMMS2/3/4/5。对于ZCU102和FMCOMMS2/3/4,双击所选硬件板目标块更改配置以使用目标板作为Xilinx Zynq UltraScale+ MPSoC IIO无线电.目标。为了保证ARM处理器的高效使用,输入的大小AD936x发射机通过多次连接外部消息,每个字符重复16次,将Block设置为近10000。由于消息速率是基带采样率的1/16,因此将每个消息字符重复16次可以使消息保持在基带采样率。

在Zynq板上运行软件和硬件

您可以从Simulink模型中控制设置万博1manbetx监视和调优模式。拨动连接到externalDataActive设计运行后,在FPGA存储的LUT消息和基于arm的外部消息之间切换源数据。

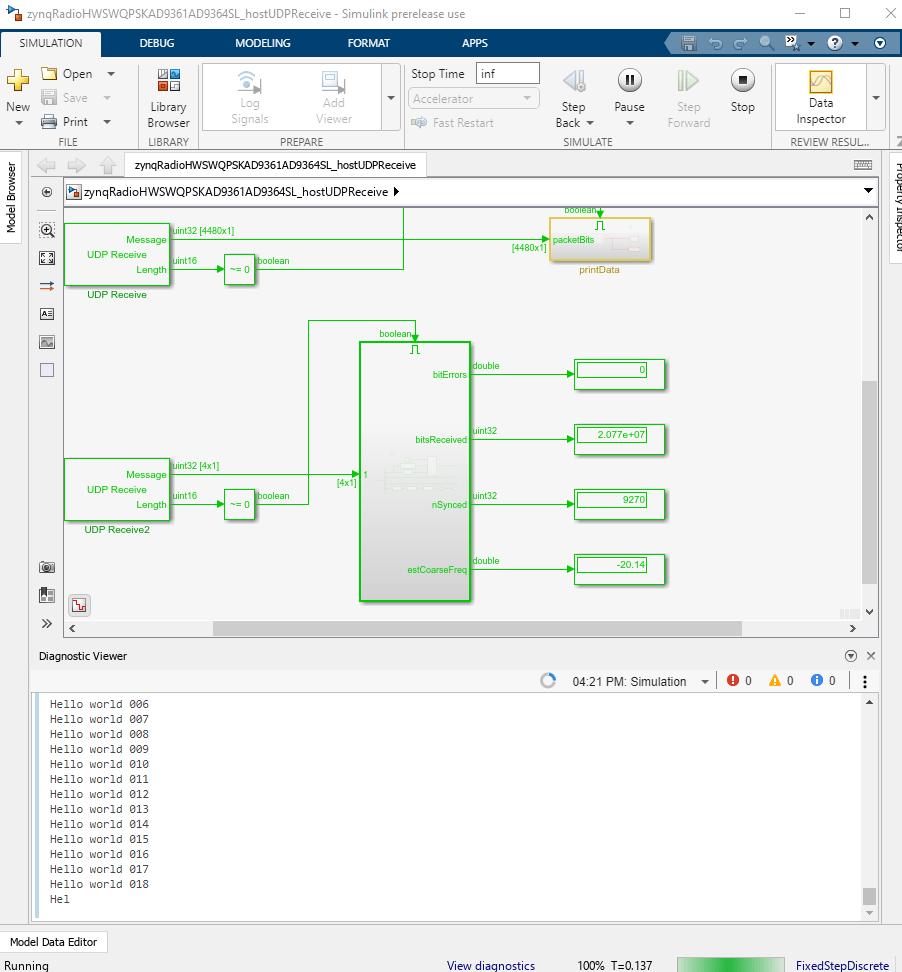

一旦接收方解码消息,ARM处理系统使用软件接口模型中的UDP发送块通过以太网链路将结果发送回主机。UDP发送块使用主机的默认IP地址“192.168.3.1”进行配置。如果在硬件安装过程中更改了IP地址,则必须提供该地址。提供了一个简单的主机UDP接收模型,可用于接收解码后的数据并在诊断查看器中显示结果。

您还可以完全部署设计以在板上运行,与Simulink断开连接。万博1manbetx2 .在“Si万博1manbetxmulink”工具栏中单击构建、部署和启动.在此模式下,不能调优参数。

结果

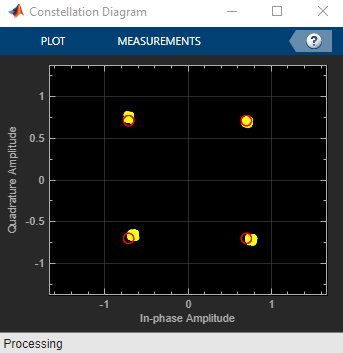

下图显示了当波形在空中传输时解码的消息和星座。诊断查看器显示解码后的消息。

星座图

主机UDP模型-内部LUT消息:

主机UDP模型-外部消息: