串行链路设计

设计PCIe、USB、以太网等高速串行链路

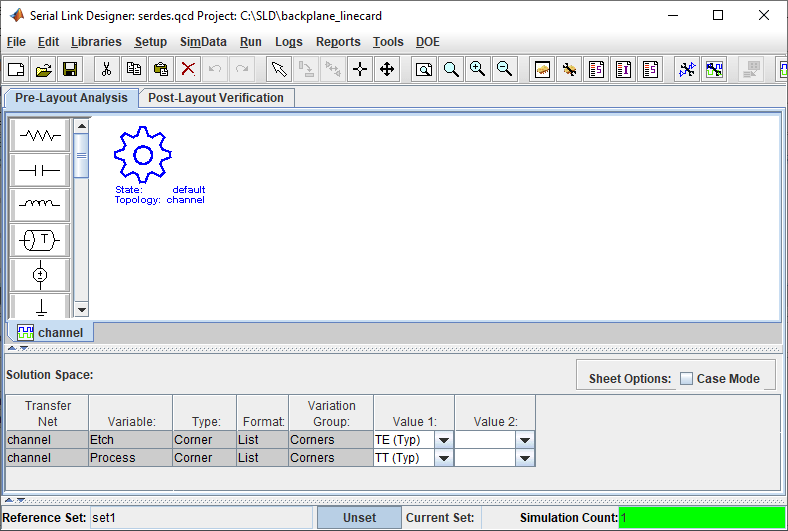

的串行链路设计器App为千兆串行链路提供了专用的系统级设计和分析环境。以图形方式捕获串行链路设计,并试验不同的物理布局和均衡策略,以预测设计替代方案如何影响链路的操作裕度和误码率(BER)。使用网络特性来模拟非均衡模拟网络的行为。这使得快速评估模拟信道设计不同的权衡。使用SerDes均衡技术和通过统计和时域分析获得的时钟恢复模型预测链路的端到端行为。使用串扰分析确定攻击信号对信道整体误码率的影响。

使用串行链路设计器应用程序配置高速串行链路。设置仿真参数,指定拐角条件,并定义刺激模式。设置预布局分析,以运行SPICE,网络表征,统计和时域模拟,以分析您的自定义串行链路。控件查看和解释结果信号完整性查看器如果您拥有RF PCB工具箱™的许可证,您还可以设置和分析串行链路设计的布局后PCB数据库。您可以修改堆叠和堆叠模型和自定义通孔,并查看更改如何影响您的设计。

主题

串行链路设计基础

- 串行链路设计中的分析流程

使用迭代和渐进的分析流程从大的解决方案空间中找到最优解决方案。 - 时钟模式

了解AMI模型中不同的时钟模式。 - PAMn功能

设计和模拟系统,并使用PAMn信号测试AMI模型。 - 链接设计器应用中的元素

元素使用的元素列表串行链路设计器而且并行连杆设计器应用程序。 - 信号完整性查看器中可用的操作列表

刷新,缩放,使用标记和阈值,并修改信号完整性查看器应用程序中的显示。 - 在信号完整性工具箱中运行并行模拟

通过使用并行计算工具箱™并行运行模拟,可以减少运行一整套模拟所需的时间。

配置串口链路工程

- 串行链路设计中的仿真参数

设置参数控制SPICE仿真和统计、时域和波形分析。 - 在串行链路设计中指定拐角条件

在串行链路工程中指定工艺角和蚀刻角进行模拟。 - 串行链路设计中的刺激模式

定义序列链接项目中时域分析的刺激模式。 - 设计串行链路时的抖动和噪声模型

添加TX时钟抖动、RX时钟抖动、RX时钟恢复抖动和噪声。

Pre-Layout分析

- 串行链路的预布局分析

学习预布局分析的基础知识。 - 为预布局分析定制串行链路项目

编辑传输线模型、指示器、s参数和IBIS文件,以自定义预布局分析。 - 串行链路预布局分析结果

查看、解释和调试预布局分析结果。 - 渠道营运利润率(COM)

COM在串行链路设计中的定义和应用。

布局后验证(需要射频PCB工具箱)

- 串行链路布局后验证

验证PCB设计数据库的系统级SI和时间裕度。 - 串行链路工程中的堆叠与抽取控制

编辑堆叠和控制堆叠模型。 - 串行链路工程中的通槽和堆叠管理

使用Stackup编辑器和PadStack编辑器管理通孔和堆叠。 - 从后布局到前布局提取

从提取的PCB数据创建拓扑。