深度学习HDL工具箱™는딥러닝신경망을FPGA와SoC에서프로토타이핑하고구현하는함수와툴을제공합니다。다양한딥러닝신경망을지원되는Xilinx®와英特尔®의FPGA및SoC기기에서구동할수있도록사전구성된비트스트림을제공합니다。프로파일링및추정툴을통해설계와성능,리소스활용도를절충하여딥러닝신경망을사용자지정할수있습니다。

深度学习HDL工具箱를통해딥러닝신경망의하드웨어구현을사용자지정하고,高密度脂蛋白编码器™및仿真软件万博1manbetx®와함께사용해이식성과합성가능성이좋은Verilog®및硬件描述语言(VHDL)®코드를생성하여fpga에배포할수있습니다。

시작하기:

프로그램가능딥러닝프로세서

툴박스에는스케줄링로직으로제어되는일반컨벌루션계층및완전연결계층을갖는딥러닝프로세서가포함되어있습니다。이딥러닝프로세서는深度学习工具箱™를사용하여개발된신경망의fpga기반추론을수행할수있습니다。고대역폭메모리터페이스는계층및가중치데이터의메모리전송에속도를더합니다。

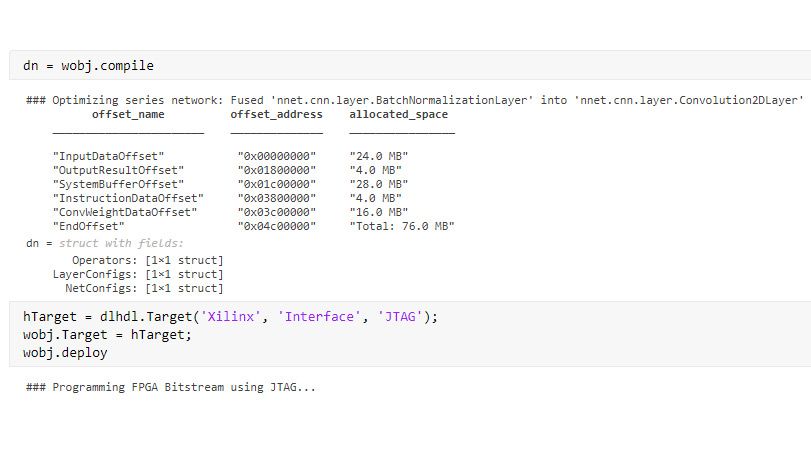

컴파일및배포

딥러닝신경망을딥러닝프로세서로실행할일련의지침으로컴파일할수있습니다。이를FPGA에배포하고예측을실행하면서실제기기상에서의성능메트릭을수집할수있습니다。

사전구성된비트스트림시작하기

널리사용되는FPGA개발키트에사용할수있는비트스트림으로FPGA프로그래밍없이신경망을프로토타이핑할수있습니다。

배포할신경망만들기

객체탐지나분류등의작업에사용할딥러닝신경망을深度学习工具箱를사용해설계,훈련,분석하여시작할수있습니다。또한기타프레임워크에서훈련된신경망또는계층을가져와서시작할수도있습니다。

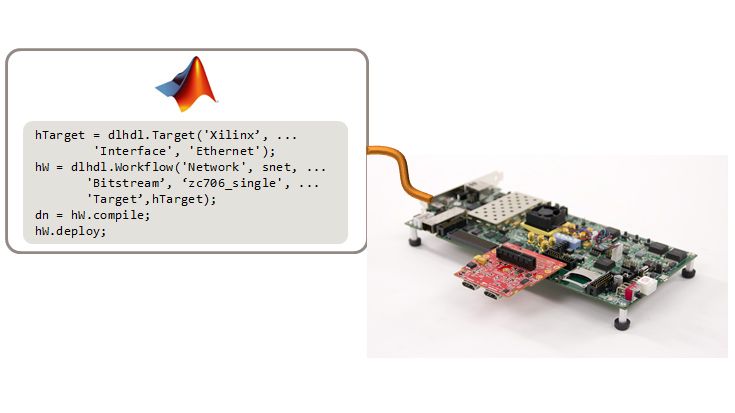

Fpga에신경망배포

훈련된신경망이있다면部署명령을사용하여이더넷또는JTAG인터페이스및딥러닝프로세서로FPGA를프로그래밍할수있습니다。그후에는fpga를다시프로그래밍하지않고도编译명령을사용하여훈련된신경망에대한일련의지침을생성할수있습니다。

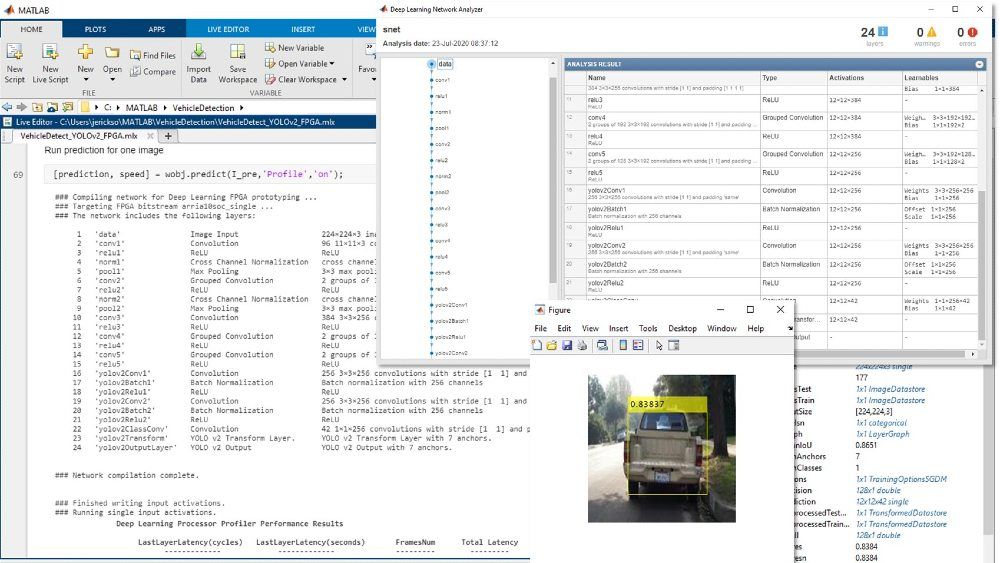

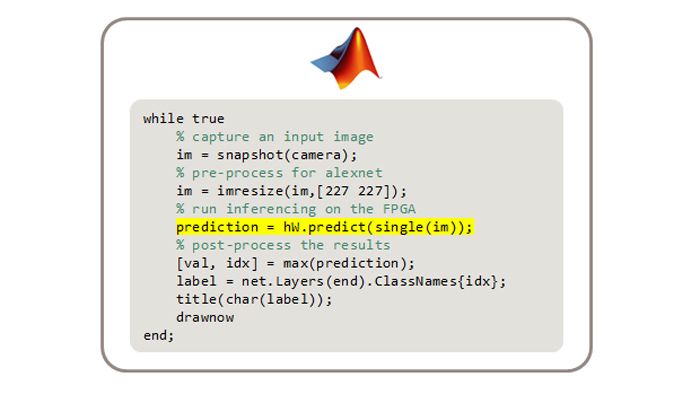

Matlab응용프로그램의일부로서fpga기반추론실행하기

테스트벤치전,처리및후처리알고리즘,FPGA기반딥러닝추론등의전체응용프로그램을MATLAB®에서실행할수있습니다。단일matlab명령预测를통해FPGA에서추론을수행하고결과를MATLAB작업공간으로반환할수있습니다。

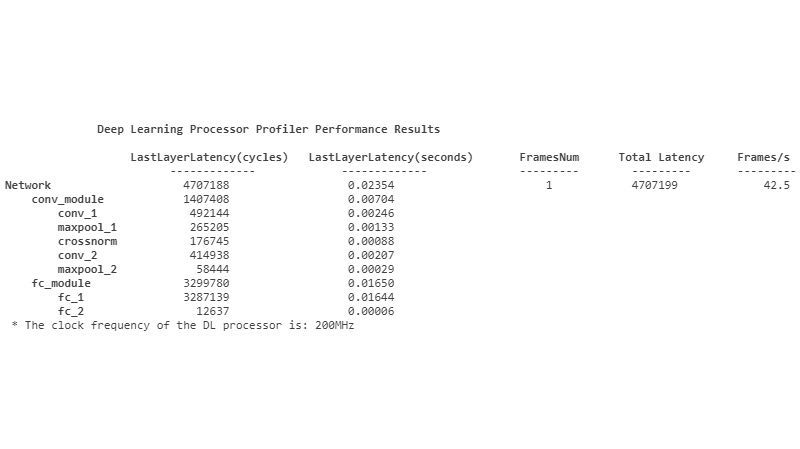

Fpga추론프로파일링하기

FPGA에서예측실행시의계층수준대기시간을측정하여성능의병목지점을찾을수있습니다。

신경망설계조정

深度学习工具箱로프로파일메트릭을사용하여신경망구성을조정할수있습니다。예를들면심층신경망디자이너를사용하여계층을추가하거나제거하거나새연결을만들수있습니다。

딥러닝양자화

딥러닝신경망을고정소수점@ @현식으로양자화하여리소스활용도를낮출수있습니다。模型量化图书馆지원패키지를사용하여정확도와리소스활용도간의상충관계를분석할수있습니다。

사용자지정딥러닝프로세서구성

병렬스레드의수나최대계층크기처럼딥러닝프로세서구현에필요한하드웨어아키텍처옵션을지정할수있습니다。

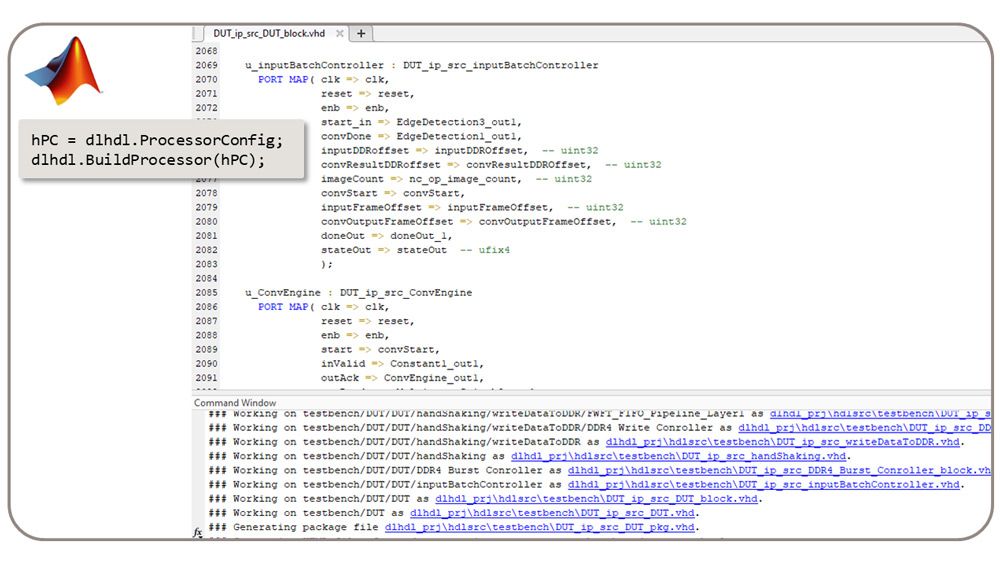

합성가능RTL생성

다양한구현워크플로와기기에사용할목적으로HDL编码器를사용하여딥러닝프로세서에서합성가능한RTL을생성할수있습니다。프로토타입및프로덕션배포에동일한딥러닝프로세서를재사용할수있습니다。

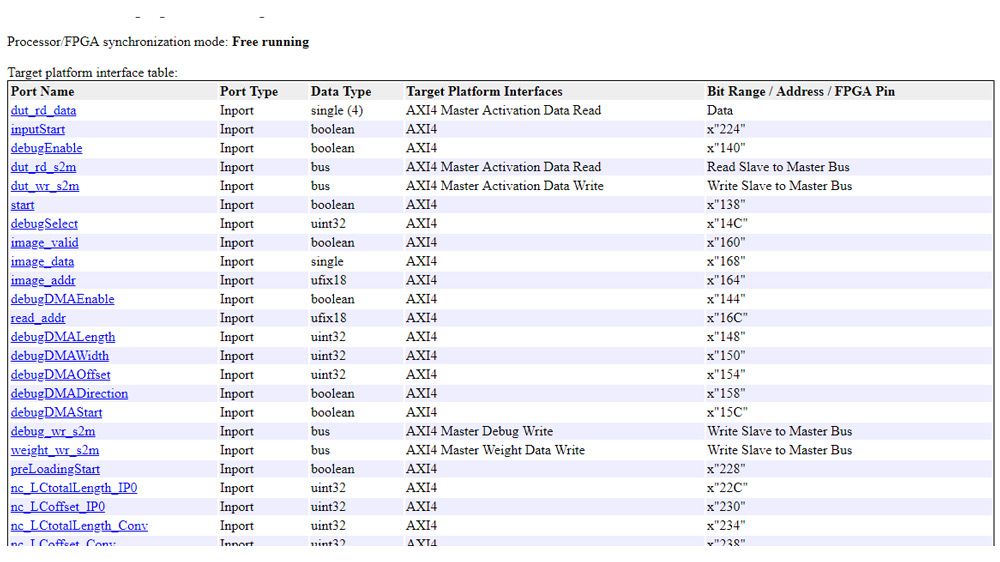

통합을위한IP地址코어생성

高密度脂蛋白编码器는딥러닝프로세서에서RTL을생성할때SoC기준설계로의통합을위한표준AXI인터페이스를갖춘IP코어도생성합니다。