SoC Blockset

设计、评估和实现SoC硬件和软件体系结构

SoC块集™提供Simulink万博1manbetx®模块和可视化工具,用于在一个芯片(SoC)上为asic、FPGAs和系统建模、仿真和分析硬件和软件体系结构。您可以使用内存模型、总线模型和I/O模型构建系统体系结构,并使用算法模拟体系结构。

SoC块集允许您使用生成的测试流量或真实的I/O数据模拟内存、内部和外部连接,以及调度和操作系统效果。您可以快速探索不同的系统体系结构,评估硬件和软件分区的接口复杂性,并评估软件性能和硬件利用率。

SoC块集导出Xilinx的参考设计®和英特尔®FPGA设备和SoC平台,包括Zynq®-7000, Ultrascale+™,英特尔SoC fpga。这些参考设计可以与Xilinx和Intel设计工具一起使用。

开始:

SoC模型模板

使用逐步的方法从头开始构建完整的SoC应用程序模型,或者从用于软硬件协同处理的预定义模板(包括用于视觉和通信应用程序的模板)开始。

使用记录的I/O数据进行模拟

记录硬件外设源,如RF信号或HDMI数据,然后在模拟或硬件测试中作为源回放记录。

DDR内存性能

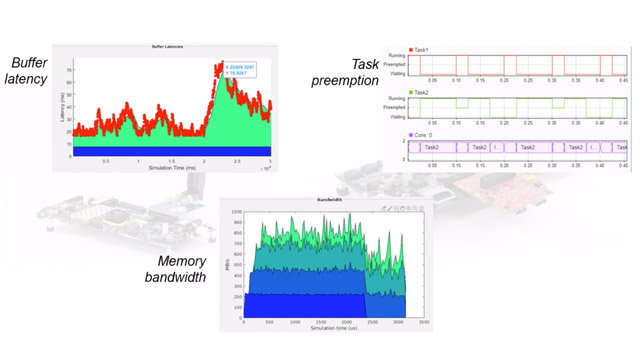

分析系统设计的内存带宽。在部署到SoC设备之前,可视化仿真结果和带宽指标。

设备上内存性能监视和任务执行概要

测量SoC设备上的内存性能和任务执行,然后可视化和分析这些测量,以调整SoC模型以满足您的系统性能需求。与来自MATLAB或Simulink测试平台的SoC设备进行实时交互。万博1manbetx

出口参考设计

为可编程逻辑生成参考设计。参考设计是通过数据和控制路径配置的IP核心网络,这些数据和控制路径可以连接到外部存储器和软件应用程序。SoC块集连接到Xilinx和Intel设计工具来产生比特流,然后对FPGA和SoC板进行编程。

生成算法IP

生成目标优化算法IP与高密度脂蛋白编码器™。将生成的IP集成到SoC块集导出的参考设计中,并使用FPGA供应商工具生成完整的比特流。

生成应用软件

使用嵌入式编码器,生成软件应用程序代码并将其部署到SoC硬件板上。SoC块集自动创建任务;将它们分配给线程;并将中断、消息和系统事件链接到生成的代码。

万博1manbetx支持硬件板

在Xilinx或Intel FPGAs或soc支持的硬件套件上实现硬件/软件应用程序。万博1manbetx目标板使用硬件支持包或构建自定义板的支持。万博1manbetx

Testbench任务块

为您的外部任务与应用程序争夺资源的效果建模

代理任务块

在没有显式任务实现的情况下,为应用程序中的任务效果建模

硬件内存诊断

查看额外的延迟和FPGA执行中的数据溢出信息

内核分析器

使用LTTng监视和记录任务的执行时间

I/O数据源块

从记录的数据文件中读取数据,时间间隔与记录在硬件板上的时间间隔相同

自定义董事会支持万博1manbetx

看到发布说明有关这些功能和相应功能的详细信息。