从一个处理器的FPGA设计Datapath公司SoC Blockset:建模与仿真

从系列:设计一个Datapath公司的FPGA与SoC Blockset处理器

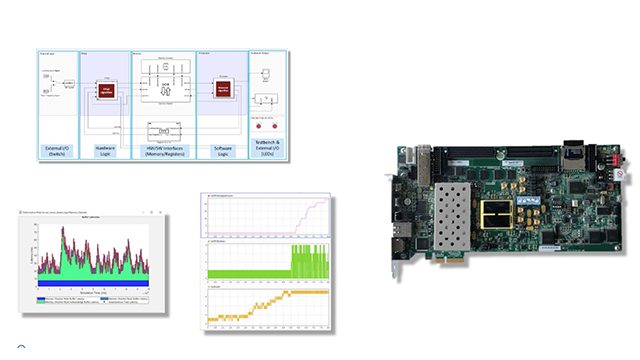

这个视频是一个系列的一部分,展示了一个系统性的方法来设计和FPGA的硬件逻辑之间的datapath公司嵌入式处理器使用SoC Blockset™。应用程序经常分区之间的硬件逻辑,嵌入式处理器芯片系统(SoC)设备来满足吞吐量、延迟和处理要求。

学会设计和模拟整个应用程序由FPGA和处理器算法以及内存接口。您将看到如何使用共享外部内存块从SoC Blockset模型,以及如何使用SoC Blockset测量不同形式的延迟,并从内存缓冲区数据丢失。

通过执行这些分析使用模拟,你有更好的可见性比工作时只有硬件设计。你可以发现吞吐量损失等问题,延迟和减少样本在实现硬件。

在这个视频中,我们将展示如何使用SoC Blockset模型和模拟硬件的影响在设计数据路径从一个处理器的FPGA。

通过模拟硬件的影响,而开发一个应用程序中,您可以评估整体性能没有得到应用程序加载的所有额外的努力开发板。还与模拟,你可以有更大的可视性应用程序比是可能的开发板,这样你就可以更快地识别问题和测试潜在的解决方案。

这是我们设计应用程序的初始模型。需要从外部源正弦流数据,把它作为一个低收入或高频信号,和低或高频率检测器光照亮。

我们将测试它通过拨动开关选择低收入和高频信号。对于测试的目的,我们将生成在FPGA测试信号。FPGA过滤器输入流,然后将数据传递到缓冲区。初始模型使用一个简单的理想的缓冲,这是足够好的检查算法。处理器运行在一帧的数据,检测信号,并打开相应的探测器的光。

我们可以看到模型运行。在模拟我们可以在低收入和高频测试信号之间切换,我们看到探测器led点亮。仿真证明了算法,但是现在我们要把硬件缓冲在DDR内存的影响我们将在硬件配置它。SoC Blockset包括块和模板,帮助我们。

考虑我们的应用程序的这个图。FPGA的测试信号采样的速度100千赫。处理器运行在一帧的数据每10毫秒。因为从FPGA异步传输的数据处理器,我们插入一个FIFO FPGA内存以及DDR内存。这里显示的虚线代表背压。这是内存缓冲区填满,可能需要更多的数据保持在FPGA的FIFO缓冲区刷新之前。

这里有两个需求的设计必须满足:

- 最大允许延迟是100毫秒

- 我们不能减少任何超过1 10000年样本

当我们试图满足这些需求,我们将专注于两个参数:帧大小和缓冲区的数量。

我们用从SoC Blockset块模型更准确地设计的架构。

- 这个内存通道数据传输通过DDR共享内存块模型。在这个模型中,记忆的通道模型实现AXI4-Stream协议从FPGA通过DMA处理器。

- 内存控制器断定和赠款访问内存块。

- 注册通道模型的通信处理器的FPGA,我们看到,FPGA驱动发光二极管通过其输出插脚。

首先,我们使用一个框架的大小800个样本,每个样本消耗4个字节。我们还指定的内存区域将包括11个缓冲区。我们设置的参数记忆通道块和运行模拟。

在仿真中,我们可以切换输入信号之间的低收入和高频信号。我们可以查看dataout信号来自处理器和看到的频率变化,我们可以看到相应的指示灯变化。我们运行仿真100秒时间,,这个模型已经运行完成。

我们打开通道的内存块,它是仪器测量延迟逐帧。如下所示,几秒钟到模拟,100毫秒的延迟到达值范围。最大允许延迟时间是100毫秒,所以这个设计不是太遥远的延时要求。因为我们正在接近要求,让我们继续。

另一个要求是,样品不超过1 10000年可能会下降。随着SoC Blockset,模型检测我们可以确定样品是否被删除。从上面的图表,我们可以看到缓冲区使用开始增加约3秒进入模拟,并增加到约5.5秒。中间的图块使用FIFO,底部一块样品的数量已经下降。

在5.8秒左右,FIFO开始稳步下降样本。100秒,年底已下降了近900个样本,我们可以看到,每10秒期间,大约100个样本下降。这是非常正确的要求限制的10000。因为这个规格的设计也不是会议很好,让我们试试改变内存配置。

我们将增加框架的大小从800年到1000年样本和减少缓冲区的数量从11到9。然后我们重新运行仿真与新参数。

仿真完成后,我们可以打开通道的内存块。在这种情况下,延迟达到一个峰值在23秒到仿真,达到大约78毫秒的延迟。记住,最大允许延迟时间是100毫秒,所以现在我们很安全限制。

然后我们重新检查,看我们是否在要求的不到1 10000年样本。当我们看同样的三个变量,我们可以看到,样品没有被删除。这意味着我们现在有一个设计,满足我们的两个条件。

现在我们使用模拟与SoC Blockset确定帧大小和缓冲区的数目,我们准备在硬件实现的设计在一个FPGA板,我们可以执行与SoC Blockset进一步测试来验证我们的仿真结果。

总结,我们使用SoC Blockset增强模型的算法与硬件的影响,所以我们可以使用模拟,看看不同的帧的大小和数量的缓冲性能的影响。

通过模拟一个算法的硬件架构,我们可以发现延迟和减少样本等问题在实现硬件。

你也可以从下面的列表中选择一个网站:

表现最好的网站怎么走吗

选择中国网站(中文或英文)最佳站点的性能。其他MathWorks国家网站不优化的访问你的位置。