Deep Learning HDL Toolbox

原型并在FPGA和SOC上部署深度学习网络

深度学习HDL Toolbox™提供原型的功能和工具,并在FPGA和SOC上实现深度学习网络。它提供预先构建的比特流,用于在支持的Xilinx上运行各种深度学习网络万博1manbetx®和英特尔®FPGA and SoC devices. Profiling and estimation tools let you customize a deep learning network by exploring design, performance, and resource utilization tradeoffs.

深度学习HDL工具箱使您可以自定义深度学习网络的硬件实现,并生成便携式,可综合的Verilog®和vhdl.®任何FPGA部署的代码(使用HDL Coder™和Simulink万博1manbetx®).

Get Started:

可编程深度学习处理器

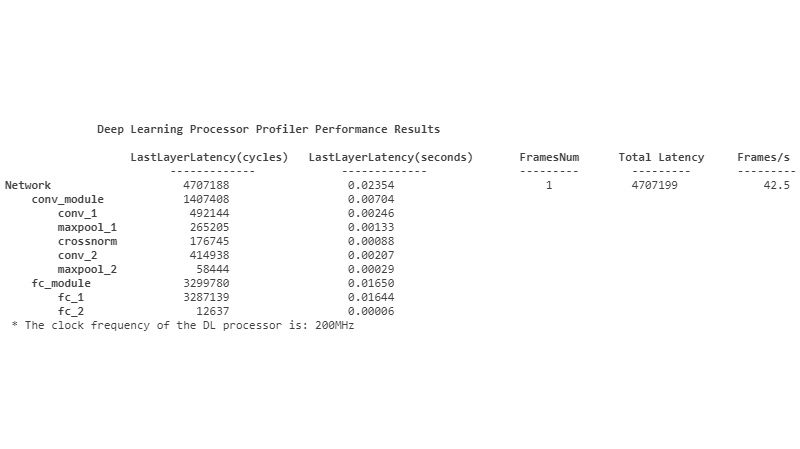

工具箱包括深度学习处理器,该处理器具有通过调度逻辑控制的通用卷积和完全连接的图层。这种深度学习处理器执行使用的基于FPGA的推理使用Deep Learning Toolbox™. High-bandwidth memory interfaces speed memory transfers of layer and weight data.

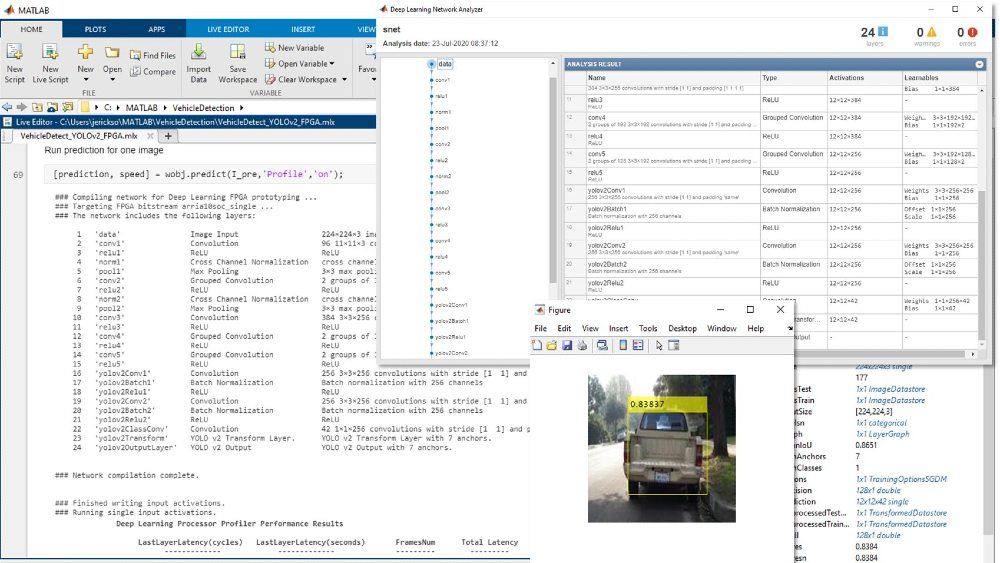

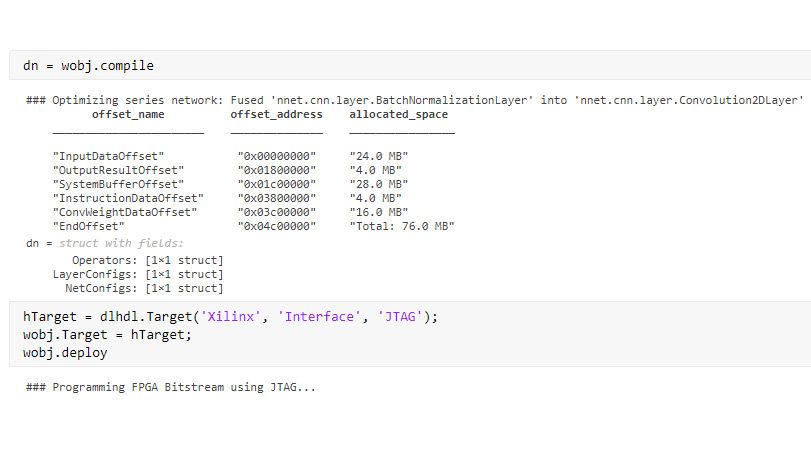

Compilation and Deployment

将您的深度学习网络编译为由深度学习处理器运行的一组指令。在捕获实际的设备上性能指标时部署到FPGA并运行预测。

开始使用预构建比特流

Prototype your network without FPGA programming using available bitstreams for popular FPGA development kits.

创建部署网络

首先使用深度学习工具箱来设计,列车和分析您的深度学习网络,以获取对象检测或分类等任务。您还可以通过从其他框架导入培训的网络或图层来开始。

将您的网络部署到FPGA

Once you have a trained network, use the部署命令用深度学习处理器与以太网或JTAG接口进行编程FPGA。然后用来编译命令为培训的网络生成一组指令,而不重新编程FPGA。

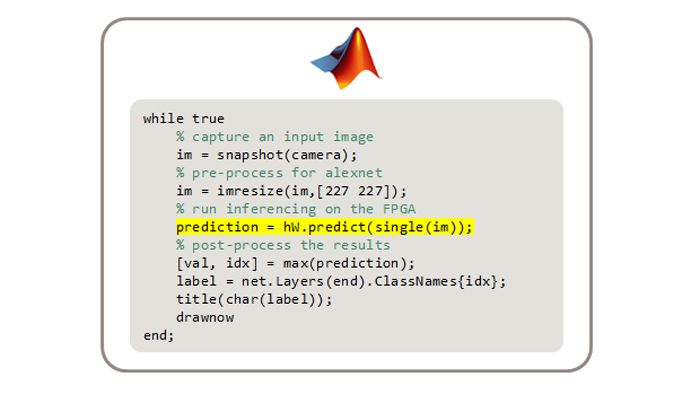

Running FPGA-Based Inferencing as Part of Your MATLAB Application

在matlab中运行整个应用程序®,包括您的测试台,预处理和后处理算法,以及基于FPGA的深度学习推理。单个matlab命令,predict, performs the inferencing on the FPGA and returns results to the MATLAB workspace.

调整网络设计

Using the profile metrics, tune your network configuration with Deep Learning Toolbox. For example, use Deep Network Designer to add layers, remove layers, or create new connections.

Deep Learning Quantization

Reduce resource utilization by quantizing your deep learning network to a fixed-point representation. Analyze tradeoffs between accuracy and resource utilization using the Model Quantization Library support package.

Custom Deep Learning Processor Configuration

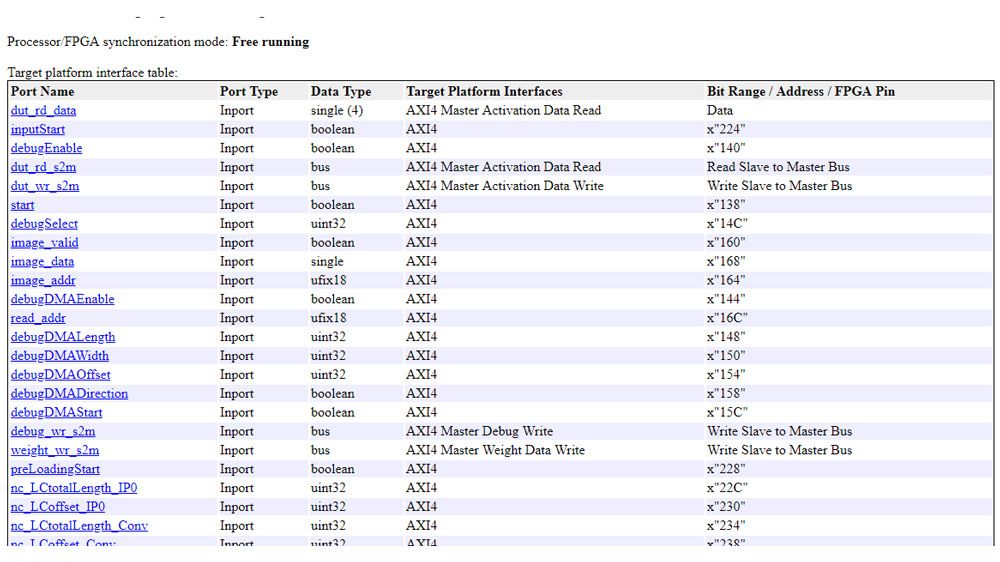

Specify hardware architecture options for implementing the deep learning processor, such as the number of parallel threads or maximum layer size.

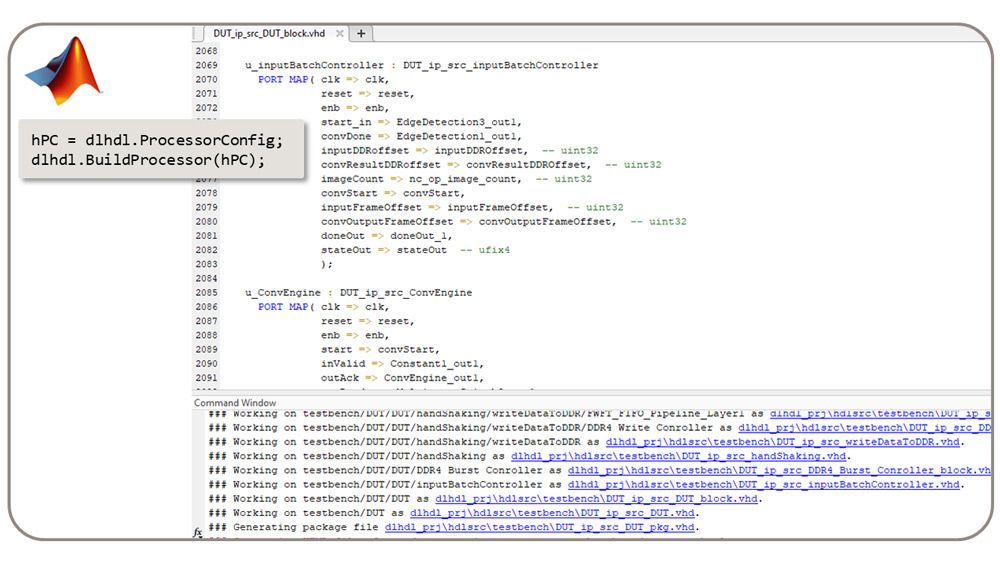

生成可合成的RTL.

使用HDL编码器从深度学习处理器生成可合成的RTL,以用于各种实现工作流程和设备。重用相同的深度学习处理器进行原型和生产部署。

为集成生成IP核心

When HDL Coder generates RTL from the deep learning processor, it also generates an IP core with standard AXI interfaces for integration into your SoC reference design.