优化FIR滤波器

为你的教程文件创建一个文件夹

在MATLAB之外设置一个可写的工作文件夹®安装文件夹,用于存储完成教程工作时生成的文件。本教程的说明假设您创建了该文件夹hdlfilter_tutorials在C盘。

在滤波器设计器中设计FIR滤波器

本教程指导您完成以下步骤:设计优化的量化离散时间FIR滤波器,为滤波器生成Verilog代码,并使用生成的测试台验证Verilog代码。

本节假设您熟悉MATLAB用户界面和过滤器设计器。

启动MATLAB软件。

将当前文件夹设置为您在其中创建的文件夹为你的教程文件创建一个文件夹.

控件启动筛选器设计器

filterDesigner在MATLAB命令窗口中的命令。出现“过滤器设计和分析工具”对话框。

在“过滤器设计和分析工具”对话框中,设置以下过滤器选项:

选项 价值 响应类型 低通滤波器设计方法 冷杉Equiripple过滤器订单 最低订购量 选项 密度系数:20频率的规范 单位:

赫兹Fs:

48000成就:

9600Fstop: 12000

大小规格 单位:

dBapas:

1Astop:

80这些设置适用于过滤器设计器为您创建的默认过滤器设计。如果您不需要更改过滤器,并且设计滤波器是灰色的,你完成了可以跳转到吗量化FIR滤波器.

点击设计滤波器.筛选器设计器为指定的设计创建筛选器。任务完成后,筛选器设计器状态栏中将出现以下消息。

设计滤波器……完成

有关使用滤波器设计器设计滤波器的更多信息,请参阅DSP系统工具箱™文档。

量化FIR滤波器

您必须量化用于HDL代码生成的过滤器。要量化过滤器,

打开中创建的FIR滤波器设计在滤波器设计器中设计FIR滤波器如果它还没有打开。

单击“设置量化参数”按钮

在左侧工具栏中。筛选器设计器显示过滤算法菜单在其对话框的下半部分。

在左侧工具栏中。筛选器设计器显示过滤算法菜单在其对话框的下半部分。

选择

定点从名单上。然后选择指定所有从过滤精度列表。过滤器设计器在其对话框的下半部分显示量化参数的三个选项卡面板中的第一个。

使用量化选项测试各种设置对量化滤波器性能和精度的影响。

量化参数设置如下:

选项卡 参数 设置 系数 分子字长 16最佳精度分数长度 选择使用无符号表示 清除缩放分子系数以充分利用整个动态范围 清除输入/输出 输入字长 16输入分数长度 15输出字长 16过滤器内部 舍入模式 地板上溢出模式 饱和累计字长 40点击应用.

有关使用滤波器设计器量化滤波器的更多信息,请参阅DSP系统工具箱文档。

配置和生成优化的Verilog代码

量化过滤器之后,就可以配置编码器选项并为过滤器生成Verilog代码了。本节将指导您启动UI,设置选项,并为您设计和量化的FIR滤波器生成Verilog代码和测试台在滤波器设计器中设计FIR滤波器而且量化FIR滤波器.

通过选择启动Filter Design HDL Coder™UI目标>产生高密度脂蛋白在过滤器设计器对话框中。过滤器设计器显示生成HDL对话框。

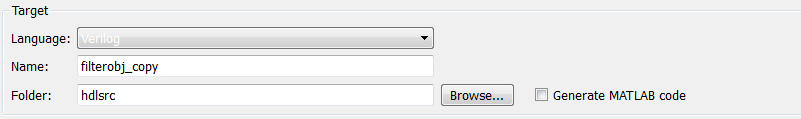

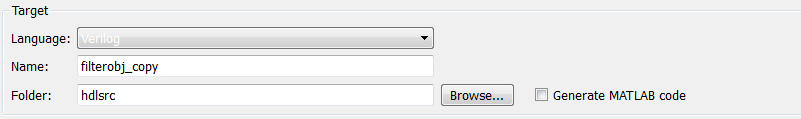

选择

Verilog为语言选项,如下图所示。

在的名字的文本框。目标窗格中,将默认名称替换为

optfir.此选项命名Verilog模块和包含过滤器的Verilog代码的文件。在过滤器体系结构窗格中,选择针对HDL进行优化选择。此选项用于生成针对性能或空间需求进行优化的HDL代码。当启用此选项时,编码器会对数据类型进行权衡,并可能忽略您的量化设置以实现优化。在使用该选项时,请记住,这样做的代价是原始筛选器对象生成的筛选结果与优化HDL代码的模拟结果之间可能存在数值差异。

选择

CSD为乘数系数选择。此选项通过指示编码器将系数乘子操作替换为由标准符号数字(CSD)技术产生的部分乘积的加法来优化系数乘子操作。s manbetx 845这种技术通过用最少的非零数字表示二进制数来最小化常量乘法所需的加法运算次数。选择添加管道寄存器选择。对于FIR滤波器,此选项优化最终求和。编码器创建一个最终加法器,对连续的产品执行成对加法,并在树的每一层之后包含一段管道寄存器。s manbetx 845当用于FIR过滤器时,这个选项可以在原始过滤器对象生成的结果和优化HDL代码的模拟结果之间产生数值差异。

现在出现Generate HDL对话框,如图所示。

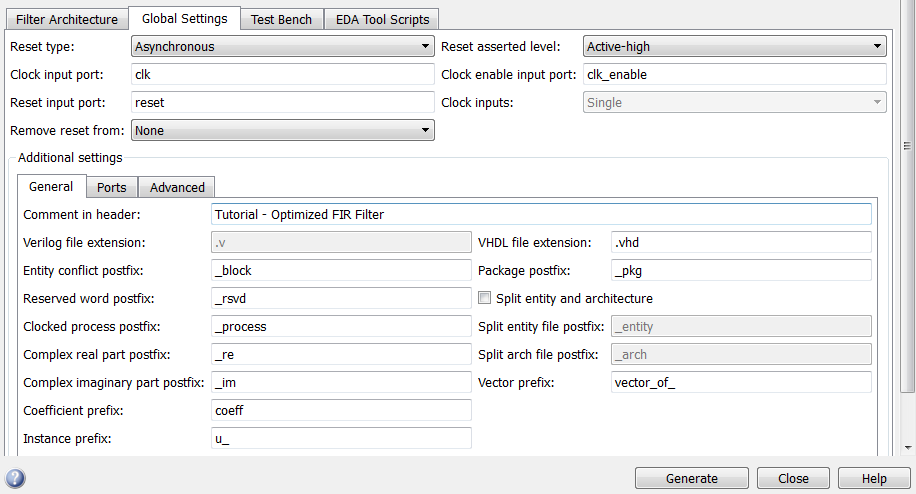

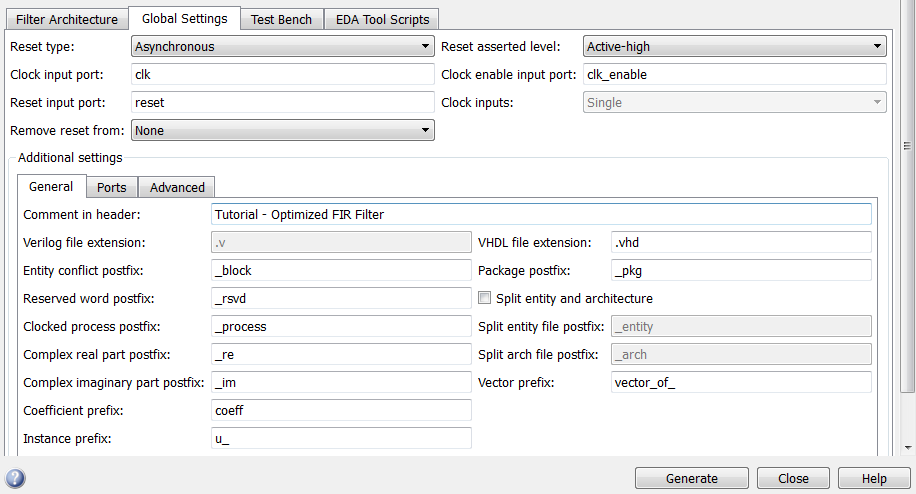

选择全局设置界面的选项卡。然后选择一般的标签。附加的设置部分。

在标头注释文本框,键入

教程-优化的FIR滤波器.编码器将注释添加到每个生成文件的头注释块的末尾。

选择港口的标签。附加的设置部分的UI。

修改输入、输出端口名称。在输入端口文本框,替换

filter_in与data_in.在输出端口文本框,替换filter_out与data_out.

属性的复选框添加输入寄存器选择。的港口窗格现在看起来如所示。

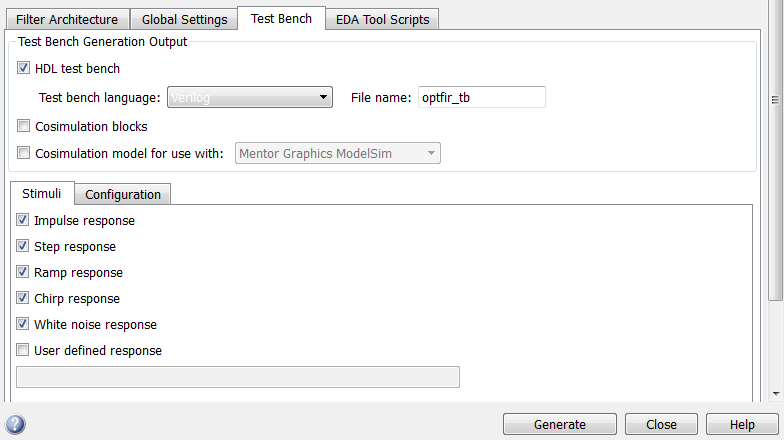

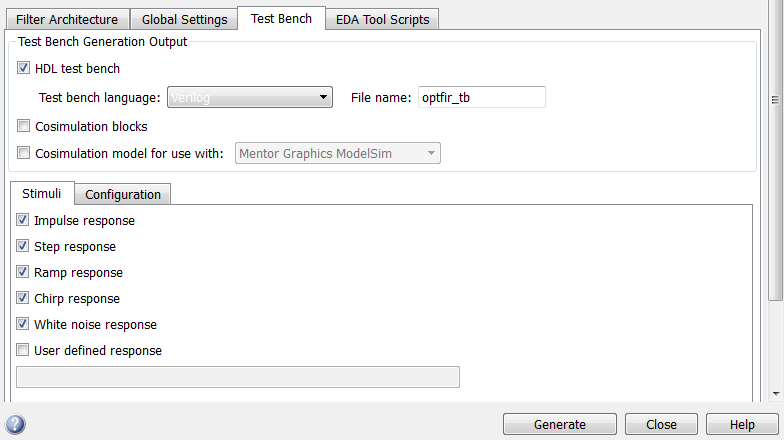

单击试验台选项卡中的生成HDL对话框。在文件名称文本框中,将默认名称替换为

optfir_tb.这个选项命名生成的测试平台文件。

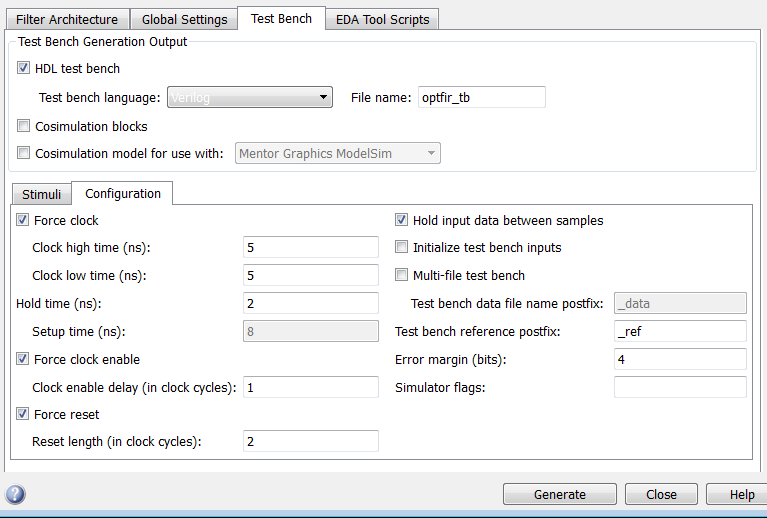

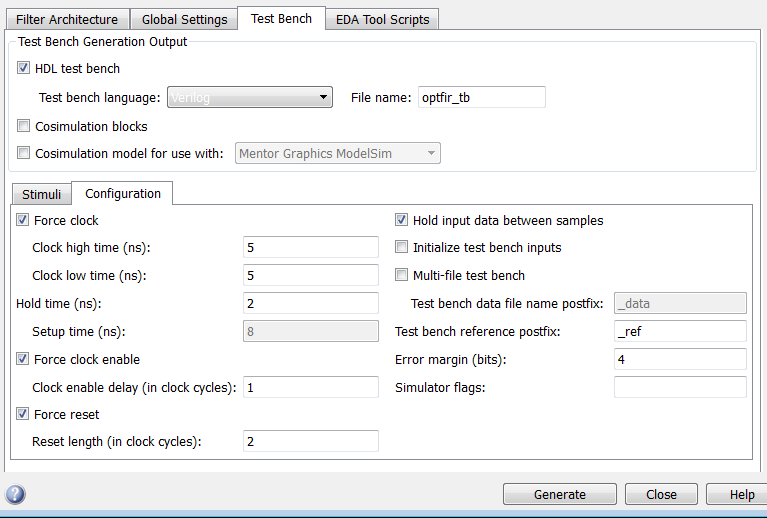

在Test Bench窗格中,单击配置选项卡。观察到误差幅度(位)选项已启用。启用此选项是因为先前选择的优化选项(例如添加管道寄存器)可能会产生与原始过滤器对象产生的结果不同的数值结果。您可以使用此选项来调整测试台在生成警告之前在比较期间忽略的最低有效位的数量。

在“生成HDL”对话框中,单击生成启动代码生成过程。当代码生成完成时,单击关闭关闭对话框。

编码器在MATLAB命令窗口中显示以下消息,因为它生成过滤器和测试台Verilog文件:

###开始Verilog代码生成过程的过滤器:optfir ###生成:C:\hdlfilter_tutorials\hdlsrc\optfir。v ### optfir Verilog模块开始生成### optfir Verilog模块主体开始生成### HDL延迟为8个样本###过滤器Verilog代码生成过程成功完成:optfir ### Verilog测试台开始生成###生成输入刺激###已生成输入刺激;长度3429个样本。生成测试台:C:\hdlfilter_tutorials\hdlsrc\optfir_tbv ###请稍等…完成VERILOG测试台的生成

如消息所示,编码器创建文件夹

hdlsrc在当前工作文件夹下并放置文件optfir.v而且optfir_tb.v在那个文件夹里。注意,这些消息包括到生成的代码和测试台架文件的超链接。通过单击这些超链接,您可以直接在MATLAB编辑器中打开代码文件。

生成的Verilog代码具有以下特点:

Verilog模块命名

optfir.当复位信号激活时使用异步复位的寄存器high(1)。

生成优化数据类型使用并消除冗余操作的代码。

系数乘数优化与CSD技术。

使用流水线技术优化的最终求和。

端口名称如下:

Verilog港口 的名字 输入 data_in输出 data_out时钟输入 clk时钟使能输入 clk_enable复位输入 重置用于处理过滤器输出的额外寄存器。

系数为

多项式系数,在那里nn是系数数,从1开始。0连接时使用类型安全表示:

'0' & '0'...后缀

“_process”被追加到sequential (开始)块名称。

生成的测试台:

是一个可移植的Verilog文件。

强制clock、clock enable和reset输入信号。

强制时钟使能输入信号高激活。

驱动时钟输入信号高(1)5纳秒,低(0)5纳秒。

强制重置信号两个周期加上2纳秒的保持时间。

对数据输入信号应用2纳秒的保持时间。

应用4位的误差率。

对于FIR滤波器,应用脉冲,步进,斜坡,啁啾和白噪声刺激类型。

探索优化生成的Verilog代码

通过打开和浏览文件来熟悉优化生成的Verilog代码optfir.v在ASCII或HDL模拟器编辑器中:

打开生成的Verilog过滤器文件

optcfir.v.搜索

optfir.属性的值标识Verilog模块的名字选项中的目标窗格。参见第3步配置和生成优化的Verilog代码.搜索

教程.代码的这部分是编码器放置您为标头注释选择。参见第9步配置和生成优化的Verilog代码.搜索

HDL代码.本节列出中修改的编码器选项配置和生成优化的Verilog代码.搜索

过滤器设置.VHDL代码的这部分描述了过滤器设计和量化设置在滤波器设计器中设计FIR滤波器而且量化FIR滤波器.搜索

模块.的值命名Verilog模块的名字选项中的目标窗格。属性上的选项定义的端口列表港口面板的生成HDL对话框。属性指定的值命名用于数据输入和输出的端口输入端口而且输出端口的选项港口选项卡的生成HDL对话框。请参见步骤3和步骤11配置和生成优化的Verilog代码.搜索

输入.这一行和后面的四行声明了每个端口的方向模式。搜索

常量.这段代码定义了系数。它们使用默认命名方案命名,多项式系数,在那里nn是系数数,从1开始。搜索

信号.此代码定义了滤波器的信号。搜索

sumvector1.这部分代码声明了实现流水线最终加法器实例的信号。还包括了另外四个流水线最终加法器的信号声明。方法所指定的流水线FIR加法器样式优化使用这些信号来实现添加管道寄存器选择。参见第7步配置和生成优化的Verilog代码.搜索

过程.的块的名字Delay_Pipeline_process包括默认的块后缀“_process”.搜索

重置.这段代码断言复位信号。指定了缺省值active high(1)。还要注意过程在为寄存器生成代码时应用默认的异步重置样式。搜索

posedge.当过滤器对寄存器进行操作时,Verilog代码检查上升边。搜索

sumdelay_pipeline_process1.此块实现了在第7步中指定的管道FIR加法器样式的管道寄存器阶段配置和生成优化的Verilog代码.搜索

output_register.这段代码将过滤器输出写入输出寄存器。默认情况下会生成该寄存器的代码。第12步配置和生成优化的Verilog代码,你清除了添加输入寄存器选项,却离开了添加输出寄存器选中。还要注意进程名Output_Register_process包括默认的过程后缀“_process”.搜索

data_out.这段代码驱动过滤器的输出数据。

验证生成的Verilog代码

本节解释如何使用生成的Verilog测试台验证优化后的FIR滤波器生成的Verilog代码。本教程使用导师图形®ModelSim®模拟器作为编译和模拟Verilog代码的工具。您可以使用其他HDL仿真工具包。

要验证过滤器代码,请完成以下步骤:

启动模拟器。当你开始Mentor Graphics ModelSim模拟器中,屏幕显示如下所示。

将当前文件夹设置为包含生成的Verilog文件的文件夹。例如:

cd hdlsrc

如果需要,可以创建一个设计库来存储编译后的Verilog模块。在Mentor Graphics ModelSim控件创建设计库时,可以使用

vlib命令。vlib工作

编译生成的过滤器和测试台Verilog文件。在Mentor Graphics ModelSim控件来编译Verilog代码

视频博客命令。下面的命令编译过滤器和过滤器测试平台Verilog代码。视频博客optfir。V vlog optfir_tb.v . log

下面的屏幕显示了这个命令序列和编译期间显示的信息消息。

加载试验台进行模拟。加载测试台的过程因所使用的模拟器而异。在Mentor Graphics ModelSim仿真器,加载试验台进行仿真

vsim命令。例如:vsim optfir_tb

下面显示加载的结果

optfir_tb与vsim命令。

打开一个显示窗口,以便在测试台架运行时监视模拟。在Mentor Graphics ModelSim模拟器,可以使用以下命令打开一个波窗口并将模拟结果作为HDL波形查看。

添加波浪*

以下波窗口:

要开始运行模拟,请为模拟器发出启动模拟命令。例如,在Mentor Graphics ModelSim控件启动模拟程序,可以使用

运行命令。下面的显示显示

运行-命令用于启动模拟。

在运行测试台架模拟时,请注意错误消息。如果出现错误消息,则将其解释为与过滤器设计和所选HDL代码生成选项有关。根据生成筛选器Verilog代码时指定的自定义确定结果是否符合预期。

以下波窗口显示仿真结果为HDL波形。