使用SystemVerilog DPI试验台验证HDL设计

这个例子展示了如何使用SystemVerilog DPI试验台验证的HDL代码需要一个大数据集。

在某些应用程序中,模拟需要大量样本中验证高密度脂蛋白HDL编码生成的代码™的算法。例如,这些应用程序需要大量的样本用于算法验证:

)计算雷达天文学的频率通道使用多相滤波器组。

b)获得比特误码率(BER)的维特比译码器在通信系统中。

c) Pixel-streaming视频处理算法对高分辨率的视频。

生成一个高密度脂蛋白试验台验证这样一个设计费时,因为编码器必须在仿真软件模拟模型®捕捉试验台数据。万博1manbetx

更快的生成的试验台替代HDL验证者™SystemVerilog DPI试验台。SystemVerilog DPI试验台不需要仿真软件模拟,所以在大型数据集生成一个试验台比高密度脂蛋白万博1manbetx试验台在更短的时间。

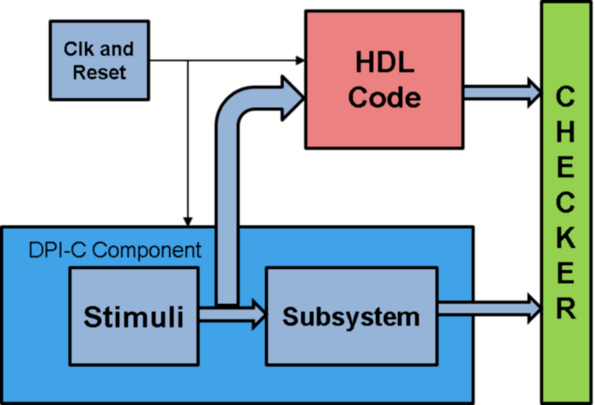

高密度脂蛋白校验SystemVerilog DPI试验台与仿真软件集成编码器™出口仿真软件系统生成C代码在一个Sys万博1manbetxtemVerilog组件直接编程接口(DPI)。在DPI-C组件内生成刺激也应用于C子系统和应用仿真软件生成的HDL代码系统。万博1manbetx这个试验台对比HDL的输出与DPI-C组件的输出仿真验证HDL设计。

多相滤波器组

多相滤波器组是一种广泛使用的技术来减少不准确的FFT由于泄漏和扇形边损失。多相滤波器组产生平坦响应比正常的DFT通过抑制带外信号明显。

模型是一个多相滤波器组由一个过滤器和一个FFT处理16个样本。关于多相滤波器组看到的更多信息高通量对FPGA信道器。

modelname =“hdlcoder_DPIC_testbench”;open_system (modelname);

建立了模型

InitFcn回调(模型属性> > InitFcn回调)设置模式。在这个例子中,512点FFT与每个乐队的四抽头滤波器使用。dsp。信道器对象用于生成系数。

该算法需要512过滤器(一个过滤器为每个乐队)。对于一个向量输入16个样品过滤器实现股票的16个过滤器,32倍。输入数据包含两个正弦波,200 KHz和250千赫。

生成HDL代码、高密度脂蛋白试验台和SystemVerilog DPI试验台

使用一个临时目录中生成的文件:

workingdir = tempname;

检查PolyphaseFilterBank子系统的HDL代码生成的兼容性:

checkhdl (“hdlcoder_DPIC_testbench / PolyPhaseFilterBank”,“TargetDirectory”,workingdir);

运行以下命令来生成HDL代码:

makehdl (“hdlcoder_DPIC_testbench / PolyPhaseFilterBank”,“TargetDirectory”,workingdir);

运行以下命令生成试验台:

makehdltb (“hdlcoder_DPIC_testbench / PolyPhaseFilterBank”,“TargetDirectory”,workingdir);

这将生成一个高密度脂蛋白试验台模拟模型的仿真软件,然后捕捉试验台数据。万博1manbetx

运行以下命令来生成SystemVerilog DPI试验台:

HDLSimulator =“ModelSim”;% 万博1manbetx= ModelSim的模拟器支持选项,“尖锐”,“风投”,“Vivado”

makehdltb (“hdlcoder_DPIC_testbench / PolyPhaseFilterBank”,“TargetDirectory”workingdir,“GenerateSVDPITestBench”HDLSimulator,“GenerateHDLTestBench”,“关闭”);

这个命令生成一个SystemVerilog没有运行仿真软件仿真试验台。万博1manbetx而不是模拟、出口仿真软件系统生成的C代码的代码在一个SystemVerilog组件。万博1manbetx试验台验证输出数据通过比较它与高密度脂蛋白的输出设计。makehdltb函数还生成simulator-specific脚本编译和仿真。

SystemVerilog DPI试验台可以用来验证HDL设计目标语言——硬件描述语言(VHDL)®和Verilog®。

此外,您可以设置SystemVerilog DPI试验台选项“HDL代码生成>试验台”窗格中配置参数。

生成SystemVerilog DPI试验台工件

当你要求一个SystemVerilog DPI试验台,编码器生成以下工件:

一个)。PolyPhaseFilterBank_dpi_tb。sv -这是SystemVerilog试验台,验证HDL代码。

b。)PolyPhaseFilterBank_dpi_tb。——这是宏观文件,导师图形ModelSim®使用HDL代码编译和运行仿真试验台。

基于所选择的模拟器,编码器生成一个不同的文件进行编译和仿真试验台。例如,如果您选择“尖锐”,编码器产生的PolyPhaseFilterBank_dpi_tb。sh的编译和仿真的节奏®门齿®。

(可选)生成HDL代码覆盖率报告和数据库

仪器模拟器生成一个高密度脂蛋白HDL代码覆盖率报告和数据库,:

一个)。“HDL代码生成>试验台”窗格中,选中该复选框标记“HDL代码覆盖率”。

b。)当你叫“makehdltb”,“HDLCodeCoverage”设置为“上”。例如:

makehdltb (“hdlcoder_DPIC_testbench / PolyPhaseFilterBank”,“TargetDirectory”workingdir,“GenerateSVDPITestBench”HDLSimulator,“GenerateHDLTestBench”,“关闭”,“HDLCodeCoverage”,“上”);

HDL代码覆盖工件生成后的源目录试验台模拟。

高密度脂蛋白的世代时间比较试验台和SystemVerilog DPI试验台

仿真模型的时间设定在预装的回调(模型属性> > PreLoadFcn回调)

simTime = 1000;

采样频率是2 e + 6赫兹,这意味着仿真生成HDL testbench收集2 e + 9样品。

对于某些应用程序,它需要更多的样品从多相滤波器获得正确的频率。需要增加simTime产生所需的时间也会增加高密度脂蛋白试验台。

这样的应用程序解决方案是使用SystemVerilog DPI试验台。试验台的世代时间是一样的,不管你的测试场景需要多少样品。

你可以增加仿真时间通过改变“simTime”变量。例如生成一个高密度脂蛋白试验台2 e + 12样本,设置:

simTime = 1000000;

表显示了一个比较的时间(以秒为单位)代HDL试验台和SystemVerilog DPI试验台为越来越多的样本(2 e 2 e + 15 + 9):

列= {“NumberOfSamples”;“GenerationTimeHDLTestBench”;“GenerationTimeSystemVerilogDPITestbench”};numSamples = [2 e9; 2 e10; 2 e11; 2 e12汽油;2 e13; 2 e14灯头;2 e15];HDLTBtime = (10、12、59; 504; 4994; 52200; 505506);DPICTBtime =[47, 47岁,47岁,47个;47,47岁,47);CompareTestBenchTimes =表(numSamples HDLTBtime DPICTBtime,“VariableNames”、列);disp (CompareTestBenchTimes);

NumberOfSamples GenerationTimeHDLTestBench GenerationTimeSystemVerilogDPITestbench售予__________________________ _______________________________________ 47 2 e 2 e + 09年10 + 10 12 47 2 e + 11 59 47 504 47 2 e e + 12 + 13 4994 47 52200 47 2 e e + 14 + 15 5.0551 e + 05年47岁

日志的一代时间这两个试验台类型对样本的数量,显示在高密度脂蛋白试验台需要更多的世代时间的增加样品的数量,生成时间SystemVerilog DPI试验台保持不变无论样本的数量。

重对数(numSamples HDLTBtime,“这”numSamples DPICTBtime,“r-o”);xlim ([2 e09 e15]);传奇(“高密度脂蛋白试验台”,“SystemVerilog DPI试验台”,“位置”,“西北”);包含(样品的数量);ylabel (一代”时间(以秒为单位));close_system (modelname 0);

结论

而HDL试验台是少量的样本非常有效,如果你的测试场景需要大量的样本,高密度脂蛋白校验SystemVerilog DPI试验台提供了更快的试验台的一代。