在基于Zynq RFSoC的数字基带上验证毫米波射频电子器件

Matthew Weiner, RF Pixels

新兴的5G网络在毫米波频谱中运行,这意味着与4G网络相比,它们可以以更快的速度传输更多数据,延迟更低。虽然毫米波频谱技术具有巨大的潜力,但它也给设备制造商带来了设计上的挑战。例如,毫米波频谱中的信号受大气和其他物体的影响比低频信号更弱。

我的同事和我正在开发具有专业射频电子硬件的无线电前端,通过波束形成聚焦毫米波信号功率来克服这种衰减。我们的设计结合了多用户、多输入和多输出(MU-MIMO)技术。

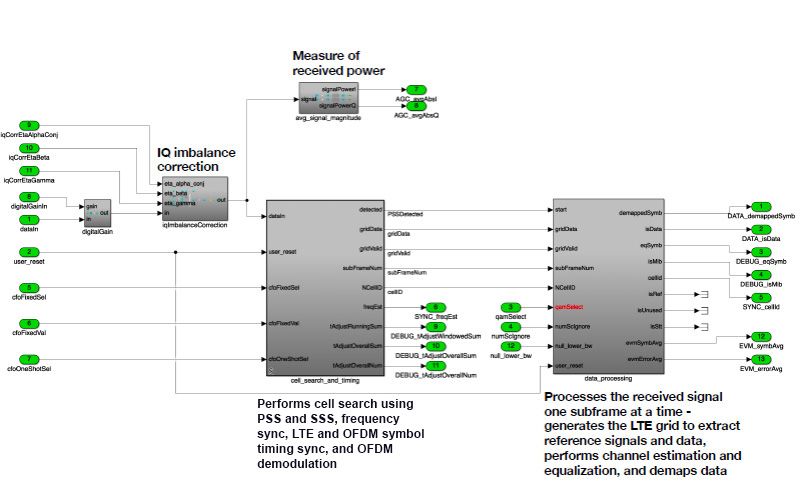

为了测试和演示这些设计,我们在MATLAB中实现了自己的数字基带®和仿真软万博1manbetx件®(图1)我们通过调整无线HDL工具箱™中的LTE黄金参考模型并将其部署到Zynq中来加速实现®UltraScale+™RFSoC板使用HDL Coder™。这种方法为我们节省了至少一年的工程工作,并使我能够自己完成实现,而无需雇用额外的数字工程师。

数字基带的建模与仿真

无线HDL工具箱提供的黄金参考LTE模型开箱即用,提供了许多关键功能,例如主信息块(MIB)解码。我使用这些功能构建了一个自定义的类似4g的OFDM收发器链,增强了现有的时序恢复、载波恢复和均衡。

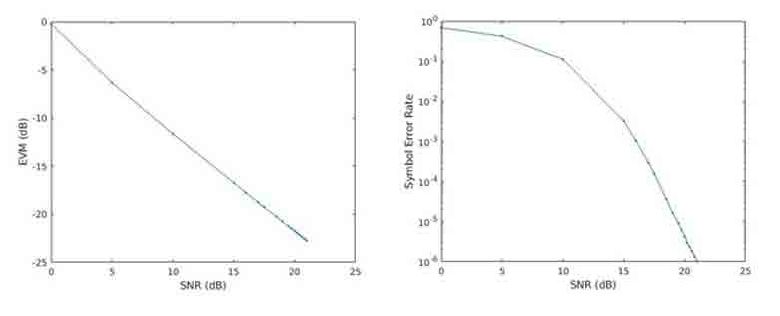

我用无线HDL工具箱中的一个简单信道模型模拟了这个收发器链。模拟使我能够通过评估和可视化各种噪声级别的符号错误率(SER)和错误向量幅度(EVM)等指标来验证基带模型(图2)。

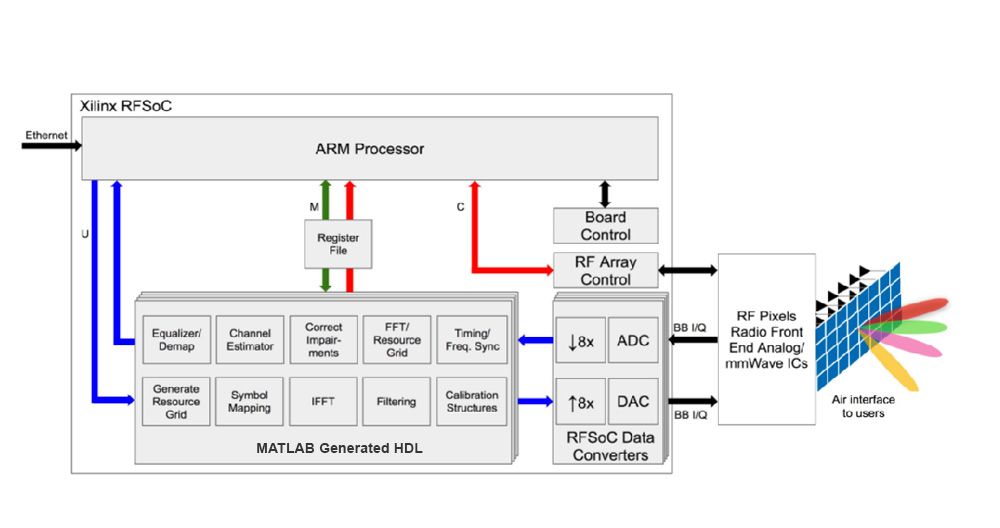

在Zynq RFSoC硬件上实现基带

在通过Simulink仿真验证数字模型后,我用HDL Coder从模型生成RTL代码万博1manbetx,并将其部署到Zynq UltraScale+ RFSoC ZCU111板上。生成的代码既高效又可读。我通过在Zynq板的FPGA上执行数字回环测试来验证实现,将发射输出直接传递回接收链。在这些测试之后,我进行了模拟回环测试,其中在电路板上集成了模数转换器(ADC)和数模转换器(DAC)(图3)。

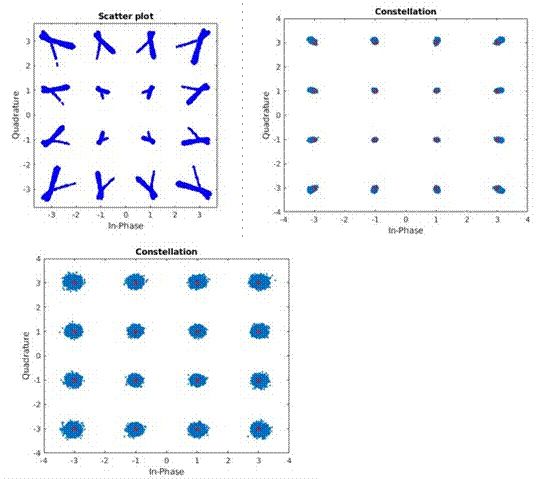

在这一点上,我可以运行完整的板对板测试,并探索射频损伤的影响,使用MATLAB分析从板上捕获的数据,生成星座图,并评估算法增强以解决损伤。

快速设计迭代

在过去,我在更传统的工作流程中工作过,RTL团队实现由系统团队产生的设计。这个工作流中的迭代往往需要很长时间;实现和重新测试算法更改可能需要数周时间。我使用MATLAB和Simulink的迭代要快得多,我通常可万博1manbetx以在几天内实现并重新测试一个增强,如果不是在同一天的话。

在一个实例中,我注意到,虽然系统在系统启动后不久就表现良好,但误码率(BER)随着时间的推移稳步增加。为了诊断问题,我在启动后以不同的时间间隔从ADC中捕获数据,并在MATLAB中进行分析。星座图清楚地显示了性能如何随着时间的推移而下降。

我确定这个问题与采样率偏移有关,它导致LTE帧的循环前缀区域外逐渐漂移。我修改了一个算法来跟踪主同步信号。我通过模拟验证了这个修正,然后在板子上实现了它,在板子上,我看到无论系统运行多长时间,误码率都保持在很低的水平(图4)。

后来,我发现了一个IQ增益和相位不平衡的问题。虽然我们认为我们已经很好地校准了我们的系统来处理IQ不平衡,但我发现校准参数值不正确。我再一次在MATLAB中分析捕获的数据,然后在MATLAB中执行快速暴力搜索,以找到适当的校准值来纠正问题。我更新了Simulink模型万博1manbetx以实现更改,并在几分钟内生成代码以在活动硬件上验证修复。

改进计划

我们正在计划5G版本的数字基带,并致力于扩展我们的射频技术,以满足O-RAN联盟开放无线电接入网络的规范。为我们的设计提供一个O-RAN接口将使我们的IP更容易与其他系统集成,即使我们继续提高性能并添加新功能。

2020年出版的