瑞萨基于模型设计的asic图像处理IP核设计与实现

挑战

解决方案

结果

- 探索了多种设计优化和替代方案

- 生成高效的HDL代码

- 重要的工程技能很快就掌握了

“与传统的设计流程相比,基于模型的设计可以更早地验证我们的算法和系统功能,更快地适应规格变化,并评估更多的设计方案。基于模型的设计有助于弥合算法专家和RTL工程师之间的差距。”

Mamoru Kamiya, Renesas系统设计

瑞萨系统设计是瑞萨电子旗下的设计和应用技术公司,主要开发asic、大规模集成电路(LSI)系统、微型计算机等电子产品的核心技术。s manbetx 845这些核心技术包括用于汽车显示系统和数字成像设备的先进图像处理和滤波算法。

为了加速asic图像处理知识产权(IP)核心的设计和实现,瑞萨的工程师采用了MATLAB的基于模型的设计®和仿真软万博1manbetx件®.

瑞萨系统设计公司高级设计工程师Kamiya Mamoru表示:“因为我们开发的IP核将用于多种产品,所以它必须既高s manbetx 845质量又灵活。”“基于模型的设计使我们能够在开发的早期阶段产生实时原型,系统地探索设计方案,并通过广泛的测试用例模拟建立对我们设计的信心,从而实现这些目标。”

挑战

瑞萨的工程师们用c语言编写了他们的算法的浮点版本。为了将浮点代码转换为定点代码,瑞萨依赖于少数有经验的工程师,他们理解算法,熟悉寄存器传输级(RTL)硬件设计。依赖少数工程师来完成耗时但重要的任务导致了项目瓶颈。HDL代码是基于定点C代码手工编写的,造成了额外的延迟。

瑞萨需要一种开发方法,使他们能够在开发早期完成算法的实时验证。他们还试图将从浮点数到定点转换以及编写HDL代码相关的瓶颈最小化。

解决方案

瑞萨的工程师采用基于模型的设计进行图像处理算法的开发和实现。

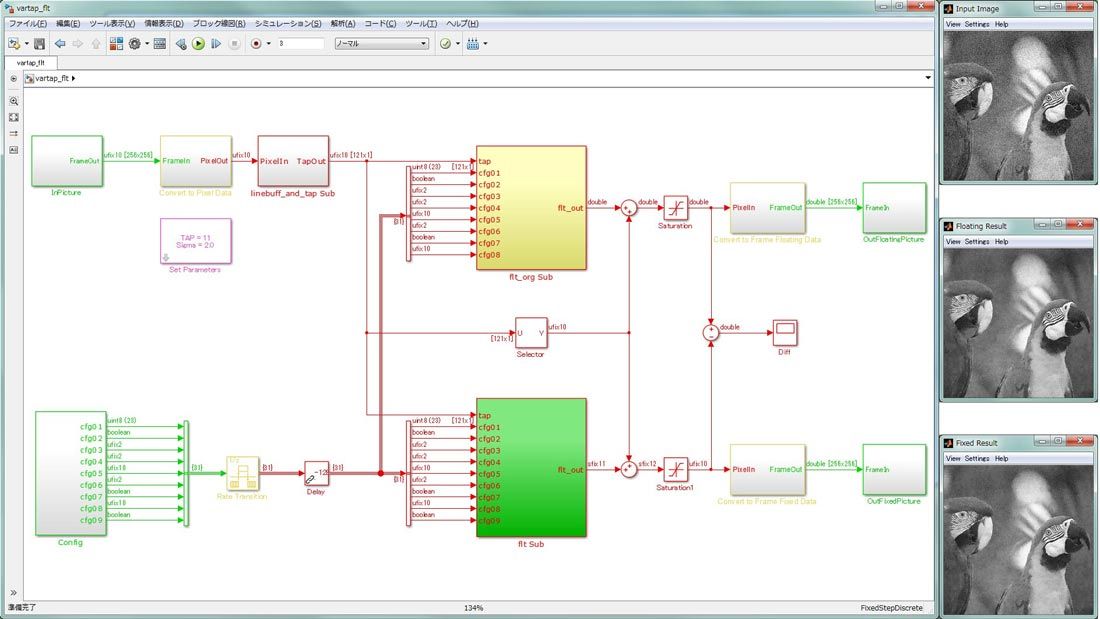

在MATLAB和Simulink中,工程师们万博1manbetx根据规范开发了图像处理系统的浮点模型。他们通过使用通过仿真产生的输出图像来可视化图像处理算法的效果,对模型进行了早期功能验证。

该团队使用计算机视觉工具箱™来可视化来自系统模型的输出图像。

使用定点设计器™,他们将浮点设计转换为定点设计。Fixed-Point Designer中的Fixed-Point Advisor工具使他们能够自动转换步骤,并检测溢流和溢流条件。

在比较了定点和浮点版本的仿真结果后,该团队使用HDL Coder™从优化的Simulink模型中生成可合成的HDL代码。万博1manbetx

使用HDL Coder和HDL Verifier™,团队生成了一个测试台,他们使用该测试台通过与Simulink和Cadence的联合仿真来验证HDL万博1manbetx®敏锐的®.

他们利用MATLAB脚本优化了设计速度和面积,以满足规范要求。该脚本使用一系列HDL Coder资源共享因子和管道选项生成多个版本的代码,并使用Synopsys合成每个版本的代码®设计编译器。然后,研究小组比较了合成结果,以确定最佳设计。

他们将合成的代码部署到Stratix上®来自Altera(现在是英特尔的一部分)的FPGA进行原型测试,然后用从相同的Simulink模型生成的HDL代码合成asic的IP核。万博1manbetx

瑞萨的工程师已经使用Simulink和HDL Coder完成了图像处理系统的开发,并计划在未来的图像处理技术项目中使用基于模型的设计。万博1manbetx

结果

探索了多种设计优化和替代方案.“通过基于模型的设计,我们能够系统地优化设计,通过改变位宽、资源共享因子和管道寄存器的数量,然后重新生成HDL代码,”Kamiya说。“这种能力使得探索替代设计方案和执行参数优化以满足规范变得容易。”

生成高效的HDL代码.Kamiya说:“经过优化后,自动生成的代码基本上与我们最好的手写代码具有相同的面积和速度特征。”“由HDL Coder生成的HDL代码在120 MHz和275 MHz的目标时钟频率上使用的门比我们手写的等效HDL代码略少。”

重要的工程技能很快就掌握了.Kamiya说:“通万博1manbetx过使用Simulink和HDL Coder,一个之前没有硬件经验的工程师在大约六个月的时间里学会了RTL设计。”“这种能力有助于一个只有三名工程师的团队在相同的时间内在FPGA上设计和部署复杂的图像处理算法。”

s manbetx 845产品使用

比较tu éxito

Únete al客户参考计划