主要内容

信道器HDL优化

多相滤波器组和快速傅里叶变换优化的HDL代码生成

- 库:

DSP系统工具箱HDL支持/滤波万博1manbetx

描述

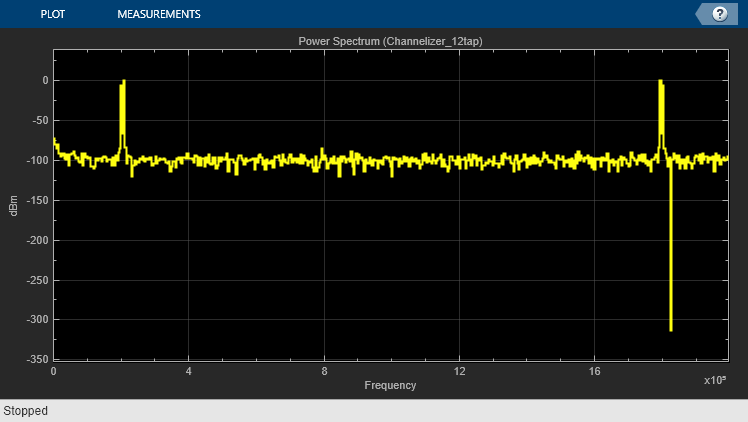

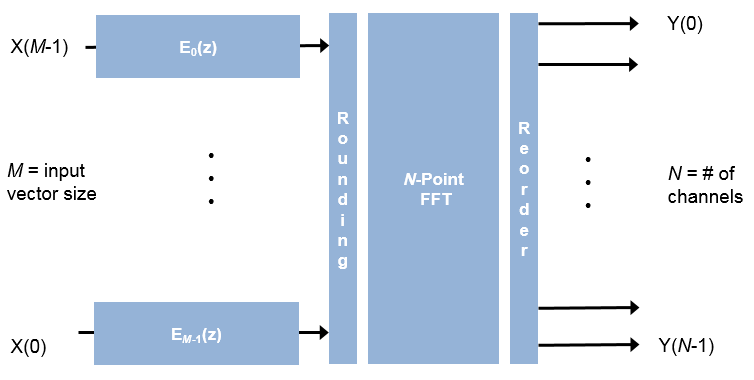

的信道器HDL优化块将一个宽带输入信号分割成多个窄带输出信号。它为流数据应用程序提供硬件速度和区域优化。该块接受实数据或复杂数据的标量或矢量输入,提供硬件友好的控制信号,并具有可选的输出帧控制信号。您可以使用矢量输入来实现每秒千兆采样(GSPS)吞吐量。该块实现了一个多相滤波器,每个输入向量元素有一个子滤波器。硬件实现将子滤波器交叉,从而共享每个滤波器乘数(FFT长度/输入的大小)次。FFT实现使用相同的管道基数2^2 FFT算法FFT HDL优化块。

港口

输入

输出

参数

模型的例子

算法

参考文献

哈里斯,F. J.迪克,M.赖斯。使用多相滤波器组用于无线通信的数字接收机和发射机。IEEE微波理论与技术汇刊.第51卷第4期,2003年4月。

扩展功能

介绍了R2017a