代码生成原理

HDL代码生成启动,语言选择,HDL代码生成脚本

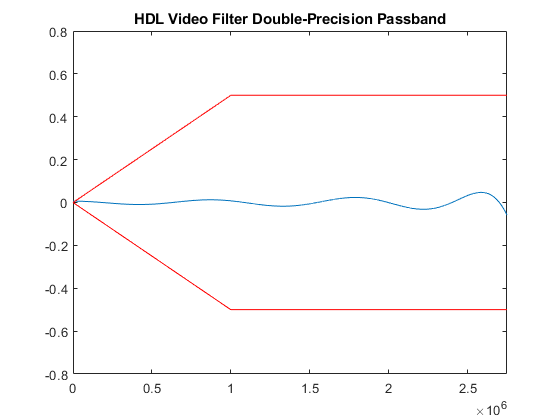

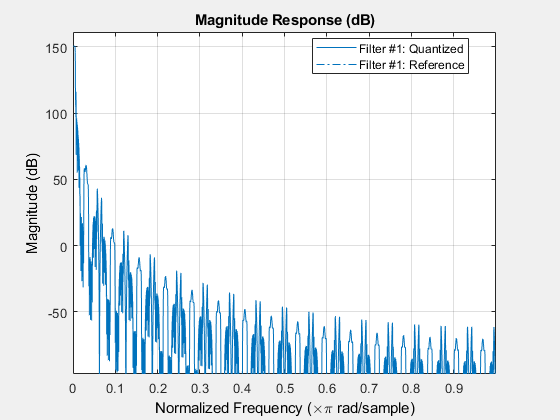

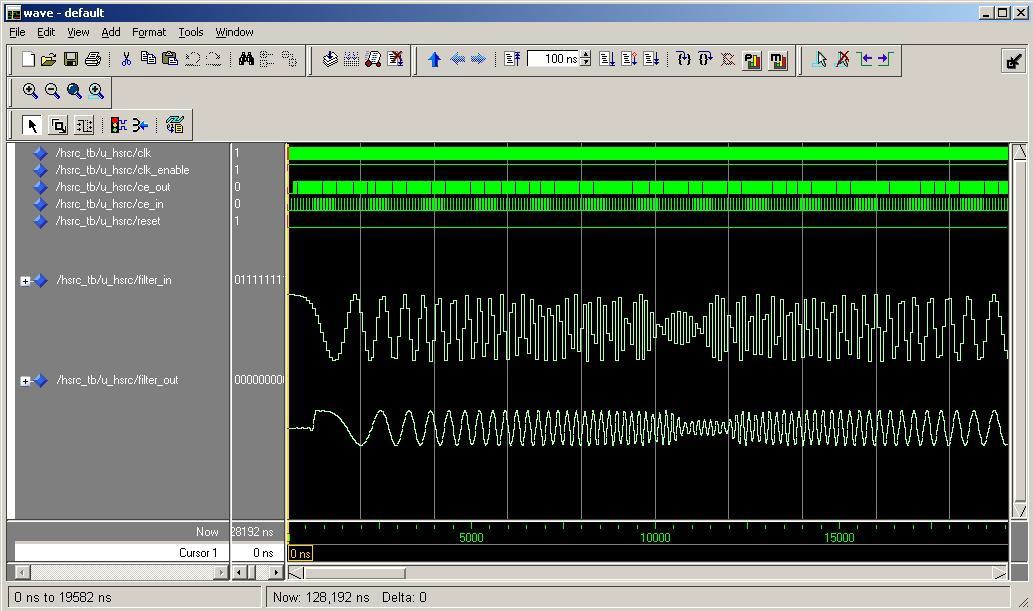

滤波器设计HDL编码器™工作流程能自动化滤波器的实现设计的高密度脂蛋白。首先,设计一个过滤器,手动或通过使用DSP系统工具箱™工具Filter Designer设计或过滤器生成器。然后,使用生成HDL对话框或generatehdl功能配置代码生成选项和生成VHDL或Verilog实现设计的。此流程,就能微调算法,并通过快速原型和实验模型,而在HDL实现花费更少的时间。看到启动滤波器设计HDL编码器。

功能

fdhdltool |

打开生成HDL对话框 |

generatehdl |

生成量化滤波HDL代码 |

属性

| 基本的HDL代码生成属性 | 自定义过滤器的名称,目标文件夹,并指定目标语言 |

主题

进入滤波器设计HDL编码器工具。

选择目标语言。HDL代码在任一VHDL或Verilog被生成。

一旦你的滤波器设计和HDL设置准备,生成HDL代码为您的设计。

为了节省您的代码生成设置,您可以生成一个脚本,其中包括所选的选项。

在会议闭幕前,请保存参数设置。

了解HDL代码生成,从过滤系统对象的具体细节。

您可以生成从DSP系统工具箱™过滤系统对象HDL代码。