深度学习HDL工具箱™提议des函数等des outtils倒原型等implémenter des réseaux de深度学习sur des cartes FPGA et SoC。La工具箱提供des比特流prédéfinis倒exécuter une variété de réseaux de深度学习sur les cartes FPGA et SoC Xilinx®等英特尔®万博1manbetxsupportees。Les outils de profile et d ' estimate vous permeent de personaliser un réseau de深度学习en explorant Les折衷中心设计,性能和资源利用。

Avec深度学习HDL工具箱,vous pouvez personaliser l 'implémentation硬件de votre réseau de深度学习,et générer du代码Verilog®等硬件描述语言(VHDL)®便携式et synthétisable pour le déployer sur n ' import quel FPGA (avec HDL Coder™et Simuli万博1manbetxnk®)

En savoir加:

处理器深度学习可编程

Cette工具箱理解unprocseur de深度学习计算卷积générique et des couches entièrement connectées contrôlées par une loggique d'ordonnancement。Ce处理器de深度学习效果des inférences basées sur des FPGA pour les réseaux développés avec深度学习工具箱™。Des接口mémoire à高级bande passante accélèrent les transferts en mémoire Des données Des couch et de pondération。

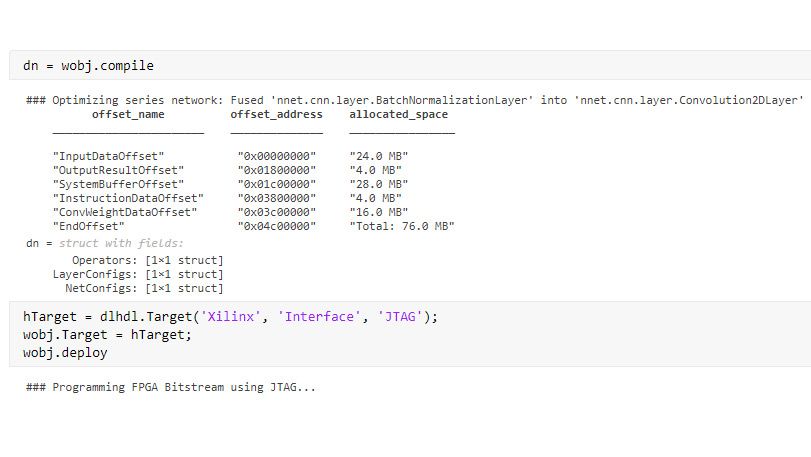

编译et déploiement

Compilez votre réseau de深度学习en un ensemble d'instructions qui seront exécutées par le procseur。Déployez sur le FPGA et réalisez des prédictions tout en collector des métriques de performance sur carte。

Débuter avec des bitstreams prédéfinis

Prototypez votre réseau sans programming de FPGA avec les bitstreams disponibles pour les kits de développement FPGA les plus courants。

Création d’un réseau pour le déploiement

开始使用深度学习工具箱倒concevir, entraîner et analyser votre réseau de深度学习倒des tâches comme la détection ou la分类d'对象。Vous pouvez également commencer par importer un réseau entraîné ou des沙发d' aures框架。

Déploiement de votre réseau sur le FPGA

Après avoir créé votre réseau entraîné, utilisez la command部署倒程序员le FPGA avec le处理器de深度学习等接口以太网ou JTAG。Puis utilisez la command编译pour générer un ensemble d'instructions pour votre réseau entraîné sans avoir à重编程le FPGA。

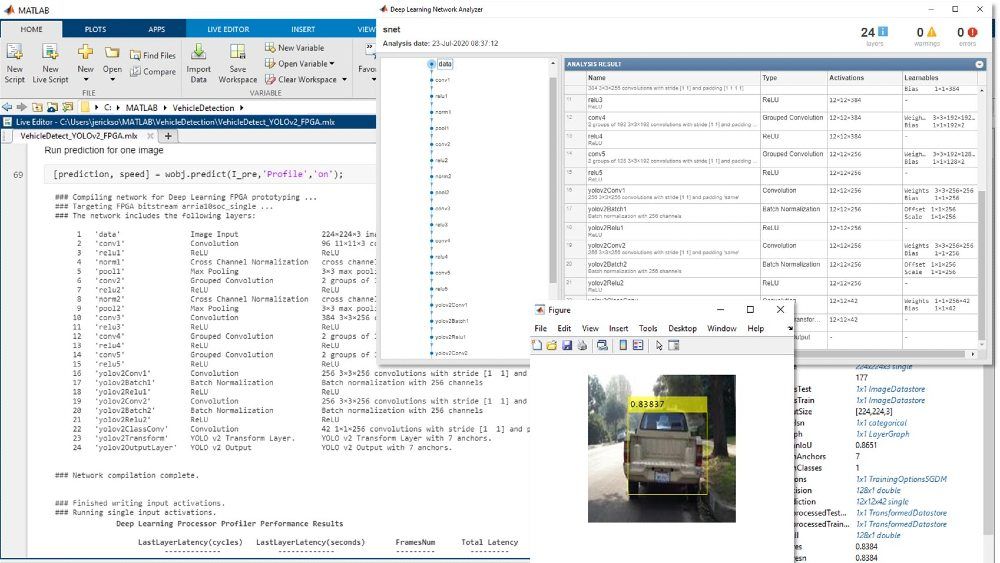

Exécution d'inférences basées sur des FPGA dans votre应用MATLAB

Exécutez l'ensemble de votre应用dans MATLAB®, y包括votre测试台,les算法de prétraitement et de post- tritement, et les inférences de Deep Learning sur FPGA。La command MATLAB预测suffit pour effectuer des inférences sur le FPGA et renvoyer les résultats dans l' space de travail MATLAB。

分析器des inférences FPGA

Mesurez la latence au niveau des沙发lorsque vous réalisez des prédictions sur le FPGA pour identifier les goulots d'étranglement dans les performance。

Ajuster le design du réseau

Ajustez la configuration de votre réseau avec深度学习工具箱,en utilant les métriques de profile。利用举例深网络设计师pour ajouter ou供应商des沙发,ou créer de nouvelles连接。

深度学习量化

Optimisez l' utilization des resources en quantiant votre réseau de Deep Learning vers une représentation virgule fixe。分析les折衷entre la précision et l' utilization des资源avec le支持包模型量化库。万博1manbetx

配置personnalisée du procseur de Deep Learning

Précisez les options d'architecture硬件pour l'implémentation du procseur de Deep Learning, comme le nombre de threads parallèles ou la taille maximale des长沙发。

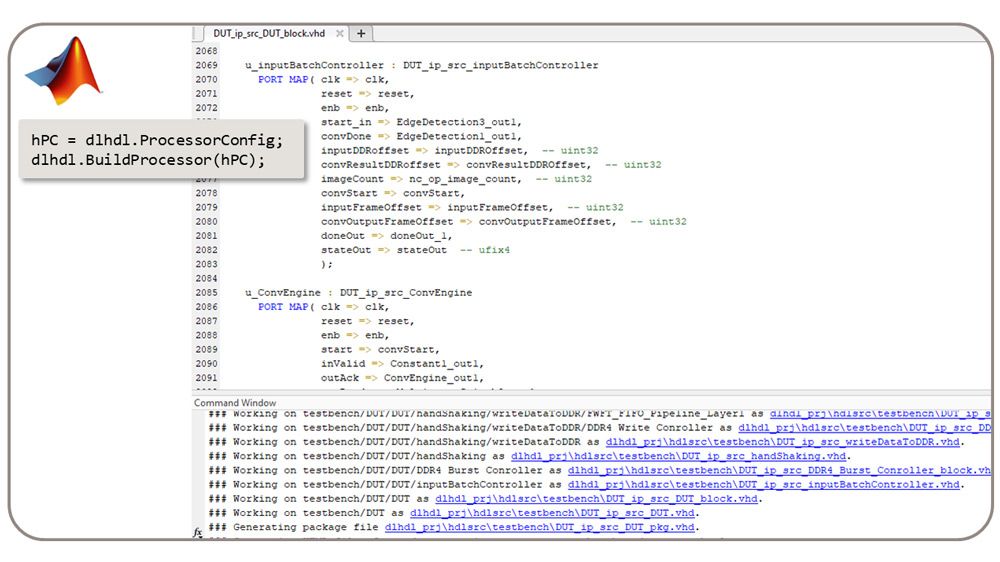

Générer du RTL synthétisable

Utilisez HDL Coder pour générer du RTL synthétisable à partir du procseur de Deep Learning pour une utilisation dans différentes cartes et工作流d'implémentation。Réutilisez le même procseur de Deep Learning pour le prototype et le déploiement en production。

Générer des coeurs IP pour l'intégration

Lorsque HDL Coder génère le RTL à partr du procseur de Deep Learning, il génère également un core IP avec des interfaces AXI standard pour l'intégration dans votre design de référence SoC。