缺陷检测

这个例子展示了如何部署一个定制的训练系列网络来检测物体的缺陷,如六边形螺母。采用迁移学习的方法对自定义网络进行训练。迁移学习通常用于深度学习应用。你可以用一个预先训练好的网络作为学习新任务的起点。用迁移学习对网络进行微调通常比用随机初始化权值从头开始训练网络更快、更容易。使用少量的训练信号,您可以快速地将学到的特征转移到新的任务中。这个例子使用了两个训练过的系列网络,trainedDefNet.mat和trainedBlemDetNet.mat.

先决条件

Xilinx ZCU102 SoC开发工具包

用于Xilinx FPGA和SoC的深度学习HDL工万博1manbetx具箱™支持包

深度学习工具箱™

深度学习HDL工具箱™

负载Pretrained网络

加载定制的预训练系列网络trainedDefNet。

如果〜ISFILE(“trainedDefNet.mat”) url ='//www.tianjin-qmedu.com/万博1manbetxsupportfiles/dlhdl/trawaydefnet.mat';websave (“trainedDefNet.mat”url);结束网络1=负载(“trainedDefNet.mat”);snet_defnet = net1.custom_alexnet

snet_defnet = SeriesNetwork with properties: Layers: [25×1 net.cnn.layer. layer] InputNames: {'data'} OutputNames: {'output'}

分析了网络。analyzeNetwork显示网络体系结构的交互式绘图和包含有关网络层信息的表格。

analyzeNetwork (snet_defnet)

网络负载snet_blemdetnet.

如果〜ISFILE('troustmblemdetnet.mat') url ='//www.tianjin-qmedu.com/万博1manbetxsupportfiles/dlhdl/trainedBlemDetNet.mat';websave ('troustmblemdetnet.mat'url);结束net2 =负载('troustmblemdetnet.mat');snet_blemdetnet = net2.convnet

snet_blemdetnet = SeriesNetwork with properties: Layers: [12×1 net.cnn.layer. layer] InputNames: {'imageinput'} OutputNames: {'classoutput'}

分析了网络。analyzeNetwork显示网络体系结构的交互式绘图和包含有关网络层信息的表格。

分析(Snet_BlemDetNet)

创建目标对象

创建具有目标设备的自定义名称的目标对象以及将目标设备连接到主计算机的接口。接口选项是JTAG和以太网。要使用JTAG连接,请安装Xilinx™Vivado™设计套件2020.1。

设置Xilinx Vivado工具路径。

% hdlsetuptoolpath('ToolName', 'Xilinx Vivado', 'ToolPath', 'C: Xilinx Vivado\2020.1\bin\ Vivado .bat');hT = dlhdl。目标(“Xilinx”,“界面”,“以太网”)

hT = Target with properties: Vendor: 'Xilinx' Interface: Ethernet IPAddress: '192.168.1.101' Username: 'root' Port: 22

创建工作流对象训练defnet网络

对象的对象dlhdl。工作流类。指定网络和位流名称。指定保存的预训练网络trainedDefNet随着网络。确保位流名称与您的目标数据类型和FPGA板匹配。本例中,目标FPGA板为Xilinx ZCU102 SOC板。位流使用单一数据类型。

hW = dlhdl。工作流(“网络”snet_defnet,“比特流”,“zcu102_single”,'目标'hT)

hW =带有属性的工作流:Network: [1×1 SeriesNetwork] Bitstream: 'zcu102_single' ProcessorConfig: [] Target: [1×1 dlhdl. hW = []目标]

编制trainedDefNet系列网络

的compile函数dlhdl。工作流对象。

hW.compile

###编译网络深度学习FPGA原型…### FPGA bitstream zcu102_single…###网络包括以下几层:1的数据图像输入128×128×1图像“zerocenter”正常化(SW层)2 conv1卷积96年11×11×1旋转步[4 4]和填充[0 0 0 0](HW层)3的relu1 ReLU ReLU (HW层)4 norm1的横通道正常化横通道正常化与5频道/元素(HW层)5 pool1马克斯池3×3马克斯池与步幅[2 2]和填充[0 0 0 0](HW层)6“conv2”分组卷积2组128 5×5×48旋转步[1]和填充[2 2 2 2](HW层)7的relu2 ReLU ReLU (HW层)8“norm2”横通道正常化横通道正常化与5频道/元素(HW层)9“pool2”马克斯池3×3马克斯池步(2 - 2)和填充[0 0 0 0]conv3的卷积(HW层)384 3×3×256旋转步[1]和填充[1 1 1 1](HW层)11的relu3 ReLU ReLU (HW层)12“conv4”分组卷积2组192 3×3×192旋转步[1]和填充[1 1 1 1](HW层)13的relu4 ReLU ReLU (HW层)14“conv5”分组卷积2组128 3×3×192旋转步[1]和填充[1 1 1 1](HW层)15 ' relu5 ReLU ReLU (HW层)16“pool5”马克斯池3×3马克斯池步(2 - 2)和填充[0 0 0 0](HW层)17 fc6完全连接4096完全连接层(HW层)18“relu6”ReLU ReLU (HW层)19 drop6辍学50%辍学(HW层)20 fc7完全连接4096完全连接层(HW层)21 ' relu7 ReLU ReLU (HW层)22“drop7”辍学50%辍学(HW层)23“fc8”完全连接2完全连接层(HW层)24“概率”Softmax Softmax(层)西南25“输出”分类输出crossentropyex类“ng”和“ok”(SW层)3内存创建区域。编译段:conv1>>pool5… Compiling leg: conv1>>pool5 ... complete. Compiling leg: fc6>>fc8 ... Compiling leg: fc6>>fc8 ... complete. Skipping: prob Skipping: output Creating Schedule... ....... Creating Schedule...complete. Creating Status Table... ...... Creating Status Table...complete. Emitting Schedule... ...... Emitting Schedule...complete. Emitting Status Table... ........ Emitting Status Table...complete. ### Allocating external memory buffers: offset_name offset_address allocated_space _______________________ ______________ _________________ "InputDataOffset" "0x00000000" "8.0 MB" "OutputResultOffset" "0x00800000" "4.0 MB" "SchedulerDataOffset" "0x00c00000" "4.0 MB" "SystemBufferOffset" "0x01000000" "28.0 MB" "InstructionDataOffset" "0x02c00000" "4.0 MB" "ConvWeightDataOffset" "0x03000000" "12.0 MB" "FCWeightDataOffset" "0x03c00000" "84.0 MB" "EndOffset" "0x09000000" "Total: 144.0 MB" ### Network compilation complete.

ans =结构体字段:[1×1 struct]注册:[1×1 struct] syncstructions: [1×1 struct]

在FPGA上编程Bitstream并下载网络权重

当需要在Xilinx ZCU102 SoC硬件上部署网络时,需要运行Xilinx的deploy功能dlhdl。工作流对象。该函数使用compile函数的输出,利用编程文件对FPGA板进行编程。它还下载了网络权重和偏差。deploy函数开始对FPGA设备进行编程,并显示进度消息和部署网络所需的时间。

hW.deploy

###使用以太网编程FPGA位流。。。通过以太网将目标FPGA设备配置下载到SD卡…#复制/tmp/hdlcoder\u rd到/mnt/hdlcoder\u rd#复制位流hdlcoder\u system.bit到/mnt/hdlcoder\u rd#设置位流到hdlcoder\u rd/hdlcoder\u system.bit#复制设备树设备树dlhdl.dtb到/mnt/hdlcoder\u rd#设置设备树到hdlcoder\u rd/Devicetree\u dlhdl.dtb#设置引导以供参考设计:“AXI内存访问:3”通过以太网将目标FPGA设备配置下载到SD卡完成。系统现在将重新启动以使持续更改生效。系统正在重新启动FPGA位流编程已成功完成将重量加载到Conv处理器。###已加载Conv砝码。当前时间为2020年12月16日16:16:31#####将权重加载到FC处理器。###完成20%,当前时间为2020年12月16日16:16:32完成40%,当前时间为2020年12月16日16:16:3260%完成,当前时间为2020年12月16日16:16:3380%完成,当前时间为2020年12月16日16:16:34已加载FC权重。当前时间为2020年12月16日16:16:34

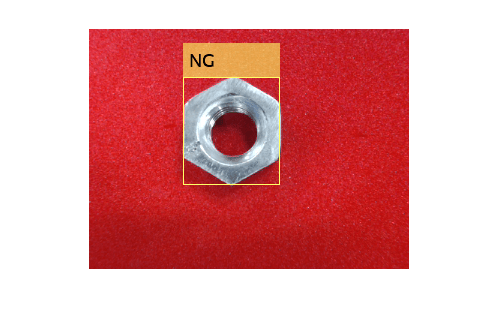

运行对一个图像的预测

从附件中加载图像testImages文件夹并调整图像大小以匹配网络图像输入层尺寸。运行预测功能dlhdl。工作流对象从FPGA中检索和显示缺陷预测。

wi = uint32 (320);他= uint32 (240);ch = uint32 (3);文件名= fullfile (pwd,“ng1.png”);img = imread(文件名);Img = imresize(Img,[他,wi]);img = mat2ocv (img);%提取ROI进行预处理[Iori, imgpack, num, bbox] = myNDNet_Preprocess(img); / /上传数据%主行到主列的转换imgPacked2=零([128128,4],“uint8”);对于c = 1:4对于i = 1:128对于j = 1:128 imgPacked2 (i, j c) = imgPacked((张)* 128 + (j - 1) +(颈- 1)* 128 * 128 + 1);结束结束结束%利用CNN对检测到的坚果进行分类分数=零(2,4);对于i=1:num[分数(:,i),速度]=hW.predict(单个(imgPacked2(:,:,i)),'轮廓',“开”);结束

###完成写入输入激活。###运行单输入激活。Deep Learning Processor Profiler Performance Results LastFrameLatency(cycles) LastFrameLatency(seconds) FramesNum Total Latency Frames/s ------------- ------------- --------- --------- --------- Network 12231156 0.05560 1 12231156 18.0 conv1 414021 0.00188 norm1 172325 0.00078 pool1 56747 0.00026 conv2 654112 0.00297 norm2 119403 0.00054 pool2 . Deep Learning Processor Profiler Performance Results LastFrameLatency(cycles) LastFrameLatency(seconds) FramesNum Total Latency Frames/s43611 0.00020 conv3 777446 0.00353 conv4 595551 0.00271 conv5 404425 0.00184 pool5 17831 0.00008 fc6 1759699 0.00800 fc7 7030188 0.03196 fc8 185672 0.00084 * DL处理器的时钟频率为:220MHz

Iori =重塑(Iori,[1,他*wi*ch]);Bbox =重塑(Bbox, [1,16]);Scores =重塑(Scores, [1,8]);%插入用于后处理的注释Out = MyNDNet_PostProcess(IORI,Num,Bbox,Scors,Wi,He,Ch);sz = [他wi ch];出= ocv2mat(出,sz);imshow(出)

创建工作流对象trainedBlemDetNet网络

对象的对象dlhdl。工作流类。指定网络和位流名称。指定保存的预训练网络trainedblemDetNet随着网络。确保位流名称与您的目标数据类型和FPGA板匹配。本例中,目标FPGA板为Xilinx ZCU102 SOC板。位流使用单一数据类型。

hW = dlhdl。工作流(“网络”snet_blemdetnet,“比特流”,“zcu102_single”,'目标'hT)

hW =带有属性的工作流:Network: [1×1 SeriesNetwork] Bitstream: 'zcu102_single' ProcessorConfig: [] Target: [1×1 dlhdl. hW = []目标]

编制培训blemdetnet系列网络

的compile函数dlhdl。工作流对象。

hW.compile

###编译深度学习网络FPGA原型... ###定位FPGA比特流ZCU102_Single ... ###网络包括以下图层:1'ImageInput'图像输入128×128×1图像,具有“Zerocenter”归一化的图像(SW层)2'CROM_1'卷积20 5×5×1卷绕升温[11]和填充[0 0 0 0](HW层)3'Relu_1'Creu Relu(HW层)4'MAXPOOL_1'MAX池2×2最大汇集步进[2 2]和填充[0 0 0 0](HW层)5'交叉频道归一化交叉通道归一化交叉通道标准化,每个元素(HW层)6'conv_2'卷积20 5×5×20卷绕升级[11]和填充[0 0 0 0](HW层)7'Relu_2'Relu Relu(HW层)8'MaxPool_2'最大池2×2最大池与步幅[2]和填充[0 0 0](HW层)9'FC_1'完全连接的512完全连接的层(HW层)10'FC_2'完全连接的2完全连接的层(HW层)11'SoftMax'Softmax Softmax(SW层)12'ClassOutput'分类输出CROSSentRopyex与类“NG”和“OK”(SW层)创建的3个内存区域。跳过:imageInput编译腿:conv_1 >> maxpool_2 ...编译腿:conv_1 >> maxpool_2 ...完成。编译腿:FC_1 >> FC_2 ...编译腿:FC_1 >> FC_2 ...完成。跳过:softmax跳过:ClassOutput创建计划.......创建时间表...完成。创建状态表......创建状态表...完成。 Emitting Schedule... ...... Emitting Schedule...complete. Emitting Status Table... ........ Emitting Status Table...complete. ### Allocating external memory buffers: offset_name offset_address allocated_space _______________________ ______________ ________________ "InputDataOffset" "0x00000000" "8.0 MB" "OutputResultOffset" "0x00800000" "4.0 MB" "SchedulerDataOffset" "0x00c00000" "4.0 MB" "SystemBufferOffset" "0x01000000" "28.0 MB" "InstructionDataOffset" "0x02c00000" "4.0 MB" "ConvWeightDataOffset" "0x03000000" "4.0 MB" "FCWeightDataOffset" "0x03400000" "36.0 MB" "EndOffset" "0x05800000" "Total: 88.0 MB" ### Network compilation complete.

ans =结构体字段:[1×1 struct]注册:[1×1 struct] syncstructions: [1×1 struct]

在FPGA上编程Bitstream并下载网络权重

当需要在Xilinx ZCU102 SoC硬件上部署网络时,需要运行Xilinx的deploy功能dlhdl。工作流对象。该函数使用compile函数的输出,利用编程文件对FPGA板进行编程。它还下载了网络权重和偏差。deploy函数开始对FPGA设备进行编程,并显示进度消息和部署网络所需的时间。

hW.deploy

### FPGA位流编程已经被跳过,因为相同的位流已经加载到目标FPGA上。###加载权值到Conv处理器。### Conv权重加载。当前时间为16-Dec-2020 16:16:47 ###正在加载FC处理器权重。### 50%完成,当前时间是2020年12月16日16:16:48。### FC权重已加载。当前时间是2020年12月16日16:16:48

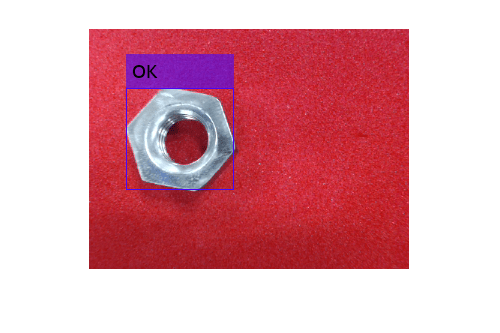

运行对一个图像的预测

从附件中加载图像testImages文件夹并调整图像大小以匹配网络图像输入层尺寸。运行预测功能dlhdl。工作流对象从FPGA中检索和显示缺陷预测。

wi = uint32 (320);他= uint32 (240);ch = uint32 (3);文件名= fullfile (pwd,“ok1.png”);img = imread(文件名);Img = imresize(Img,[他,wi]);img = mat2ocv (img);%提取ROI进行预处理[Iori, imgpack, num, bbox] = myNDNet_Preprocess(img); / /上传数据%主行到主列的转换imgPacked2=零([128128,4],“uint8”);对于c = 1:4对于i = 1:128对于j = 1:128 imgPacked2 (i, j c) = imgPacked((张)* 128 + (j - 1) +(颈- 1)* 128 * 128 + 1);结束结束结束%分类检测到的螺母使用CNN分数=零(2,4);对于i=1:num[分数(:,i),速度]=hW.predict(单个(imgPacked2(:,:,i)),'轮廓',“开”);结束

###已完成输入激活的编写。####运行单输入激活。深度学习处理器探查器性能结果LastFrameLatency(周期)LastFrameLatency(秒)FRAMESUM总延迟帧/秒-------------------------网络4892622 0.02224 1 4892622 45.0 conv_1 467921 0.00213 maxpool_1 188086 0.00085交叉范数159500 0.00072 conv_2 397561 0.00181 maxpool_2 41455 0.00019 fc_1 3614625 0.01643 fc_2 23355 0.00011*DL处理器的时钟频率为:220MHz

Iori =重塑(Iori,[1,他*wi*ch]);Bbox =重塑(Bbox, [1,16]);Scores =重塑(Scores, [1,8]);%插入后处理辅助Out = MyNDNet_PostProcess(IORI,Num,Bbox,Scors,Wi,He,Ch);sz = [他wi ch];出= ocv2mat(出,sz);imshow(出)

量化和部署trainedBlemDetNet网络

这trainedBlemDetNet网络将性能提高到每秒45帧。部署网络的目标性能是100帧/秒,同时保持在目标资源利用预算之内。资源利用预算考虑了内存大小和板载IO等参数。虽然您可以通过选择更大的板来增加资源利用预算,但这样做会增加成本。相反,可以通过量化网络来提高部署的网络性能,并保持在资源利用预算之内。量化和部署trainedBlemDetNet网络。

将数据集加载为图像数据存储。的imageDatastore根据文件夹名称对图像进行标签并存储数据。将数据分为校准和验证数据集。使用50%的图像进行校准,50%的图像进行验证。通过使用校准和验证图像集的子集,加快校准和验证过程。

如果〜ISFILE('dataset.zip') url =“//www.tianjin-qmedu.com/万博1manbetxsupportfiles/dlhdl/dataSet.zip”;websave ('dataset.zip'url);结束解压('dataset.zip')解压缩('dataset.zip') imageData = imageDatastore(fullfile(“数据集”),......“IncludeSubfolders”,真的,“FileExtensions”,“使用”,“LabelSource”,'foldernames'); [calibrationData,validationData]=拆分每个标签(imageData,0.5,“随机”);calibrationData_reduced = calibrationData.subset (1:20);validationData_reduced = validationData.subset (1:1);

创建一个量子化网络使用dlquantizer对象。将目标执行环境设置为FPGA。

dlQuantObj = dlquantizer (snet_blemdetnet,“执行环境”,FPGA的)

dlQuantObj=dlquantizer,具有以下属性:NetworkObject:[1×1 SeriesNetwork]执行环境:“FPGA”

使用校准函数通过使用样本输入练习网络,并收集范围信息校准函数练习网络,并收集网络卷积层和完全连接层中权重和偏差的动态范围,以及网络所有层中激活的动态范围校准函数返回一个表。表的每一行包含量化网络的一个可学习参数的范围信息。

dlquantobj.calibrate(CalibrationData_Reducy)

ans =21×5表(UUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUU(小标题)(小标题)(小标题)(小标题)(小标题)(小标题)(小标题))(小标题)(小标题)(小标题))(小标题)小标题10.10.10.10.10.10.10.10.10.10.10.10.10.10.10.10.10.10.10.10.577 7 7 7 7 7 7 7 7 7 0.0.0.0.0.0.0.0.0.0.0 577 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7{'imageinput'}{'imageinput'}“激活”0 255{'imageinput{U归一化'}{'imageinput'}“激活”-184.37 241.75{'Convu 1'}{'Convu 1'}“激活”-112.18 150.51{'relu 1'}{'relu 1'}“激活”0 150.51{'maxpool_1'}{'maxpool_1'}“激活”0 150.51{'crossnorm'}{'crossnorm'}“激活”0 113.27{Convu 2'}{'relu_2'}“激活”0 67.125⋮

对象的对象dlhdl。工作流班级。指定网络和比特流名称。指定已保存的预磨损量化trainedblemDetNet目的dlQuantObj随着网络。确保位流名称与您的目标数据类型和FPGA板匹配。在该示例中,目标FPGA板是Xilinx ZCU102 SoC板。比特流使用了int8数据类型。

hW = dlhdl。工作流(“网络”,dlquantobj,“比特流”,“zcu102_int8”,'目标'hT);

要编译量化网络,请运行dlhdl。工作流对象。

hW.compile (“InputFrameNumberLimit”, 30)

###编译网络深度学习FPGA原型…### FPGA bitstream zcu102_int8…###网络包括以下几层:1“imageinput”图像输入128×128×1图像“zerocenter”正常化(SW层)2的conv_1卷积20 5×5×1步[1]和填充的卷积[0 0 0 0](HW层)3的relu_1 ReLU ReLU (HW层)4“maxpool_1”马克斯池2×2马克斯池步(2 - 2)和填充[0 0 0 0](HW层)5 crossnorm横通道正常化交叉道归一化与5频道/元素(HW层)6的conv_2卷积20 5×5×20旋转步[1]和填充[0 0 0 0](HW层)7的relu_2 ReLU ReLU (HW层)8“maxpool_2”马克斯池2×2马克斯池步(2 - 2)和填充[0 0 0 0](HW层)9 fc_1完全连接512完全连接层(HW层)10 'fc_2' Fully Connected 2 fully connected layer (HW Layer) 11 'softmax' Softmax softmax (SW Layer) 12 'classoutput' Classification Output crossentropyex with classes 'ng' and 'ok' (SW Layer) 3 Memory Regions created. Skipping: imageinput Compiling leg: conv_1>>maxpool_2 ... Compiling leg: conv_1>>maxpool_2 ... complete. Compiling leg: fc_1>>fc_2 ... Compiling leg: fc_1>>fc_2 ... complete. Skipping: softmax Skipping: classoutput Creating Schedule... ......... Creating Schedule...complete. Creating Status Table... ........ Creating Status Table...complete. Emitting Schedule... ...... Emitting Schedule...complete. Emitting Status Table... .......... Emitting Status Table...complete. ### Allocating external memory buffers: offset_name offset_address allocated_space _______________________ ______________ ________________ "InputDataOffset" "0x00000000" "16.0 MB" "OutputResultOffset" "0x01000000" "4.0 MB" "SchedulerDataOffset" "0x01400000" "4.0 MB" "SystemBufferOffset" "0x01800000" "28.0 MB" "InstructionDataOffset" "0x03400000" "4.0 MB" "ConvWeightDataOffset" "0x03800000" "4.0 MB" "FCWeightDataOffset" "0x03c00000" "12.0 MB" "EndOffset" "0x04800000" "Total: 72.0 MB" ### Network compilation complete.

ans =结构体字段:[1×1 struct]注册:[1×1 struct] syncstructions: [1×1 struct]

当需要在Xilinx ZCU102 SoC硬件上部署网络时,需要运行Xilinx的deploy功能dlhdl。工作流对象。该函数使用compile函数的输出,利用编程文件对FPGA板进行编程。它还下载了网络权重和偏差。deploy函数开始对FPGA设备进行编程,并显示进度消息和部署网络所需的时间。

hW.deploy

###使用以太网编程FPGA Bitstream…下载目标FPGA设备配置通过以太网到SD卡…#将/tmp/hdlcoder_rd拷贝到/mnt/hdlcoder_rd。bit to /mnt/hdlcoder_rd #设置Bitstream为hdlcoder_rd/hdlcoder_system。#复制devicetree_dlhdl. bit #复制devicetree_dlhdl. bit #复制devicetree_dlhdl。dtb为/mnt/hdlcoder_rd #设置Devicetree为hdlcoder_rd/devicetree_dlhdl。dtb # Set boot for Reference Design: ' axis - stream DDR Memory Access: 3-AXIM'现在系统将重新启动以使持久更改生效。系统正在重新启动。

. . . . .### FPGA位流编程已成功完成###加载权值到Conv处理器。### Conv权重加载。###正在加载FC处理器的权重。### FC权重已加载。当前时间是2020年12月16日16:18:03

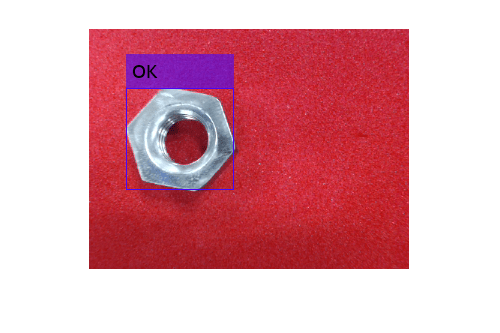

从附件中加载图像testImages文件夹并调整图像大小以匹配网络图像输入层尺寸。运行预测功能dlhdl。工作流对象从FPGA中检索和显示缺陷预测。

wi = uint32 (320);他= uint32 (240);ch = uint32 (3);文件名= fullfile (pwd,“ok1.png”);img = imread(文件名);Img = imresize(Img,[他,wi]);img = mat2ocv (img);%提取ROI进行预处理[Iori, imgpack, num, bbox] = myNDNet_Preprocess(img); / /上传数据%行主视图>列主视图转换imgPacked2=零([128128,4],“uint8”);对于c = 1:4对于i = 1:128对于j = 1:128 imgPacked2 (i, j c) = imgPacked((张)* 128 + (j - 1) +(颈- 1)* 128 * 128 + 1);结束结束结束%分类检测到的螺母使用CNN分数=零(2,4);对于i=1:num[分数(:,i),速度]=hW.predict(单个(imgPacked2(:,:,i)),'轮廓',“开”);结束

###已完成输入激活的编写。####运行单输入激活。深度学习处理器探查器性能结果LastFrameLatency(周期)LastFrameLatency(秒)FRAMESUM总延迟帧/秒------------------------------网络1754969 0.00798 1 1754969 125.4 conv_1 271340 0.00123 maxpool_1 87533 0.00040交叉范数125737 0.00057 conv_2 149972 0.00068 maxpool_2 19657 0.00009 fc_1 1085683 0.00493 fc_2 14928 0.00007*DL处理器的时钟频率为:220MHz

Iori =重塑(Iori,[1,他*wi*ch]);Bbox =重塑(Bbox, [1,16]);Scores =重塑(Scores, [1,8]);%插入用于后处理的注释Out = MyNDNet_PostProcess(IORI,Num,Bbox,Scors,Wi,He,Ch);sz = [他wi ch];出= ocv2mat(出,sz);imshow(出)

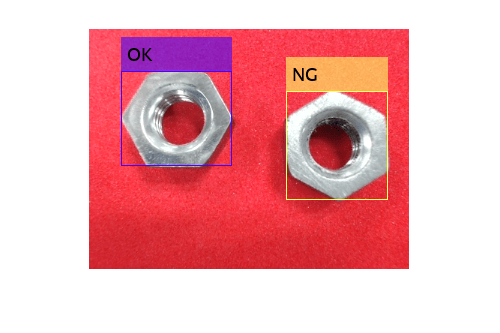

为了测试量化网络可以识别所有测试用例部署附加图像,调整图像大小以匹配网络图像输入层维度,并运行预测功能dlhdl。工作流对象从FPGA中检索和显示缺陷预测。

wi = uint32 (320);他= uint32 (240);ch = uint32 (3);文件名= fullfile (pwd,“okng.png”);img = imread(文件名);Img = imresize(Img,[他,wi]);img = mat2ocv (img);%提取ROI进行预处理[Iori, imgpack, num, bbox] = myNDNet_Preprocess(img); / /上传数据%行主视图>列主视图转换imgPacked2=零([128128,4],“uint8”);对于c = 1:4对于i = 1:128对于j = 1:128 imgPacked2 (i, j c) = imgPacked((张)* 128 + (j - 1) +(颈- 1)* 128 * 128 + 1);结束结束结束%分类检测到的螺母使用CNN分数=零(2,4);对于i=1:num[分数(:,i),速度]=hW.predict(单个(imgPacked2(:,:,i)),'轮廓',“开”);结束

###完成写入输入激活。###运行单输入激活。深度学习处理器Profiler性能结果LastFrameLatency(cycles) LastFrameLatency(seconds) FramesNum Total Latency Frames/s ------------- ------------- --------- --------- --------- Network 1754614 0.00798 1 1754614 125.4 conv_1 271184 0.00123 maxpool_1 87557 0.00040 crossnorm 125768 0.00057 conv_2 149819 0.00068 maxpool_2 196020.00009 fc_1 1085664 0.00493 fc_2 14930 0.00007 * DL处理器的时钟频率为:220MHz ###完成写入输入激活###运行单输入激活。Deep Learning Processor Profiler Performance Results LastFrameLatency(cycles) LastFrameLatency(seconds) FramesNum Total Latency Frames/s ------------- ------------- --------- --------- --------- Network 1754486 0.00797 1 1754486 125.4 conv_1 271014 0.00123 maxpool_1 87662 0.00040 crossnorm 125835 0.00057 conv_2 149789 0.00068 maxpool_2 19661 . maxpool_2的性能数据如下0.00009 fc_1 1085505 0.00493 fc_2 14930 0.00007 * DL处理器的时钟频率为:220MHz

Iori =重塑(Iori,[1,他*wi*ch]);Bbox =重塑(Bbox, [1,16]);Scores =重塑(Scores, [1,8]);%插入用于后处理的注释Out = MyNDNet_PostProcess(IORI,Num,Bbox,Scors,Wi,He,Ch);sz = [他wi ch];出= ocv2mat(出,sz);imshow(出)

量化网络从每秒45帧到125帧的性能将性能提高到125帧,并将部署的网络大小从88 MB降至72 MB。