可视化多信号的一种逻辑分析仪

通过使用逻辑分析器可视化的可编程FIR滤波器的多个信号。有关在这个例子中,以及如何使用该模型配置为生成HDL代码模型的更多信息,请参阅生成HDL代码可编程FIR滤波器。

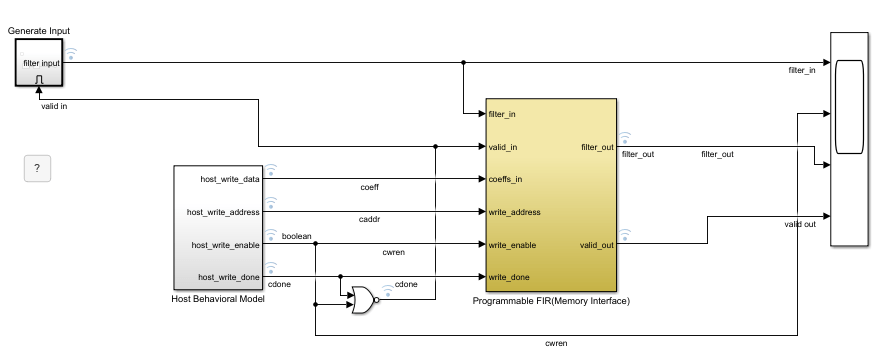

型号可编程FIR滤波器

打开示例模型。

MODELNAME ='dspprogfirhdl';open_system(MODELNAME);

考虑两个FIR滤波器,一个具有低通响应和其他与高通响应。系数可以利用来指定InitFcn *回调函数。要指定回调,选择文件>模型属性>模型属性。在该对话框中,在回调选项卡,选中InitFcn *。

该通过寄存器可编程FIR块加载来自低通系数主机行为模型块和第一处理输入线性调频脉冲的样品。块然后加载高通系数和重新处理相同的线性调频脉冲的样本。

打开通过寄存器可编程FIR块。

系统名称= [MODELNAME“经由寄存器/可编程FIR”]。open_system(系统名称);

模拟

运行示例模型。

SIM(MODELNAME)

打开的范围。

open_system([MODELNAME'/范围']);

比较DUT(测试下的设计)输出与参考输出。

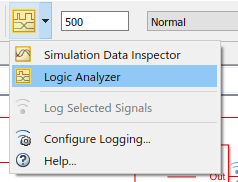

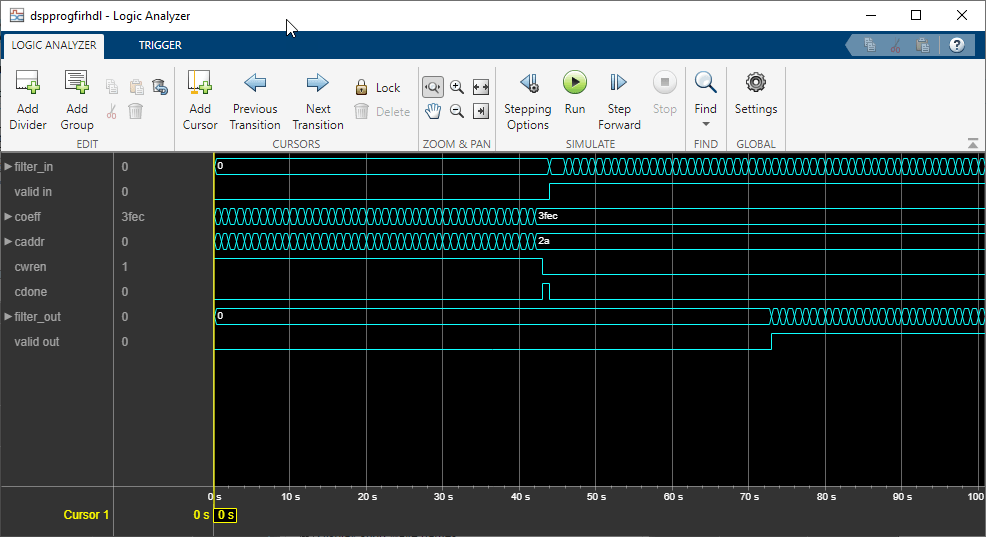

使用逻辑分析仪

逻辑分析仪使你在一个窗口,以查看多个信号。它也可以很容易地检测到的信号转换。

感兴趣的信号(输入系数,写地址,写使能,写完成的,在过滤器,滤出,参考输出和错误)已经被标记为在模型中的流。点击工具栏上的流式按钮,然后选择逻辑分析仪。

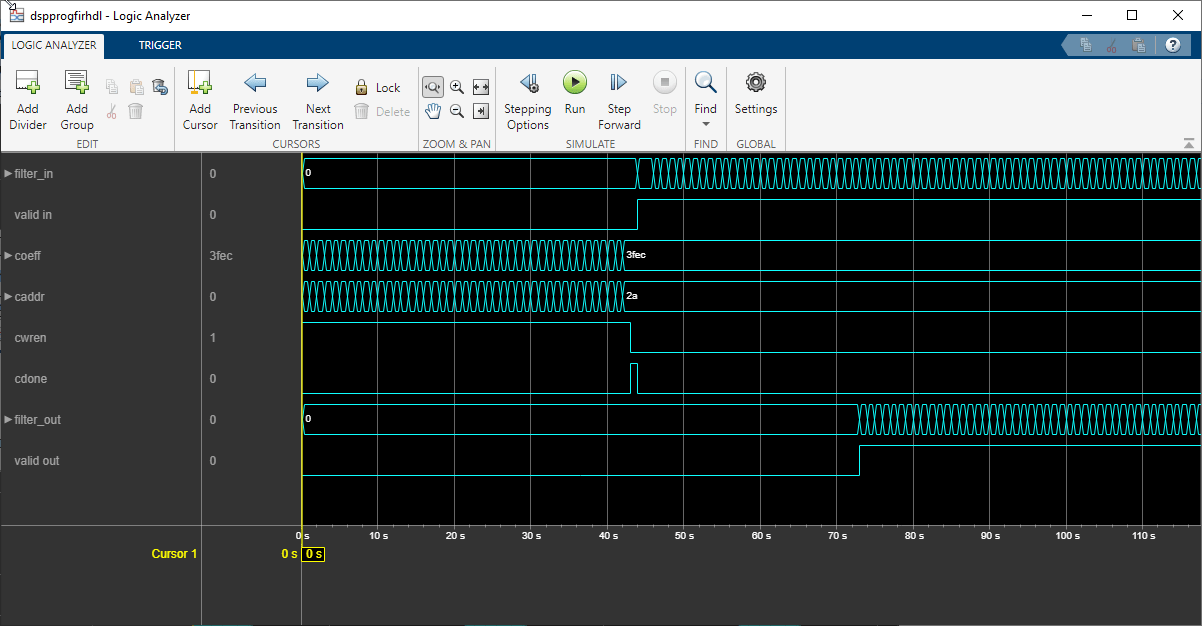

逻辑分析仪显示器波形所选择的信号的。

修改显示

在逻辑分析仪,可以修改显示的所有通道的高度,并在信道之间的间距。点击设置按钮。然后,修改每个波默认高度和间距。请点击应用显示在后台新的层面。

要放大波形,请点击放大时间按钮,在缩放和平移工具栏的部分。你的光标会变成一个放大镜。然后单击并拖动来选择对波形的区域。

逻辑分析仪现在显示您所选择的时间跨度。

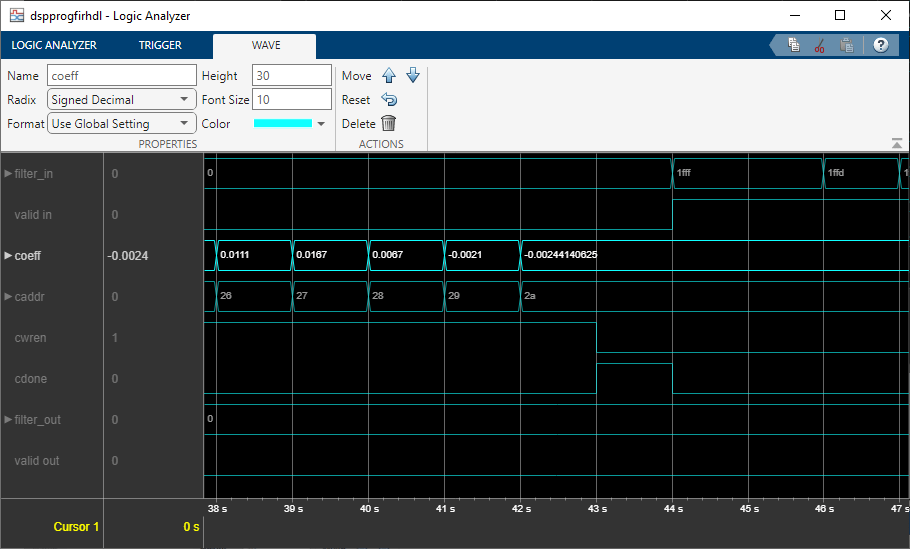

您也可以控制在每个波形的基础上显示。要修改个人波形,双击信号,选择信号,然后点击波标签来修改其设置。

显示CoeffIn在符号十进制模信号。该转换使用小数和整数位作为用于在模型中该信号定义。

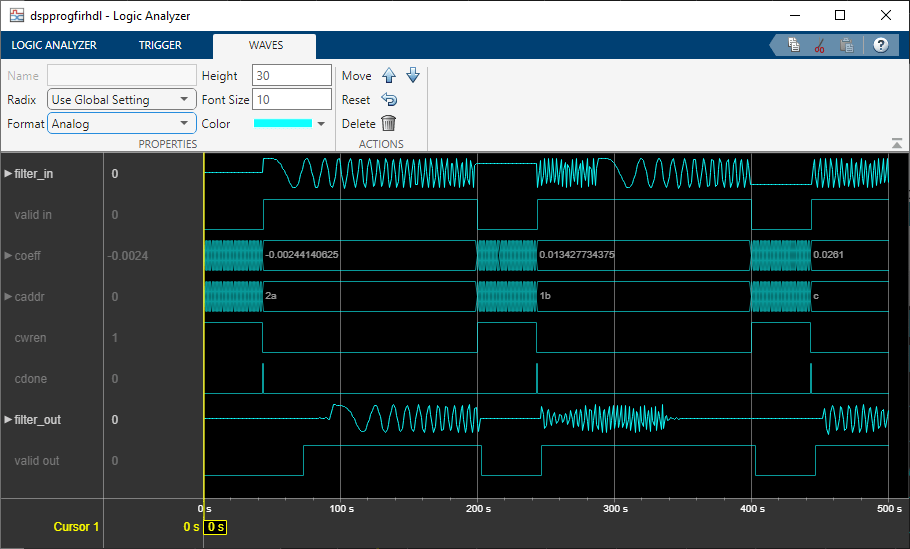

在逻辑分析仪的可视化的另一种有用的模式是模拟格式。观看过滤器在,过滤掉和参考输出模拟格式的信号。

您也可以分隔添加到显示。点击添加分频器按钮在工具栏中。

然后在你的分隔指定一个名称除法标签。添加第二个分频器。除法器在所选择的波下方加入。如果没有选择波,它在显示器的底部加入。要移动护栏,点击分隔的名字,并将其拖动到新的位置。或者,使用移动上的箭头除法标签。

注意:在新的位置的分隔符。

有关使用波形显示工具的详细说明,请参阅逻辑分析仪。