基于MATLAB的基本HDL代码生成和FPGA合成

这个例子展示了如何创建HDL Coder™项目,为您的MATLAB®设计生成代码,并合成HDL代码。在这个例子中,你:

创建一个MATLAB HDL编码器项目。

将设计和测试工作台文件添加到项目中。

启动HDL工作流顾问的MATLAB设计。

运行定点转换和HDL代码生成。

从MATLAB测试台生成HDL测试台。

使用HDL模拟器验证生成的HDL代码。本例使用ModelSim®作为工具。

使用合成工具合成生成的HDL代码。本例使用Xilinx®Vivado®作为工具。

FIR滤波器MATLAB设计

MATLAB设计mlhdlc_sfir是一个简单的对称FIR滤波器。

design_name =“mlhdlc_sfir”;testbench_name =“mlhdlc_sfir_tb”;

回顾MATLAB设计。

打开(design_name);

%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%MATLAB设计:对称FIR滤波器%%的介绍:%我们可以通过利用它的对称性来降低FIR滤波器的复杂性。n-tap滤波器的对称性意味着系数h0 =系数hn-1,%系数,h1 =系数hn-2,等等。在这种情况下,的数量%乘数可以大约减半。关键是要加%两个需要乘以相同系数的数据值%之前执行乘法。%本例中包含的键设计模式:%(1)过滤使用持久变量表示的状态%(2)作为参数传入的过滤器系数版权所有The MathWorks, Inc.% # codegen函数[y_out, delayed_xout] = mlhdlc_sfir(x_in,h_in1,h_in2,h_in3,h_in4)%对称FIR滤波器%声明和初始化延迟寄存器持续的Ud1 ud2 ud3 ud4 ud5 ud6 ud7 ud8;如果Isempty (ud1) ud1 = 0;Ud2 = 0;Ud3 = 0;Ud4 = 0;Ud5 = 0;Ud6 = 0;Ud7 = 0;Ud8 = 0;结束访问状态/寄存器的前一个值A1 = ud1 + ud8;A2 = ud2 + ud7;A3 = ud3 + ud6;A4 = ud4 + ud5;%乘数链M1 = h_in1 * a1;M2 = h_in2 * a2;M3 = h_in3 * a3;M4 = h_in4 * a4;%加法器链A5 = m1 + m2;A6 = m3 + m4;过滤输出百分比Y_out = a5 + a6;%延时输入信号Delayed_xout = ud8;%更新延迟线Ud8 = ud7;Ud7 = ud6;Ud6 = ud5;Ud5 = ud4;Ud4 = ud3;Ud3 = ud2;Ud2 = ud1;Ud1 = x_in;结束

FIR滤波器MATLAB测试台

MATLAB测试台mlhdlc_sfir_tb通过使用代表性的输入范围来练习过滤器设计。复习MATLAB测试台mlhdlc_sfir_tb.

打开(testbench_name);

%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%MATLAB的FIR滤波器测试台%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%版权所有The MathWorks, Inc.清晰的mlhdlc_sfir;T = 2;Dt = 0.001;N = T/dt+1;sample_time = 0:dt:T;Df = 1/dt;sample_freq = linspace(-1/2,1/2,N).*df;%带噪声的输入信号x_in = cos(2。*π。* (sample_time)。* (1 + (sample_time)。* 75))。”;%滤波系数H1 = -0.1339;H2 = -0.0838;H3 = 0.2026;H4 = 0.4064;Len = length(x_in);Y_out = 0 (1,len);X_out = 0 (1,len);为Ii =1:len data = x_in(Ii);调用针对硬件的设计'mlhdlc_sfir'[y_out (ii), x_out (ii)] = mlhdlc_sfir(数据,h1, h2, h3, h4);结束图(“名字”(mfilename“_plot”]);次要情节(1,1);阴谋(1:len x_in,“- b”);包含(“时间(ms)”) ylabel (“振幅”)标题(“输入信号(带噪声)”)次要情节(3、1、2);阴谋(1:len y_out,“- b”);包含(“时间(ms)”) ylabel (“振幅”)标题(输出信号(过滤后)) freq_fft = @(x) abs(fftshift(fft(x)));次要情节(3,1,3);semilogy (sample_freq freq_fft (x_in),“- b”);持有在semilogy (sample_freq freq_fft (y_out),“- r”)举行从包含(的频率(赫兹)) ylabel (“振幅(dB)”)标题(输入和输出信号(频域))({传奇“FilterIn”,“FilterOut”},“位置”,“南”)轴([-500 500 1 100])

测试原始MATLAB算法

为了避免运行时错误,请使用测试台模拟设计。

mlhdlc_sfir_tb

创建一个文件夹并复制相关文件

要将示例文件复制到临时文件夹,运行这些命令:

design_name =“mlhdlc_sfir”;testbench_name =“mlhdlc_sfir_tb”;

创建一个临时文件夹

Mlhdlc_demo_dir = fullfile(matlabroot,“工具箱”,“hdlcoder”,“hdlcoderdemos”,“matlabhdlcoderdemos”);Mlhdlc_temp_dir = [tempdir . txt]“mlhdlc_sfir”];cd (tempdir);[~, ~, ~] = rmdir(mlhdlc_temp_dir,“年代”);mkdir (mlhdlc_temp_dir);cd (mlhdlc_temp_dir);

复制MATLAB文件。

拷贝文件(fullfile (mlhdlc_demo_dir design_name,“m *”]), mlhdlc_temp_dir);拷贝文件(fullfile (mlhdlc_demo_dir testbench_name,“m *”]), mlhdlc_temp_dir);

设置HDL模拟器和合成工具路径

如果要合成生成的HDL代码,在使用HDL Coder生成代码之前,请设置合成工具路径。要设置合成工具的路径,请使用hdlsetuptoolpath函数。例如,如果你的合成工具是Xilinx Vivado:

hdlsetuptoolpath (“ToolName”,“Xilinx Vivado”,“路径”,...“C: \ Xilinx \ Vivado \ 2018.3 \ bin \ vivado.bat ');

您必须已经安装了Xilinx Vivado。要检查Xilinx Vivado合成工具的设置,运行以下命令启动工具:

vivado !

如果您想通过使用HDL测试台来模拟生成的HDL代码,您可以使用HDL模拟器,例如ModelSim®。您必须已经安装了HDL模拟器。

创建一个HDL编码器项目

创建一个HDL Coder项目:

1.运行命令创建一个项目:

编码器-hdlcoder不管是新sfir_project

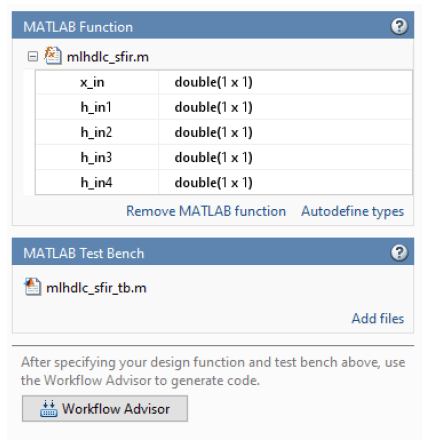

2.为MATLAB函数,添加MATLAB设计mlhdlc_sfir.添加mlhdlc_sfir_tb.m作为MATLAB测试台。

3.点击Autodefine类型并使用推荐的类型进行MATLAB设计。代码生成器通过运行测试平台来推断数据类型。

创建算法和测试台的定点版本

单击工作流的顾问按钮以打开Workflow Advisor。你可以看到定义输入类型任务已经完成。

运行定点转换的任务。的定点转换工具在右侧窗格中打开。

在运行定点转换时,为浮点数据类型建议分数长度,HDL Coder使用默认字长.在本教程中,默认字长是14.该顾问提供了一个默认值模拟安全裕度最小/最大的0%.该顾问根据这个安全系数调整数据的范围。例如,值4指定您希望的范围至少为4更大的百分比。另请参阅浮点到定点转换.

选择代码生成选项和生成HDL代码

在生成HDL代码之前,如果希望将代码部署到目标平台上,请指定合成工具。在代码生成目标任务,离开工作流来通用ASIC / FPGA并指定Xilinx Vivado随着合成工具.如果没有看到合成工具,请单击刷新列表.运行此任务。

在HDL代码生成任务中,通过使用此任务右侧的选项卡,可以指定其他代码生成选项。

默认情况下,HDL Coder生成VHDL®代码。要生成Verilog代码,请在目标选项卡中,选择

Verilog随着语言.要生成带有注释和可追溯性链接的代码生成报告,请使用编码风格选项卡上,选择包括MATLAB源代码作为注释和“生成报告”。

为了优化您的设计,您可以使用分布式流水线优化。在优化选项卡中,指定

1为输入管道而且输出管道然后选择分发管道寄存器.要了解更多信息,请参见分布式流水线.点击运行来生成Verilog代码。

检查日志窗口并单击链接以查看生成的代码和报告。

生成HDL测试台并模拟生成的代码

HDL Coder生成HDL测试台,使用HDL模拟器运行HDL测试台,验证HDL仿真与MATLAB定点仿真的数值和时延是否匹配。

生成HDL测试台并模拟生成的代码,在HDL验证>用HDL测试台验证任务:

在输出设置选项卡上,选择生成HDL测试台.

要模拟生成的测试台架,请设置仿真工具来

ModelSim.您必须已经安装了ModelSim。中指定在单独文件中生成HDL测试台代码和测试台数据测试台选项选项卡上,选择多文件测试台.

单击运行按钮。

该任务生成HDL测试台,然后使用选定的仿真工具对定点设计进行仿真,并生成编译报告和仿真报告。

合成生成的HDL代码

HDL Coder合成目标平台上的HDL代码,并根据您指定的目标设备为您的设计生成区域和定时报告。

合成生成的HDL代码:

1.运行创建项目的任务。

该任务为HDL代码创建Xilinx Vivado合成项目。HDL Coder在下一个任务中使用这个项目进行综合设计。

2.选择并运行运行合成的任务。

该任务在后台启动合成工具,打开合成项目,编译HDL代码,合成设计,并生成网络列表和面积和时间报告。

3.选择并运行运行实现的任务。

此任务在后台启动综合工具,在设计中运行位置和路线,并生成路线前和路线后计时信息,用于关键路径分析和源模型的反向注释。

清理生成的文件

要清理临时工程文件夹,运行这些命令:

Mlhdlc_demo_dir = fullfile(matlabroot,“工具箱”,“hdlcoder”,“hdlcoderdemos”,“matlabhdlcoderdemos”);Mlhdlc_temp_dir = [tempdir . txt]“mlhdlc_sfir”];清晰的墨西哥人;cd (mlhdlc_demo_dir);删除目录(mlhdlc_temp_dir“年代”);