Get Started withHDL Coder

HDL Coder™ generates portable, synthesizable VHDL®and Verilog®code from MATLAB®functions, Simulink®models, and Stateflow®charts. The generated HDL code can be used for FPGA programming or ASIC prototyping and design.

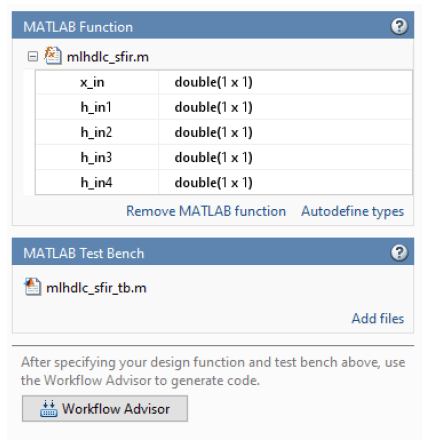

HDL Coder provides a workflow advisor that automates the programming of Xilinx®, Microsemi®, and Intel®FPGAs. You can control HDL architecture and implementation, highlight critical paths, and generate hardware resource utilization estimates. HDL Coder provides traceability between your Simulink model and the generated Verilog and VHDL code, enabling code verification for high-integrity applications adhering to DO-254 and other standards.

Support for industry standards is available throughIEC Certification Kit(for ISO 26262 and IEC 61508).

Tutorials

- Create HDL-Compatible Simulink Model

Create a model and check compatibility for HDL code generation.

- Generate HDL Code from Simulink Model

从模型生成硬件描述语言(VHDL)和Verilog代码模型万博1manbetxs.

- Verify Generated HDL Code from Simulink Model

Generate an HDL test bench to verify the VHDL or Verilog Code.

- HDL Code Generation and FPGA Synthesis from Simulink Model

Generate code and synthesize your Simulink design on the target FPGA.

About HDL Code Generation

- Basic HDL Code Generation Workflow

Workflow for HDL code generation and FPGA synthesis from MATLAB and Simulink algorithms.

- Generation of Clock Bundle Signals in HDL Coder

How HDL Coder generates clock, reset, and clock enable signals in the HDL code.

Featured Examples

Videos

HDL Coder Overview

Generate VHDL and Verilog code for FPGA and ASIC designs using HDL Coder

Using Simulink to Deploy a MATLAB Algorithm on an FPGA or ASIC

Learn how to take a MATLAB DSP algorithm through Simulink, Fixed-Point Designer™, and HDL Coder, and target an FPGA or ASIC