从Simulink模型生成HDL代码万博1manbetx

这个例子展示了如何在Simulink中为一个简单的计数器模型生成HDL代码万博1manbetx®.该模型与HDL代码生成兼容。要创建此计数器模型,请参见创建兼容hdl的Simulink模型万博1manbetx.

HDL代码生成的模型

您可以创建自己的hdl兼容模型,如计数器模型或选择:

HDL编码器™示例模型可用

hdlcoderdemos.文件夹。cd (fullfile (matlabroot,“工具箱”那'hdlcoder'那'hdlcoderdemos'))

Matlab上有这些模型®小路。例如,您可以选择对称性冷杉滤波器模型.要使用该模型,请输入:

sfir_fixed.

万博1manbetx用于HDL代码生成的Simulink模板。您可以使用模板来模拟寄存器,ROM,基本算术运算,复杂乘法器,SHIFT寄存器等。

要选择模板,请在MATLAB ToolStrip上单击

按钮,然后导航到高密度脂蛋白编码器部分。看使用Si万博1manbetxmulink模板进行HDL代码生成.

按钮,然后导航到高密度脂蛋白编码器部分。看使用Si万博1manbetxmulink模板进行HDL代码生成.

在生成HDL代码之前,可以使用HDL代码advisor检查和更新HDL兼容性的型号。看用HDL Code Advisor检查Simulink万博1manbetx模型的HDL兼容性.

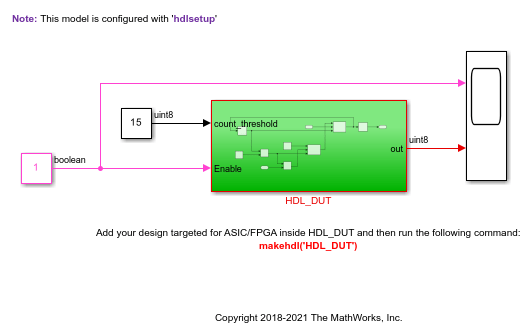

简单的计数模型

打开这个模型可以看到一个简单的计数器。该模型从零计算到一个阈值,然后再回退到零。设置阈值为15..要更改阈值,请将输入的值更改为count_threshold.港口。使能信号指定计数器是否向上计数或保存先前的值。价值1表示计数器连续计数。

生成HDL代码

对于计数器模型,hdl_dut.子系统是DUT。为DUT生成代码:

在应用选项卡上,选择高密度脂蛋白编码器.

在模型中选择DUT子系统,并确保这一点子系统名称出现在代码选择在HDL代码选项卡。要记住选择,请固定此选项。点击生成HDL代码.

默认情况下,HDL Coder在目标中生成VHDL代码hdlsrc文件夹。

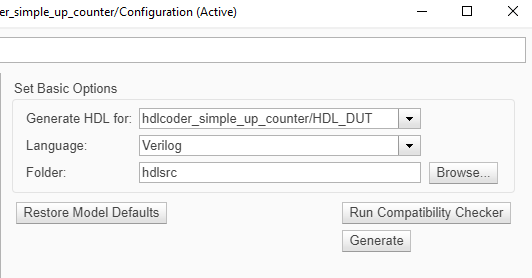

生成Verilog代码

要为计数器模型生成Verilog代码:

在HDL代码选项卡,单击设置.

在HDL代码生成窗格,for.语, 选择

verilog..点击申请然后点击产生.

HDL Coder在生成代码之前编译模型。根据模型显示选项(如端口数据类型),模型可以在代码生成后改变外观。随着代码生成的进行,HDL Coder会在MATLAB命令行中显示进度消息,并带有指向配置集和生成的文件的链接。要在MATLAB编辑器中查看文件,请单击链接。

该过程完成并显示消息:

### HDL代码生成完成。

查看HDL代码生成文件

一个文件夹图标hdlsrc文件夹出现在当前文件夹中。要查看生成的代码和脚本文件,请双击hdlsrc文件夹,然后双击与生成HDL代码的模型名称相同的文件夹。

HDL_DUT.vhd:VHDL.®包含实体定义和实现所设计计数器的RTL体系结构的代码。如果您生成Verilog代码,您将得到HDL_DUT.v文件。HDL_DUT_compile.do:导师图形®ModelSim®编译脚本。HDL_DUT_map.txt:映射文件,将在HDL代码中生成的实体或模块映射到生成它们的模型中的子系统。看使用映射文件的跟踪代码.HDL_DUT_report.html: HDL检查报告显示HDL代码生成状态和警告或消息。gm_hdlcoder_simple_up_counter.slx.:生成的模型,其行为表示Simulink建模环境中的HDL代码。万博1manbetx

HDL编码器创建一个称为的HDL代码的行为模型生成的模型.生成的型号名称与原始模型相同,并且具有前缀GM_.生成的模型对生成的HDL代码是位真和周期精确的。该模型显示了指定的块实现、速度和区域优化的效果。另请参阅HDL编码器中的速度和区域优化.

要为计数器打开生成的模型,请输入:

gm_hdlcoder_simple_up_counter.

对于计数器模型,由于禁用优化,生成的模型与原始模型相同。

检查生成的HDL代码

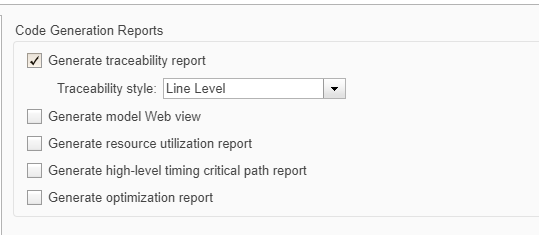

为了更容易地识别源模型和生成的HDL代码之间的映射,生成一个可跟踪性报告。使用报告从模型中的块导航到为该块生成的代码,并从代码导航到模型中的块。

要生成可追溯性报告:

在HDL代码选项卡,单击设置>报告选项.

在HDL代码生成>报告窗格,选择生成可追溯性报告,然后为此生成HDL代码

hdl_dut.子系统

生成代码后,将打开代码生成报告窗口。HDL编码器在中写入代码生成报告文件hdlsrc \ html \构建文件夹的文件夹。如果关闭报表,可以导航到此文件夹以重新打开报表。

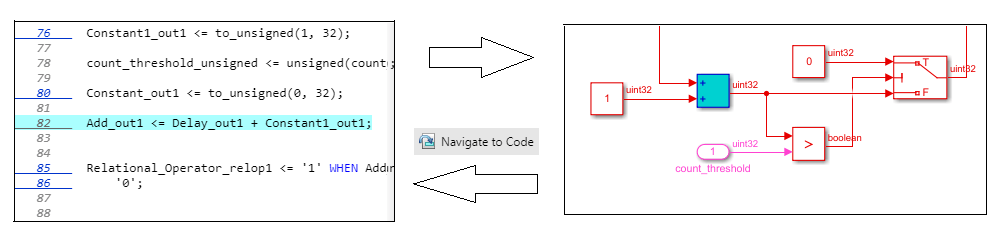

从HDL代码导航到模型:

在代码生成报告中,导航到可跟踪性报告部分,然后单击链接中的链接代码位置部分。

选择一个代码行的超链接,以突出显示模型中的相应块。

要从模型中的块导航到HDL代码,请选择该块,然后单击导航到代码按钮在审查结果部分HDL代码选项卡。

看使用可追溯性在Simulink模型万博1manbetx和HDL代码之间导航和创建和使用代码生成报告.

在生成的源文件节,如果单击HDL文件hdl_dut.,你看到了信号clk那重置,clk_enable.这些信号是时钟、复位和时钟使能信号,控制目标硬件上的触发器。HDL编码器在代码中根据顺序元素生成这些信号,如延迟您在模型中使用的块。看在HDL编码器中生成时钟束信号.

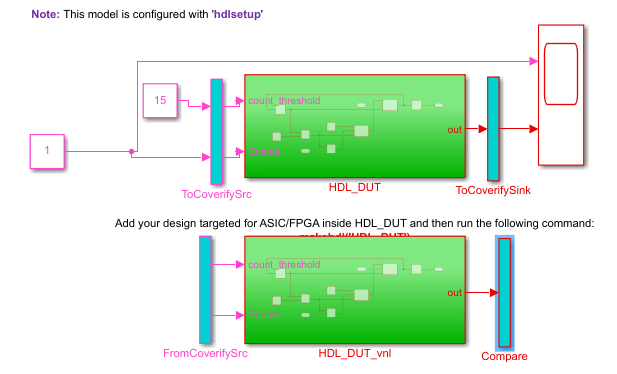

使用验证模型验证HDL行为

要使用原始模型验证HDL代码的行为模型,请生成验证模型。验证模型包含原始模型和生成的模型。它通过使用原始模型中提供的测试向量进行比较两种模型的输出。

要生成验证模型:

在HDL代码选项卡,单击设置.

在HDL代码生成>全局设置>模型生成选项卡上,选择验证模型,然后为此生成HDL代码

hdl_dut.子系统。

在代码生成日志中,您可以看到验证模型的链接。验证模型具有与生成的模型相同的前缀,并且还具有后缀_vnl.对于计数器模型,验证模型具有名称gm_hdlcoder_simple_up_counter_vnl.slx.您可以在与生成的模型相同的文件夹中找到此模型。要打开此模型,请输入:

gm_hdlcoder_simple_up_counter_vnl.

在模拟模型之后,双击比较子系统,然后在Assert_Out子系统。如果你打开范围块,你看到了犯错Signal的值为0,这意味着生成的模型输出与原始模型匹配。

验证生成的HDL代码

在目标硬件上部署设计之前,请验证生成的HDL代码。来自hdlsrc文件夹,导航到当前工作文件夹。看验证从Simulink模型生成的HDL代码万博1manbetx.

也可以看看

hdlset_param.|hdlsetup|makehdl