从仿真软件模型验证生成的HDL代码万博1manbetx

这个例子展示了如何生成一个高密度脂蛋白试验台并验证为一个简单的计数器模型生成的代码。为这个模型生成HDL代码,看看从仿真软件模型生成HDL代码万博1manbetx。如果你没有HDL代码生成模型,高密度脂蛋白编码器生成testbench之前™运行代码生成。

什么是高密度脂蛋白试验台?

验证DUT HDL代码的功能,生成一个高密度脂蛋白试验台。一个试验台包括:

刺激信号产生的数据源的数据连接到被测实体。

输出测试数据生成的实体。试验台运行期间,该数据相比,硬件描述语言(VHDL)的输出®模型验证。

时钟、复位和时钟使输入驱动被测实体。

在测试组件实例化的实体。

代码来驱动被测实体并比较其预期的输出数据。

你可以模拟生成的试验台,通过使用脚本文件导师图形®ModelSim®模拟器。

简单的计数模型

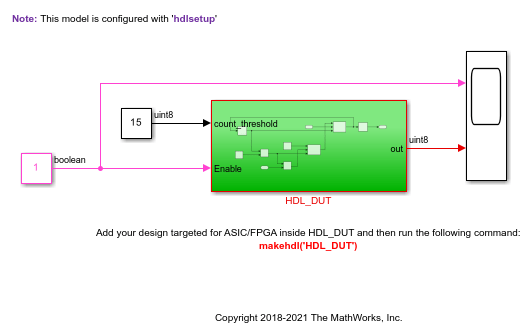

打开这个模型来看到一个简单的计数器。模型计算了从零到一个阈值,然后包裹回零。阈值设置为15。改变阈值,改变输入的值count_threshold端口。指定是否启用信号计数器计数向上或持有的前一个值。的值1表明柜台数量不断上升。

验证方法

如果你安装了HDL验证人™,你也可以验证生成的HDL代码通过使用这些方法。

| 验证方法 | 的更多信息 |

|---|---|

| 高密度脂蛋白Cosimulation | Cosimulation |

| SystemVerilog DPI试验台 | SystemVerilog DPI试验台 |

| FPGA-in-the-Loop | FPGA-in-the-Loop |

产生高密度脂蛋白试验台

生成硬件描述语言(VHDL)或Verilog®试验台代码适用。默认情况下,HDL代码和试验台代码写入相同的目标文件夹hdlsrc相对于当前文件夹。

反模式,HDL_DUTDUT子系统。生成testbench,选择这个子系统。

在应用程序选项卡上,选择高密度脂蛋白编码器。

选择DUT的子系统,

HDL_DUT,并确保这个名字出现在代码选择在HDL代码选项卡。记住选择,销此选项。点击生成Testbench。

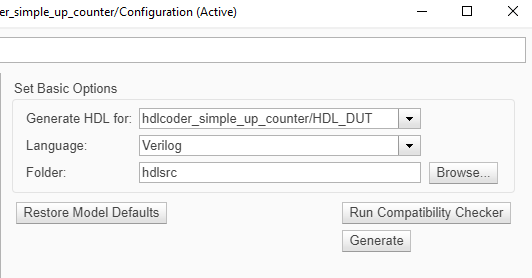

生成Verilog试验台的代码

生成Verilog testbench计数器的代码模型:

在HDL代码选项卡上,单击设置。

在HDL代码生成窗格中,为语言中,选择

Verilog。在HDL代码生成>试验台窗格中,单击生成测试工作台。

高密度脂蛋白编码器编译模型并生成试验台。

试验台一代完成并显示此消息。生成的文件中出现hdlsrc文件夹中。

# # # HDL TestBench代完成。

查看HDL试验台文件

反模式,hdlsrc文件夹包含这些试验台文件。

HDL_DUT_tb.vhd:硬件描述语言(VHDL)试验台代码包含生成的测试和输出数据。如果您生成Verilog试验台代码,生成的文件HDL_DUT_tb.v。HDL_DUT_tb_pkg.vhd:硬件描述语言(VHDL)试验台的包文件的代码。这个文件不是如果你指定的Verilog目标语言生成的。HDL_DUT_tb_compile.do:导师图形ModelSim编译脚本(威科姆公司命令)。这个脚本编译和加载实体进行测试(HDL_DUT.vhd)和试验台的代码(HDL_DUT_tb.vhd)。HDL_DUT_tb_sim.do:导师图形ModelSim脚本初始化模拟器,设置波窗口信号显示和运行一个模拟世界中。

查看生成的试验台在MATLAB代码®编辑器中,双击HDL_DUT_tb.vhd或HDL_DUT_tb.v文件在当前文件夹。

运行仿真和验证生成的HDL代码

为了验证仿真结果,您可以使用导师图形ModelSim模拟器。你必须已经安装了导师图形ModelSim。

打开模拟器,可以使用vsim(高密度脂蛋白校验)函数。这个命令显示了如何打开模拟器通过指定可执行文件的路径:

vsim (“vsimdir”,“C: \ Program Files \ ModelSim \ questasim \ 10.6 b \ win64 \ vsim.exe”)

编译和运行一个模拟生成的模型和试验台的代码,使用HDL编码器生成脚本。对于柜台模型,运行这些命令来编译和模拟试验台的生成HDL_DUT子系统。

打开导师图形ModelSim软件和导航到文件夹中,生成的代码文件和脚本。

使用生成的编译脚本编译和加载台代码生成模型和文本。为

HDL_DUT子系统,运行这个命令来编译生成的代码。QuestaSim >做HDL_DUT_tb_compile.do

使用生成的仿真脚本执行仿真。你可以忽略警告消息。为

HDL_DUT运行这个命令子系统,模拟生成的代码。QuestaSim >做HDL_DUT_tb_sim.do

模拟器优化你的设计和显示结果波窗口。如果你不看到仿真结果,打开波窗口。仿真脚本显示输入和输出模型中包括时钟、复位,时钟使信号波窗口。

你现在可以查看信号和验证仿真结果与最初设计的功能。验证后,关闭导师图形ModelSim模拟器,然后关闭在MATLAB编辑器中打开的文件。

目标设备上部署生成的HDL代码

部署在目标FPGA设备生成的代码,使用仿真软件万博1manbetx®高密度脂蛋白工作流顾问。看到从仿真软件模型HDL代码生成和FPGA合成万博1manbetx。