FPGA编程与配置

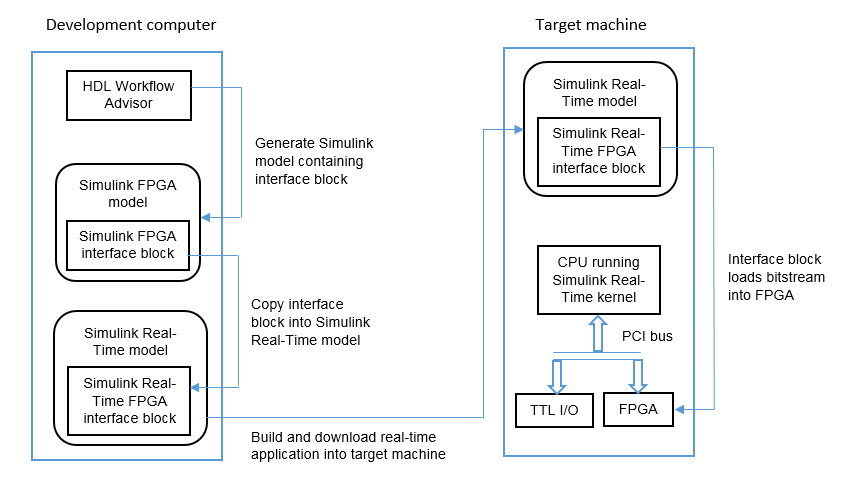

这个例子说明如何使用HDL的工作流程顾问实施上的Speedgoat FPGA万博1manbetx I / O板的Simulink算法:

指定一个FPGA板及其I/O接口。

合成Simulink的算法FP万博1manbetxGA编程。

生成的Simulink万博1manbetx实时™接口子系统模型。

该接口子系统模型包含块以对FPGA进行编程和实时应用程序执行过程中与FPGA I / O板通信。您所生成的子系统添加到您的Simulink实时域模型。万博1manbetx

整个工作流如图所示。

本例使用了Speedgoat IO331。您可以使用Simulink Real-Time和HDL编码器支持万博1manbetx的任何FPGA I/O模块万博1manbetx,以满足模型的速度、大小和输出要求。

要求和前提条件

HDL编码器™

在开始之前,请完成一个FPGA子系统计划。

对于IO331板,高密度脂蛋白工作流程顾问需要赛灵思ISE工具集。要安装此工具集,在命令窗口中,键入:

hdlsetuptoolpath('ToolName', 'Xilinx ISE', 'ToolPath',刀具路径)

哪里刀具路径是综合工具可执行文件的完整路径。

对于其他板的工具集的要求,请参阅支持第三方工具和硬件(HDL编码器)。万博1manbetx

步骤1. Sim万博1manbetxulink的域模型

Simu万博1manbetxlink FPGA域模型包含一个要在FPGA芯片上编程的子系统(算法)。使用此模型,您可以在将算法下载到FPGA板之前在模拟环境中测试FPGA算法。

创建包含要加载到F万博1manbetxPGA,在这种情况下,环回测试的算法的Simulink模型。

将要编程的算法放在一个子系统块内的FPGA上。该模型可以包含其他测试块和子系统。但是,一个子系统必须包含FPGA算法。

设置或确认子系统的输入端和输出端名称和数据类型。HDL Coder HDL Workflow Advisor使用这些设置将算法信号路由和映射到I/O连接器通道。

保存模型。

这种模式是你的FPGA领域模型。它代表着你的FPGA板上的时钟的模拟采样率。例如,的Speedgoat IO331具有板载125 MHz时钟。模拟一秒等于模型125e6迭代。

对于FPGA域模型的一个例子,请参见dslrtSGFPGAloopback_fpga。该伺服系统子系统包含FPGA算法。

步骤2. FPGA终端配置

此过程使用dslrtSGFPGAloopback_fpga例。您必须已经创建了在FPGA领域模型的FPGA子系统(算法),并开发了一个FPGA子系统的计划。

打开FPGA域模型

dslrtSGFPGAloopback_fpga。在FPGA模型中,右键单击FPGA子系统(

伺服系统)。从上下文菜单中选择HDL代码>HDL工作流顾问。该HDL流程顾问对话框显示几个任务子系统。地址只有你所需要的任务子集。扩大设置目标文件夹并选择任务1.1设定目标器件和合成工具。

组目标工作流程至

万博1manbetxSimulink的实时FPGA I / O。来自目标平台列表,选择安装在您的Speedgoat目标机器上的FPGA I/O板,在本例中为

Speedgoat IO331。检查HDL流程顾问设置综合工具赛灵思ISE设计套件。请点击运行此任务。

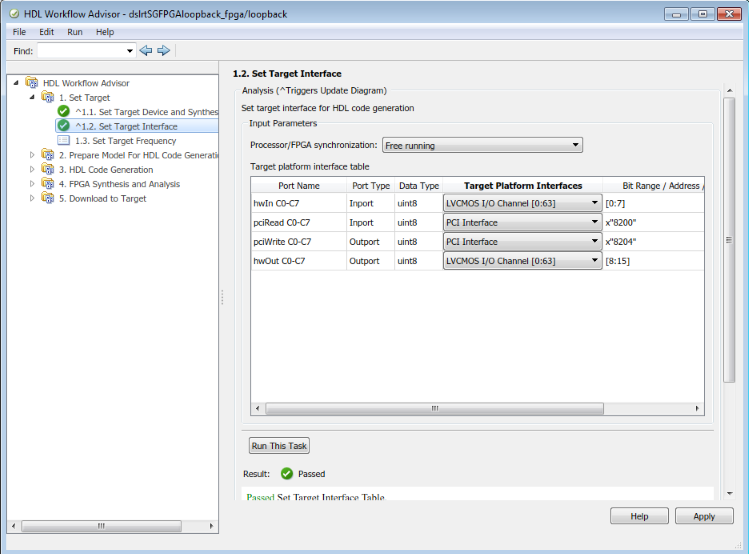

步骤3. FPGA目标接口配置

您必须已经配置的FPGA目标。

在里面设置目标文件夹,选择任务1.2设定目标界面。

在里面处理器/ FPGA同步中选择

自由奔跑。信号

赫温和hwOut, 在里面目标平台接口栏,选择LVCMOS I / O通道[0:63]。在里面位范围/地址/ FPGA引脚列,为每个信号输入通道值,或采用默认值。信号

pciRead和pciWrite, 在里面目标平台接口栏,选择PCI接口。在里面位范围/地址/ FPGA引脚列,使用自动生成的值。不输入PCI地址值。请点击运行此任务。

步骤4。FPGA目标频率配置

您必须已经配置的FPGA目标接口。

在里面设置目标文件夹,选择任务1.3设定目标频率(可选的)。该设定频率窗格包含表示FPGA输入时钟频率(固定)和FPGA系统时钟频率的字段。FPGA的系统时钟频率默认为FPGA的输入时钟频率。

指定一个不同的系统时钟频率(例如,50MHz的),在字段中键入新的值FPGA的系统时钟频率(MHz)。用于系统时钟率的允许范围,请参阅的Speedgoat板特性表。该系统集有时从你指定的值不同。

请点击运行此任务。

第5步。万博1manbetxSimulink实时接口子系统生成

这个过程为dxpcSGFPGAloopback_fpga示例生成一个接口子系统文件。

为包含不同HDL代码的块分配不同的名称。接口子系统文件的名称直接派生自块名称。如果包含不同HDL代码的两个块具有相同的名称,则名称将发生冲突,其中一个块将得到错误的代码。

您必须已经配置了FPGA目标接口和所需的目标频率。如果您已经指定了向量输入或输出,则您必须已经选择了Scalarize矢量端口复选框。此复选框上编码风格节点的标签全局设置,在节点HDL代码生成在配置参数对话框。

扩大下载到目标文件夹,并右击任务5.2生成Simulink万博1manbetx的实时接口。

在此窗格中单击运行到选定的任务。

这个动作:

运行剩余的任务。

创建于FPGA比特流文件

hdlsrc文件夹中。Simu万博1manbetxlink实时接口子系统在构建和下载过程中引用这个位流文件。生成一个名为

gm_dslrtSGFPGAloopback_fpga_slrt,其中包含了Simulink的实时接口子系万博1manbetx统。

这里是高密度脂蛋白HDL编码器工作流程顾问的这一行动之后的示例。

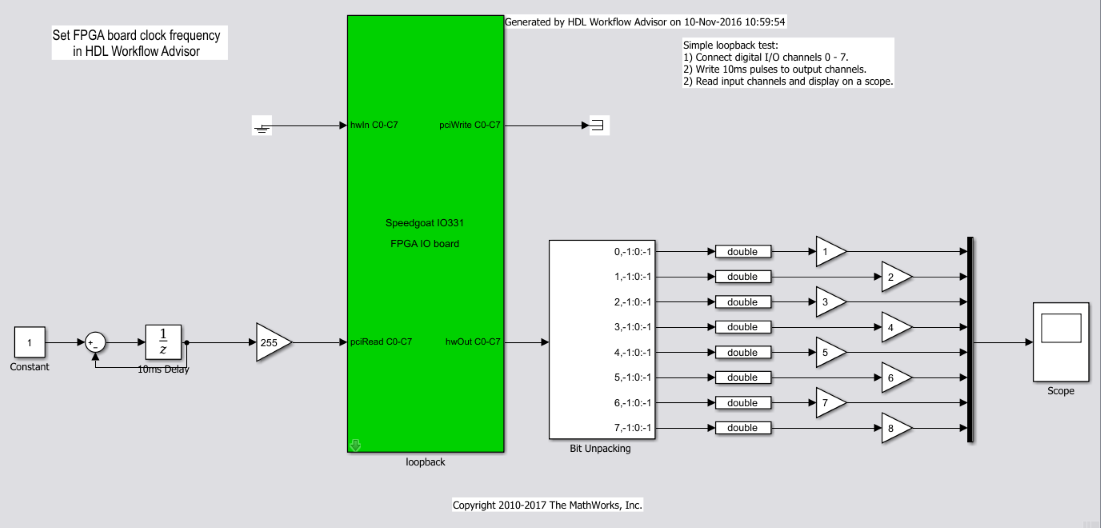

生成的接口子系统看起来像这个数字。

这个生成的模型包含具有相同的名称作为在Simulink FPGA域模型子系统掩蔽子系统。万博1manbetx虽然外观相似,该子系统不包含Simulink的算法。万博1manbetx相反,该算法在FPGA中实现的比特流。您参考和算法加载到从该子系统的FPGA。

第6步Simul万博1manbetxink的实时域模型

使用Simulink万博1manbetx的实时软件,变换的Simulink或Stateflow®域模型到Simulink实时域模型并执行它Speedgoat目标机,用于实时测试应用程序上。创建的Speedgoat FPGA接口子系统后。然后,您可以通过插入接口子系统包括在Simulink的实时域模型的FPGA板。万博1manbetx

使用要用FPGA算万博1manbetx法模拟的功能创建Simulink实时域模型。将FPGA子系统的输入端口和输出端口断开。

保存模型。

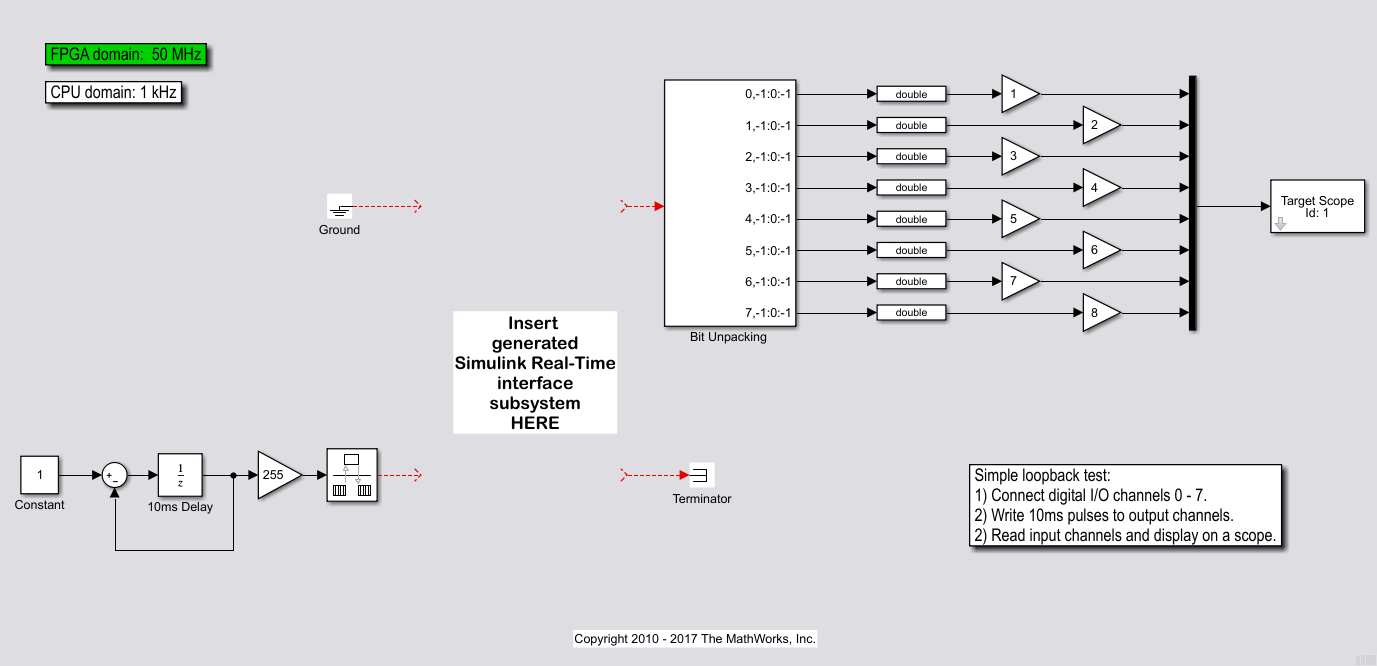

Simu万博1manbetxlink的实时域模型看起来这个数字。见例模型dslrtSGFPGAloopback_slrt。

步骤7。万博1manbetxSimulink实时接口子系统集成

在Simuli万博1manbetxnk实时接口子系统面具,设置三个参数:

设备索引

PCI插槽

采样时间

要集成接口子系统:

在Simuli万博1manbetxnk编辑器中,打开

gm_dslrtSGFPGAloopback_fpga_slrt。复制Simulin万博1manbetxk的实时接口子系统,并将其粘贴到Simulink的实时域模型。

保存或放弃

gm_dslrtSGFPGAloopback_fpga_slrt。您可以根据需要使用HDL Coder HDL Workflow Advisor重新创建它。在领域模型中,连接信号到接口子系统的inports和outports。

根据您的Speedgoat目标机器上的FPGA I/O板设置块参数。

如果您有一个FPGA I/O板,将设备索引和PCI插槽保留为默认值。您可以设置采样时间,也可以设置为

-1继承。如果你有多个FPGA I/O板,给每个板一个唯一的设备索引。

如果有相同类型的两个或更多个板(例如两个的Speedgoat IO331材),指定每个板上的PCI槽([总线,时隙])。获取与SimulinkRealTime.target.get万博1manbetxPCIInfo功能这一信息。

6保存模型。

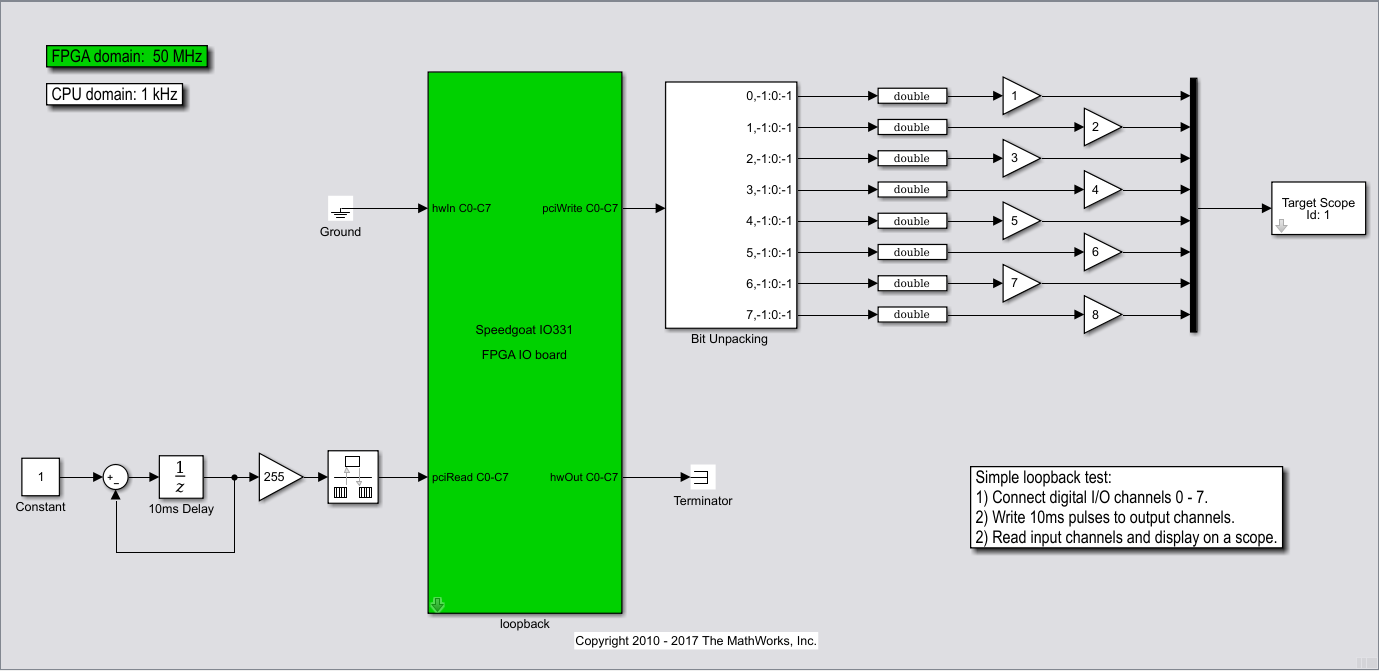

更新Simulink的实万博1manbetx时域模型看起来这个数字。见例模型dslrtSGFPGAloopback_slrt_wiss。

步骤8:实时应用程序执行

要执行此过程,您必须已经创建了一个Simulink实时域模型,该模型包括一个由HDL编码器HDL Workf万博1manbetxlow Advisor生成的Simulink实时接口子系统。

配置Speedgoat目标机器并将其连接到开发计算机。

建立和下载Simulink的实时应用。万博1manbetx实时应用程序加载到Speedgoat目标机,以及FPGA算法位流加载至FPGA。

如果您正在使用I/O线路(通道),请确认您已经将线路连接到正在测试的外部硬件。

Simulink的实时模型的启动和停止控制FPGA算万博1manbetx法的启动和停止。该FPGA算法执行在FPGA I / O板的时钟频率,同时根据与模型样品时的实时应用程序执行。