万博1manbetxReal-TimeFPGA I/O Modules

You can generate an FPGA programming file andSimulink Real-TimeFPGA I/O interface for deployment on a Speedgoat board. SeeIP Core Generation Workflow for Speedgoat Simulink-Programmable I/O Modules.

Classes

Functions

Topics

IP Core Generation Workflow for Speedgoat Simulink-Programmable I/O Modules

Use the IP Core Generation workflow with Speedgoat I/O modules and embed the IP core into the reference design.

Program Target FPGA Boards or SoC Devices

How to program the target Intel or Xilinx Hardware.

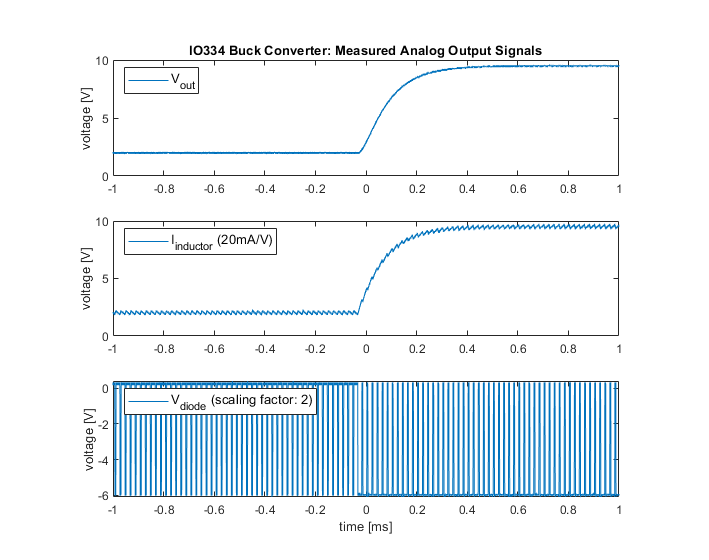

Generate Simulink Real-Time Interface Subsystem for Simscape Two-Level Converter Model

Generate HDL code and Simulink Real-Time interface model from Simscape™ models.

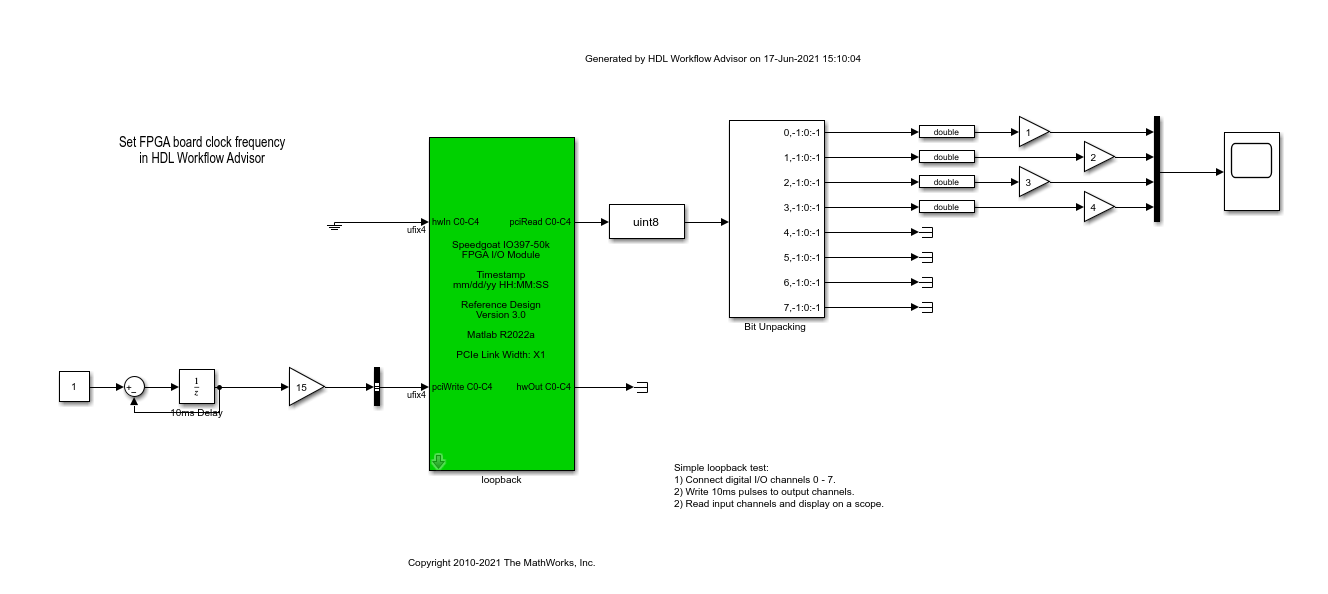

Speedgoat FPGA Support with HDL Workflow Advisor

Implementing Simulink algorithms on FPGAs on board Speedgoat FPGA I/O modules.

Related Information

Troubleshooting

Resolve Timing Failures in IP Core Generation and Simulink Real-Time FPGA I/O Workflows

Resolve timing failures in Build FPGA Bitstream step of IP Core Generation Workflow or Simulink Real-Time FPGA I/O Workflow for Vivado-Based Boards.